Xilinx VCU低延时方案和使用PS DP Live video接口来实现PS和PL的视频数据交换达到节约PL逻辑资源的目的

嵌入式技术

描述

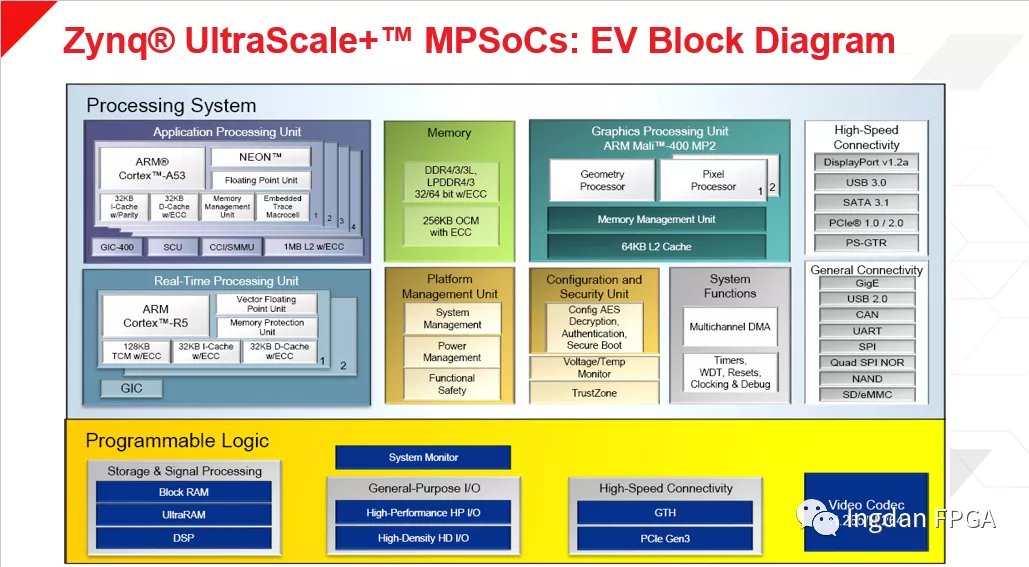

赛灵思推出首款真正的AllProgrammable(全可编程)异构多处理SoC—— ZynqUltraScale+MPSoC。采用台积公司(TSMC)新一代16nmFinFET工艺节点的ZynqUltraScale+MPSoC包含一个可扩展的32位或 64位多处理器CPU、用于实时处理图形和视频的专用硬化引擎、先进的高速外设,以及可编程逻辑,可用于汽车驾驶员辅助与安全、无线和有线通信、数据中心以及连接与控制等多种应用领域。

部分 ZynqUltraScale+MPSoC的可编程逻辑(PL)中包含最新的视频编码器/解码器。这种新型硬化编解码器能够访问来自PL 或PS的视频和音频流,以提供和/或存取达到软件算法50倍的压缩视频信息,从而节省宝贵的系统存储空间。

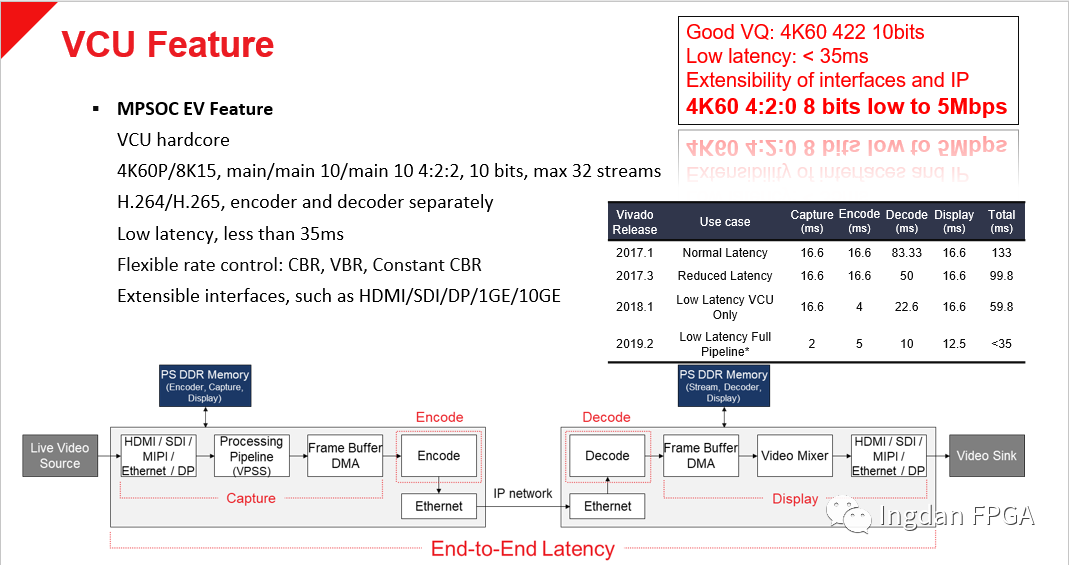

ZynqUltraScale+MPSoCVCU 的主要特性

· 支持H.264和H.265HEVC 视频标准

· 同步编码/解码

· 8Kx4K视频,15fps,或者4Kx2K视频,60fps

· 8位和10位色彩分量

· I、IP、IPB帧编码

· 4:2:0和4:2:2色度格式

Xilinx VCU低延时方案如下图所示,信号源从LiveVideo Source进入到MPSOC芯片,经过视频处理和Encode后通过网线传递给后端MPSOC,后端Decode后去到Video Sink显示;在整个End to End的视频链路上面 Latency最低可以做到小于35ms的性能。这个低延时特性可以用在KVM\内窥镜\无线图传等等领域。

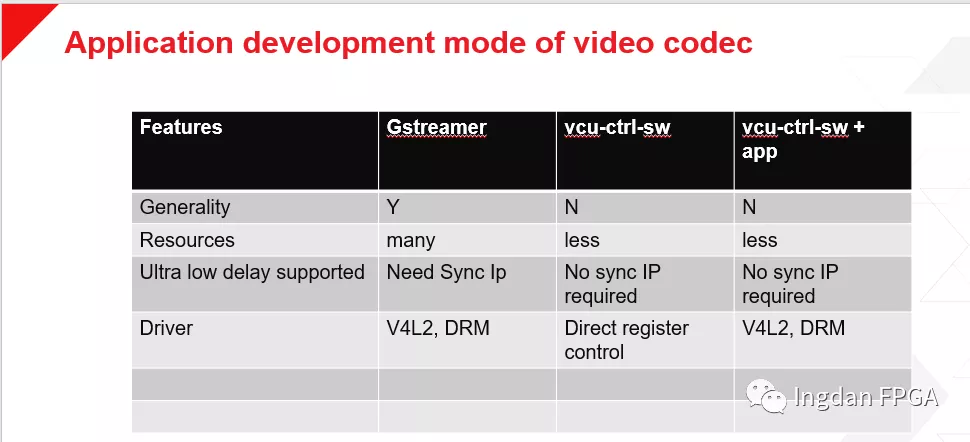

Xilinx实现低延时有两种方案,如图所示:第一种是在PS上面跑Gstreamer的软件架构加上PL的SyncIP,两个配合起来实现低延时设计;第二种方案是去掉PL的SyncIP,在PS里面跑VCU-CTRL-SW软件架构,在PS软件里面实现VCU的低延时设计。

在介绍完Xilinx VCU低延时方案后我们来聊聊如何实现使用PS DP现有的Live Video In\Out接口来代替DMA来进行PS和PL之间的视频数据互传。

从UG1250的VCU TRD可以看到整个设计框架,视频接入和输出要想跟PS进行交换数据时候都会用到DMA等等模块,对于ZU4EV器件来说PL资源是有限并且宝贵的;所以为了把宝贵的逻辑资源用于客户自己的算法,我们整个设计里面可以使用Livevideo in接口把PL的视频信号接入到PS,也可以使用LiveVideo Out接口把PS的视频数据传输到PL去做显示。利用这种巧妙的设计来满足性能和资源要求。

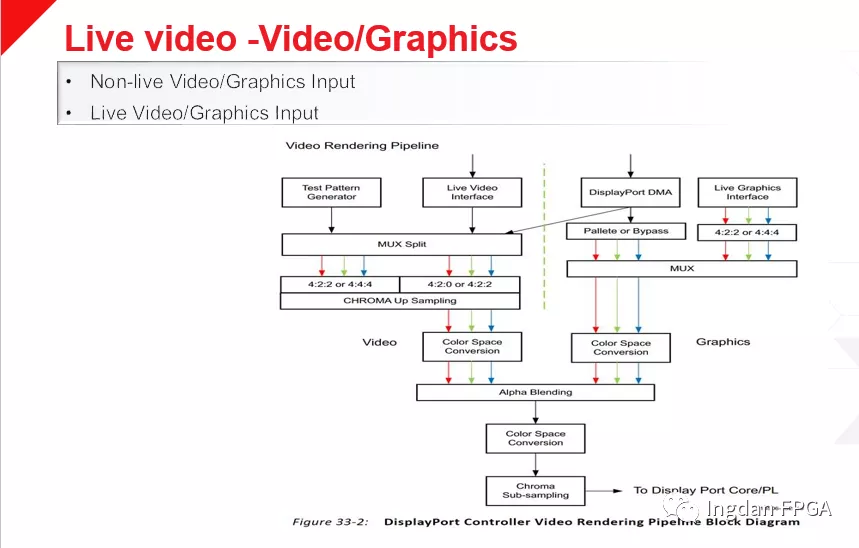

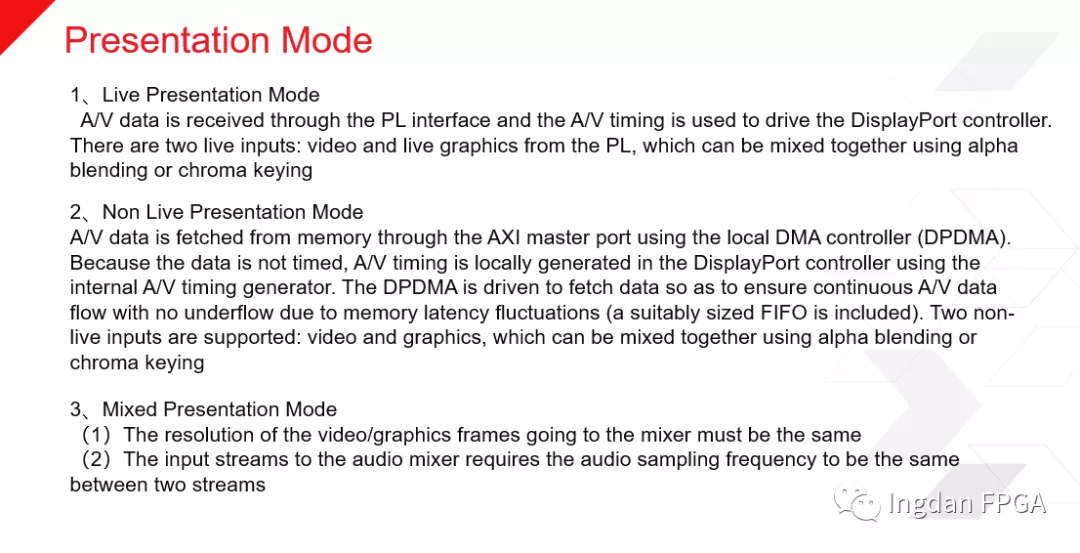

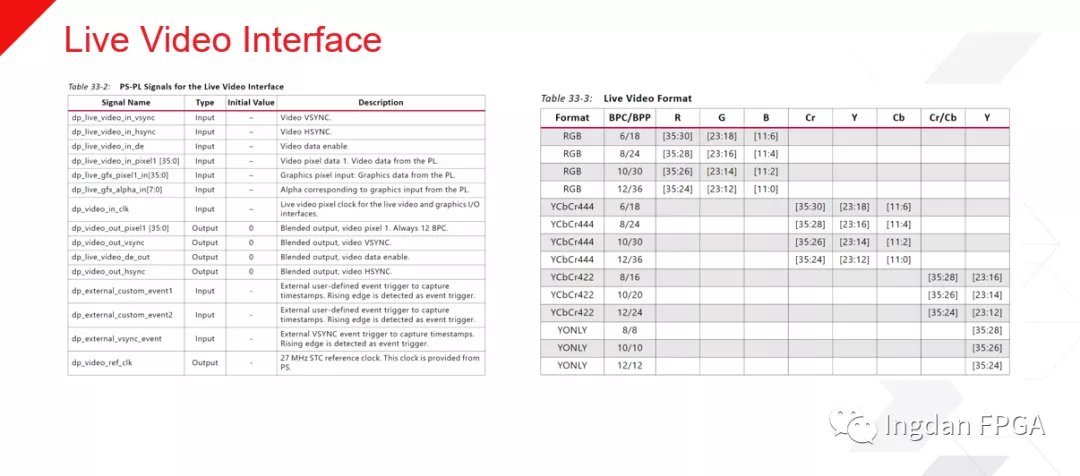

从UG1085第13章DisplayportController章节里面可以看到LiveVideo IN\OUT的架构。视频渲染管道执行图像混合、色度上采样和像素缩放。它有两个输入(混合前)和一个输出(混合后)。这两个输入路径并不相同。一个输入用于视频,另一个用于图形。图形路径有一个调色板,没有色度上采样模块(转换4:2:2到4:4:4),所以图形必须是4:4:4格式。视频路径具有4:2:0到4:2:2转换器、测试图形生成器和色度上采样模块块。

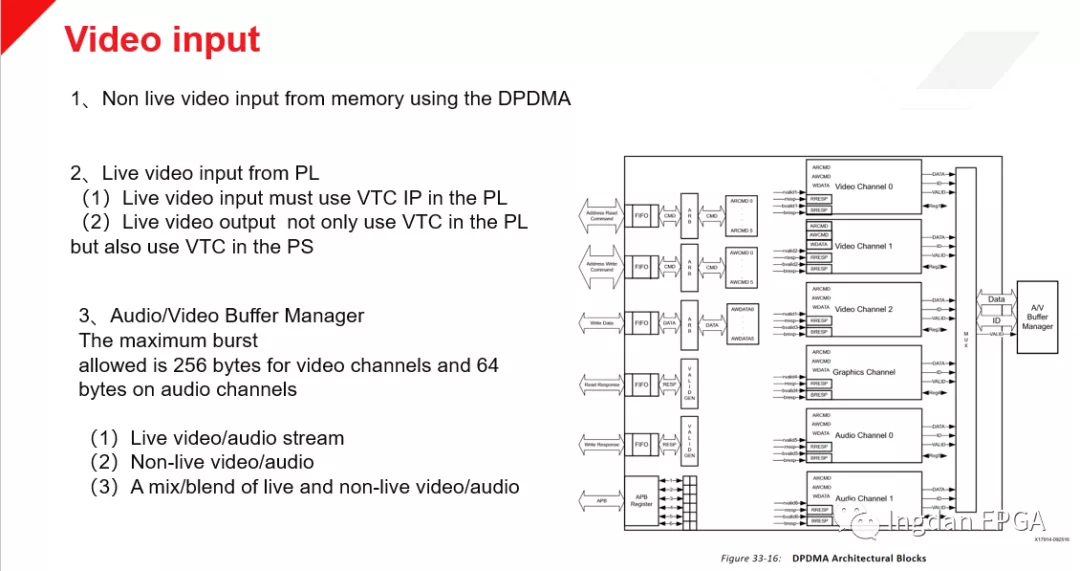

在DP的Subsystem里面包括3个video channels, 1个graphics channel和2个 audio channels;其中Video Input架构如下所示。

Non live mode 为了帮助A/V同步,A/V presentationtime必须通过相关的系统时钟打时间戳,并与A/V(例如视频帧和音频缓冲区)相关联,并将时间戳存储在DPDMA描述符中提供给软件。

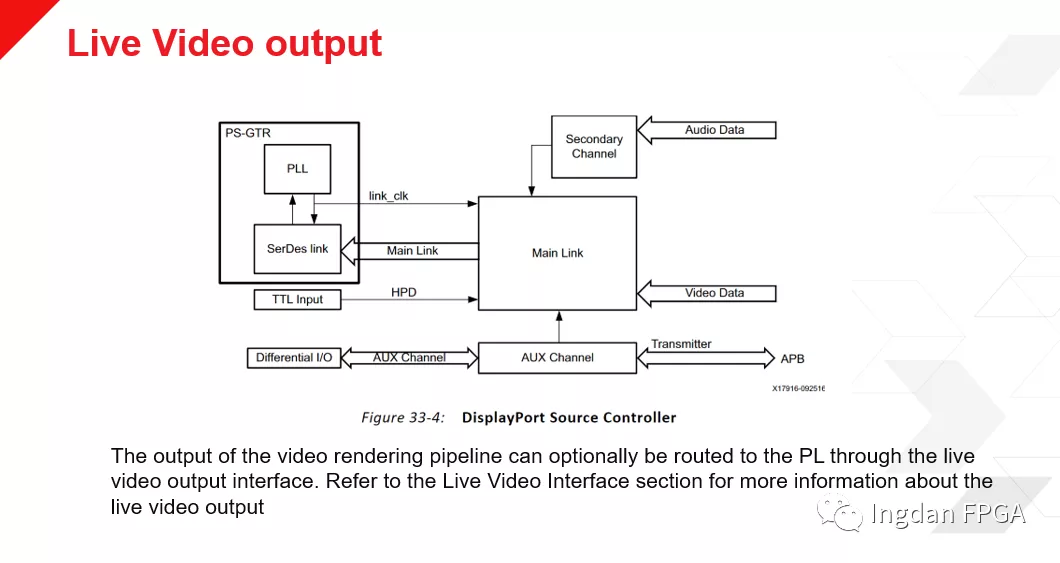

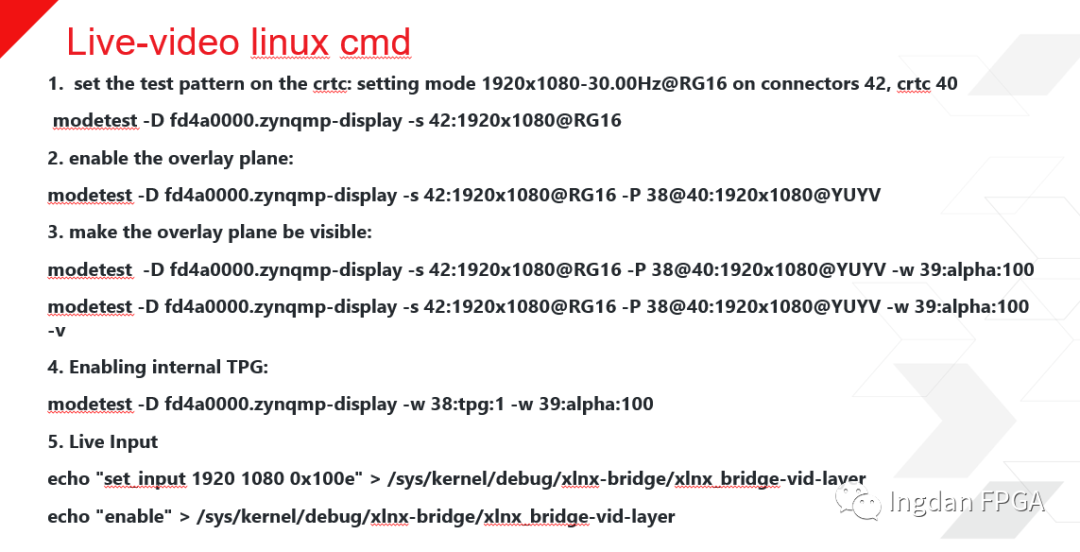

当图像在PS处理完成后要通过PL去做显示,那么可以通过Live Video Out接口传入到PL。

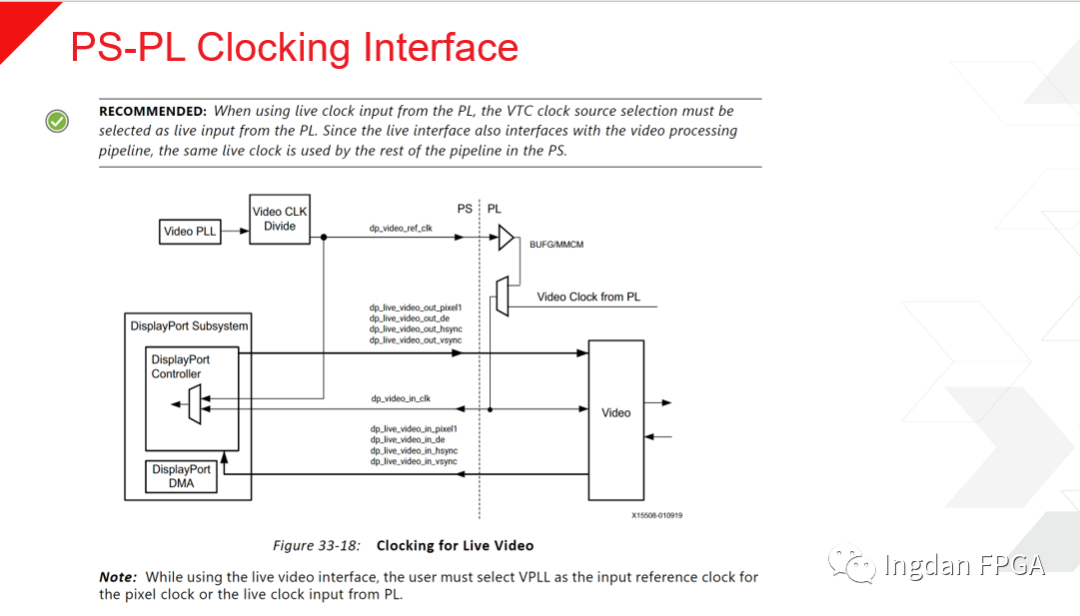

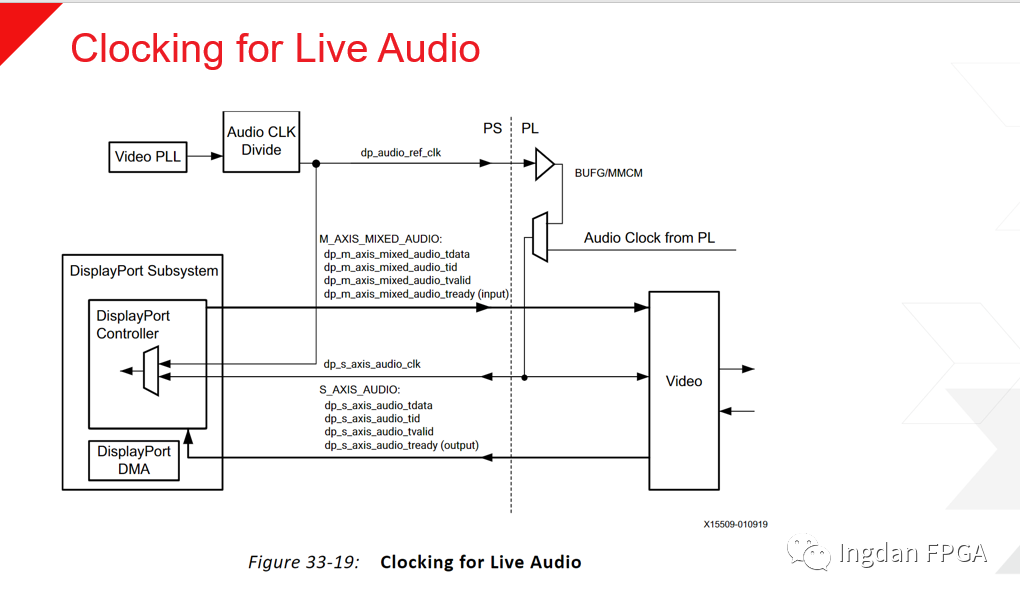

为了保证视频数据和时钟同步需要按照下图来做时钟分配。

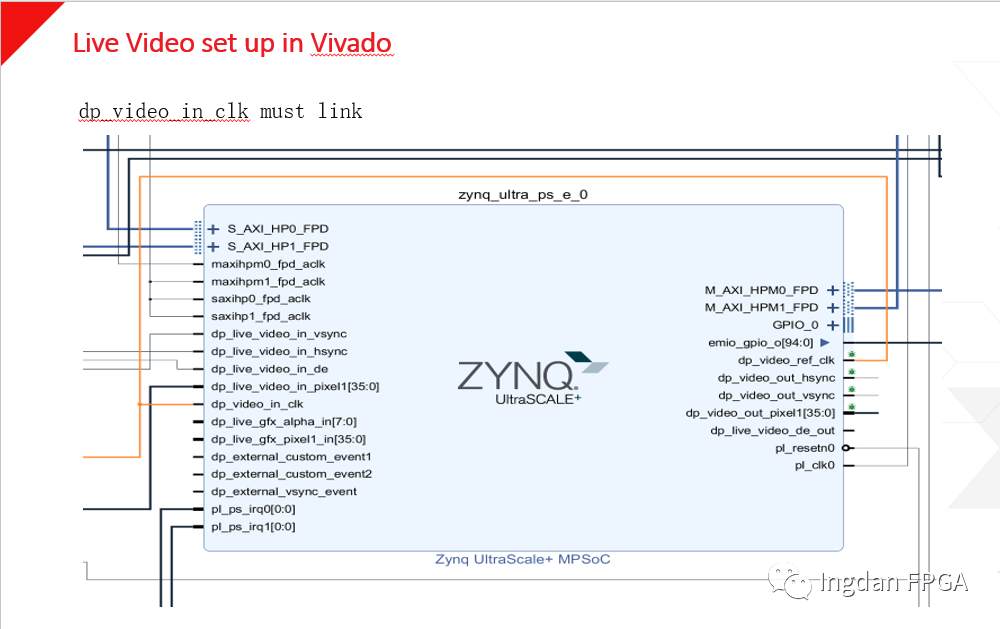

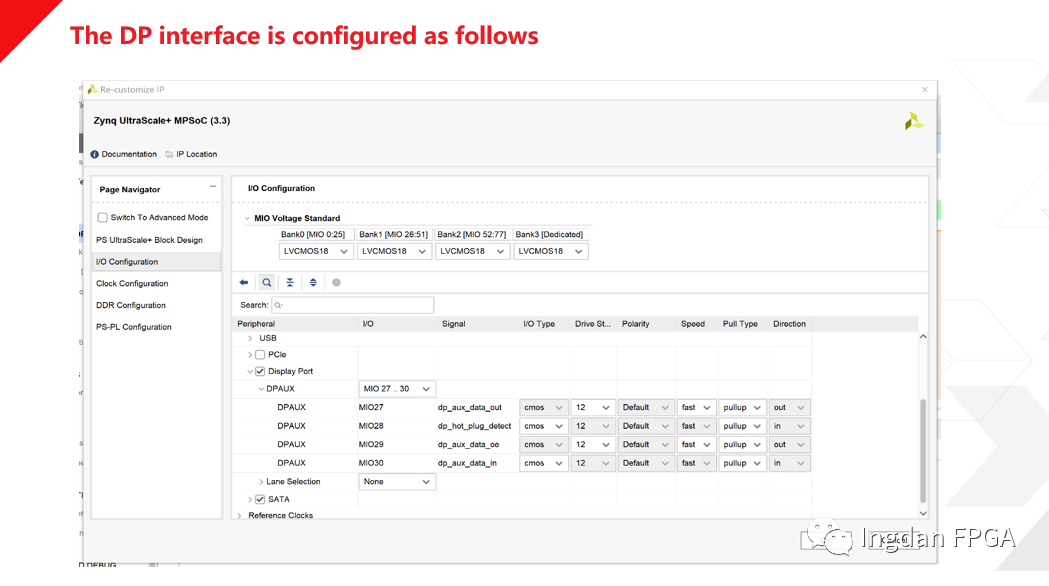

在Vivado里面需要对DP接口做相关配置才能从硬件上面实现其作用。

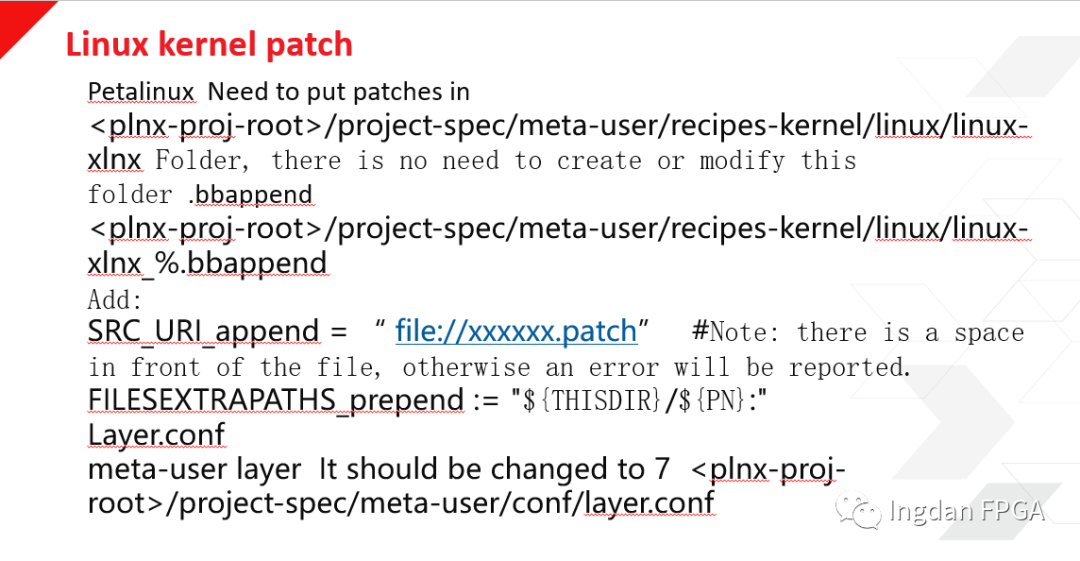

前面已经在Vivado里面完成相关配置,对于Linux端来说也需要做相应的调整来配合才能完整实现其功能。

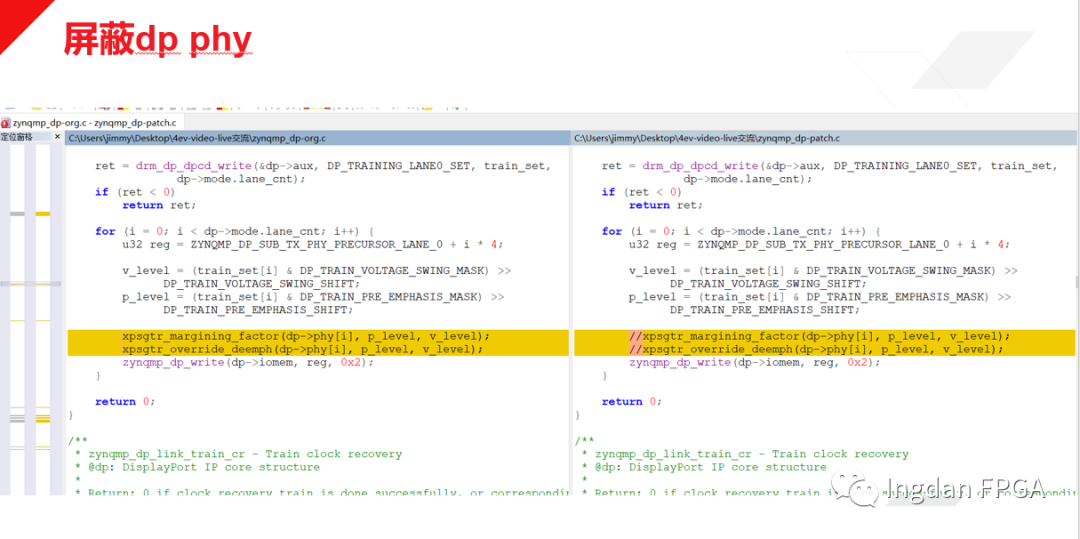

到此工程已经搭建完成;那么由于DP的源和终端之间是需要进行交互匹配才能实现显示功能,而我们没有真实使用DP接口,只是利用他的数据通道而已;所以我们还需要对DP的驱动进行一些小的修改才能使Live Video接口在没有连接DP显示器时候也能输出图像数据。

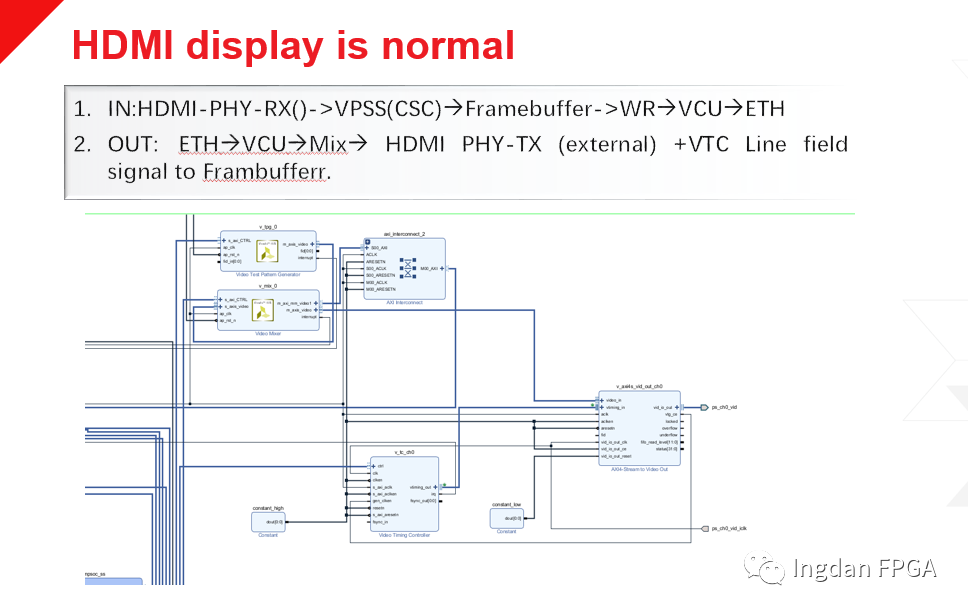

当PL获得Live video的视频数据后,客户可以在PL里面加上Mixer的IP来把PS过来的QT和PL其他视频数据流进行多画面叠加实现OSD的功能。然后可以通过HDMI接口输出去正常显示。

审核编辑 黄昊宇

-

FPGA ZYNQ中PS与PL交互的HP接口详解2026-04-21 1203

-

ZYNQ PS与PL数据交互方式2025-10-15 1443

-

Linux下如何通过UIO监控PL给到PS的中断2023-08-24 3226

-

FPGA系列之“Zynq MPSoC PS-PL AXI Interfaces”2023-02-01 5208

-

基于Xilinx Zynq-7010/20系列——PS+PL异构多核案例开发手册2023-01-03 1549

-

ZCU106在PLDDR实现超低延时编码2022-08-02 1347

-

ZYNQ PS + PL异构多核案例开发手册之axi_timer_pwm_demo案例2021-05-28 2106

-

PS/PL之间的数据交互办法2020-09-15 13159

-

zynq 7020 PS和zynq PL是如何通话的?2020-05-08 2920

-

Xilinx的四个pynq类和PL接口2018-12-30 8550

-

Zynq PS / PL 第四篇:Adam Taylor MicroZed系列之 242017-02-10 1489

-

轻松实现PL“打包”PS的功能2017-02-09 5139

-

datamover完成ZYNQ片内PS与PL间的数据传输2017-02-08 2434

-

【Z-turn Board试用体验】由PS向PL提供时钟信号(转载)2015-06-01 39578

全部0条评论

快来发表一下你的评论吧 !