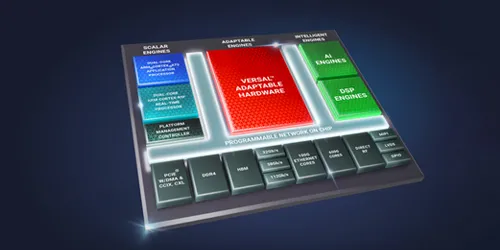

异构平台设计方法 探索赛灵思Versal ACAP设计方法论

FPGA/ASIC技术

描述

探索异构平台的设计方法和概念

赛灵思 Versal ACAP 硬件、IP 和平台开发方法论是旨在帮助精简 Versal 器件设计进程的一整套最佳实践。Versal ACAP从设计之初即采用正确方法并尽早关注设计目标(包括 IP 选择和配置、块连接、RTL、时钟、I/O 接口和 PCB 管脚分配)至关重要。在每个设计阶段中正确定义和验证设计有助于减少后续实现阶段的时序收敛、性能收敛和功耗问题。

鉴于设计的规模与复杂性,因此必须通过执行特定步骤与设计任务才能确保设计每个阶段都能成功完成。本指南基于最佳时间对操作步骤进行了规范,帮助开发者以尽可能最快且最高效的方式实现期望的设计目标。

使用 Vivado® Design Suite 创建设计

Versal ACAP支持包括Vivado® IP intergrator、Vitis™ HLS、RTL等方式创建设计。

Vivado® IP integrator 支持使用 SmartConnect IP 和 NoC 将多个 IP 连接在一起以创建块设计 (.bd) 或 IP 子系统。通过使用 IP integrator,即可将 IP 拖放到设计画布上,以单一线路连接 AXI 接口,设置端口和接口端口布局以将 IP 子 系统连接到顶层设计。这些 IP 块设计还可作为源设计加以封装 并在其它设计中复用。

本指南中详细介绍了开发者通过以上方式创建设计的基本流程和注意事项。

如何完美适配 Vitis 环境?

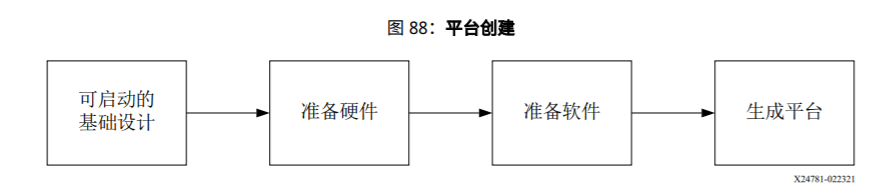

平台是设计的起点,Vitis 统一软件平台凭借“打破软硬件语言壁垒,提升开发效率”的优势,广受开发者青睐。本指南对如何适配 Vitis 环境提供了详细的指导。

可通过赛灵思 GitHub 获取基础平台源代码

同时,如果开发者希望从头开始创建自定义 Vitis 嵌入式平台,本指南亦提供了详细的指导。

-

详解基于赛灵思的Versal™ ACAP设计创建步骤2020-09-28 7409

-

【AD新闻】赛灵思新CEO访华绘蓝图,7nm ACAP平台要让CPU/GPU难企及2018-03-23 4999

-

赛灵思发布基于7nm工艺的ACAP平台产品Versal2018-10-17 4533

-

赛灵思发布自适应计算加速平台芯片系列Versal2018-10-22 6661

-

引领迈入自适应计算时代,Xilinx Versal ACAP荣膺2019“世界互联网领先科技成果”2019-10-21 1369

-

赛灵思旗舰级ACAP平台Versal Premium可助力实现最高生产力2020-03-18 4455

-

揭秘赛灵思计算平台ACAP技术细节2021-01-04 4615

-

赛灵思Versal ACAP如何为算力“跨界赋能”?2021-01-15 3217

-

赛灵思宣布两款Versal ACAP评估套件现已上市2021-03-12 4174

-

探索异构平台的设计方法和概念2021-03-25 2620

-

赛灵思Versal自适应计算加速平台助于高效实现设计目标2021-05-27 2823

-

Versal ACAP:精简设计进程的最佳实践2021-05-31 2741

-

赛灵思Versal自适应计算加速平台指南2021-10-11 5477

-

Versal ACAP的高层次综述2022-06-16 2263

-

Versal ACAP硬件、IP和平台开发方法指南2023-09-13 517

全部0条评论

快来发表一下你的评论吧 !