AXI总线协议的几种时序介绍

接口/总线/驱动

描述

由于ZYNQ架构和常用接口IP核经常出现 AXI协议,赛灵思的协议手册讲解时序比较分散。所以笔者收藏AXI协议的几种时序,方便编程。

(1) AXI_LITE协议:

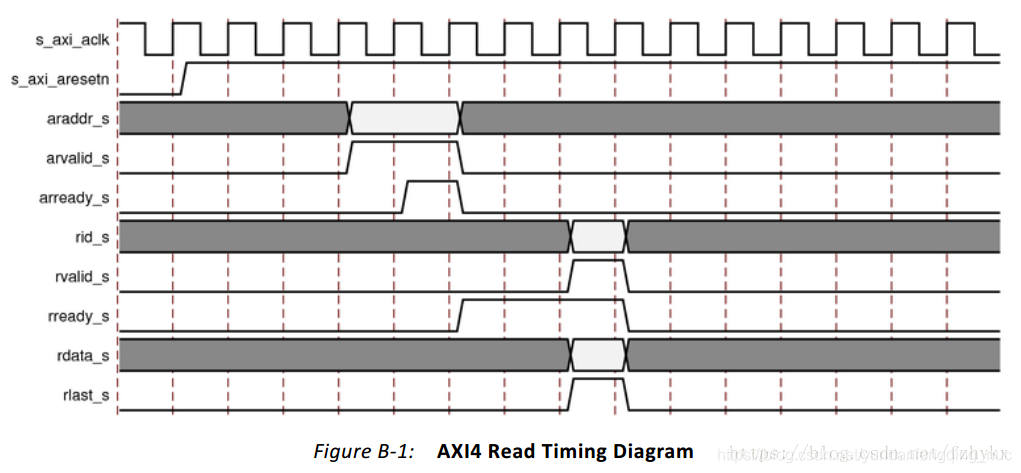

( 1) 读地址通道, 包含ARVALID, ARADDR, ARREADY信号;

( 2) 读数据通道, 包含RVALID, RDATA, RREADY, RRESP信号;

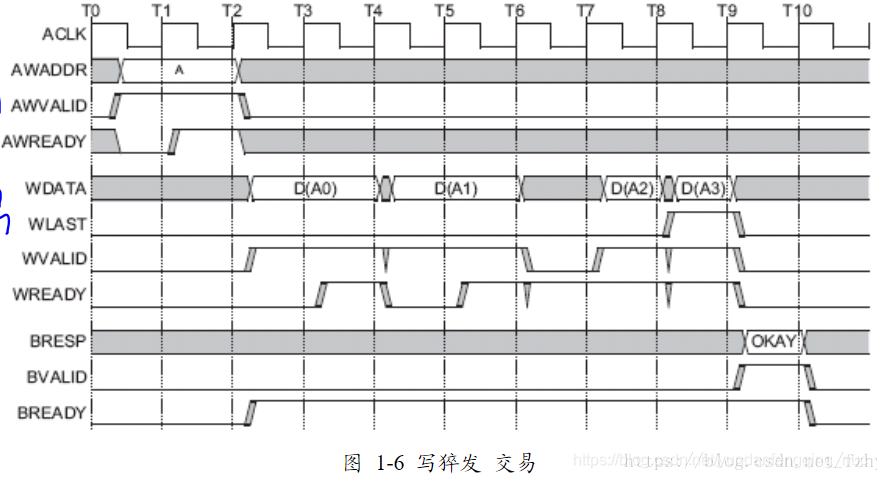

( 3) 写地址通道, 包含AWVALID, AWADDR, AWREADY信号;

( 4) 写数据通道, 包含WVALID, WDATA, WSTRB, WREADY信号;

( 5) 写应答通道, 包含BVALID, BRESP, BREADY信号;( 6) 系统通道, 包含:ACLK, ARESETN信号。

AXI4总线和AXI4-Lite总线的信号也有他的命名特点:读地址信号都是以AR开头( A:address;R:read)写地址信号都是以AW开头( A:address;W:write)读数据信号都是以R开头( R:read)写数据信号都是以W开头( W:write)

AXI_LITE读时序:

AXI_LITE:写时序

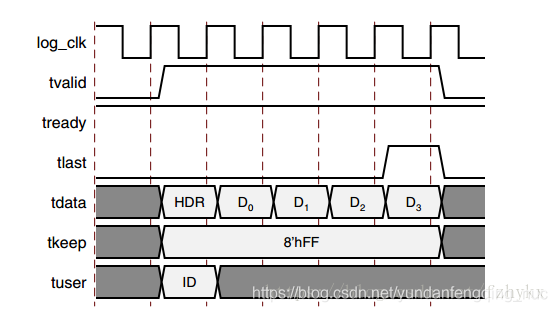

(2) AXI_STREAM:

AXI4-Stream总线的组成有:

( 1) ACLK信号:总线时钟, 上升沿有效;

( 2) ARESETN信号:总线复位, 低电平有效

( 3) TREADY信号:从机告诉主机做好传输准备;

( 4) TDATA信号:数据, 可选宽度32,64,128,256bit

( 5) TSTRB信号:每一bit对应TDATA的一个有效字节, 宽度为TDATA/8

( 6) TLAST信号:主机告诉从机该次传输为突发传输的结尾;

( 7) TVALID信号:主机告诉从机数据本次传输有效;

( 8) TUSER信号 :用户定义信号, 宽度为128bit。

(3)其他

(a)AXI架构

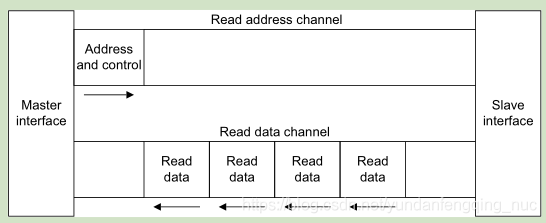

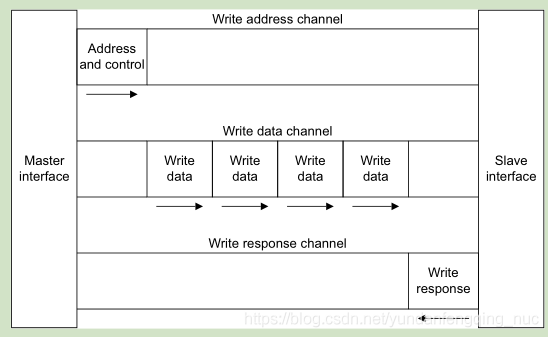

AXI协议是基于burst的传输,并且定义了以下5个独立的传输通道:读地址通道、读数据通道、写地址通道、写数据通道、写响应通道。

地址通道携带控制消息用于描述被传输的数据属性,数据传输使用写通道来实现“主”到“从”的传输,“从”使用写响应通道来完成一次写传输;读通道用来实现数据从“从”到“主”的传输。

图3-1 读结构

图3-2 写架构

AXI是基于VALID/READY的握手机制数据传输协议,传输源端使用VALID表明地址/控制信号、数据是有效的,目的端使用READY表明自己能够接受信息。

读/写地址通道:读、写传输每个都有自己的地址通道,对应的地址通道承载着对应传输的地址控制信息。

读数据通道:读数据通道承载着读数据和读响应信号包括数据总线(8/16/32/64/128/256/512/1024bit)和指示读传输完成的读响应信号。

写数据通道:写数据通道的数据信息被认为是缓冲(buffered)了的,“主”无需等待“从”对上次写传输的确认即可发起一次新的写传输。写通道包括数据总线(8/16…1024bit)和字节线(用于指示8bit 数据信号的有效性)。

写响应通道:“从”使用写响应通道对写传输进行响应。所有的写传输需要写响应通道的完成信号。

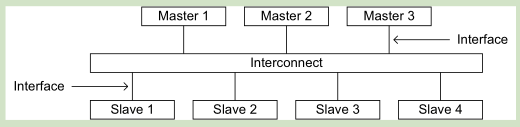

图3-4 接口与互联

AXI协议提供单一的接口定义,能用在下述三种接口之间:master/interconnect、slave/interconnect、master/slave。

可以使用以下几种典型的系统拓扑架构:

共享地址与数据总线

共享地址总线,多数据总线

multilayer多层,多地址总线,多数据总线

在大多数系统中,地址通道的带宽要求没有数据通道高,因此可以使用共享地址总线,多数据总线结构来对系统性能和互联复杂度进行平衡。

寄存器片(Register Slices):

每个AXI通道使用单一方向传输信息,并且各个通道直接没有任何固定关系。因此可以可以在任何通道任何点插入寄存器片,当然这会导致额外的周期延迟。

使用寄存器片可以实现周期延迟(cycles of latency)和最大操作频率的折中;使用寄存器片可以分割低速外设的长路径。

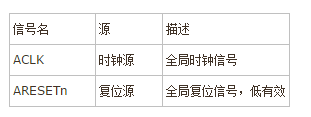

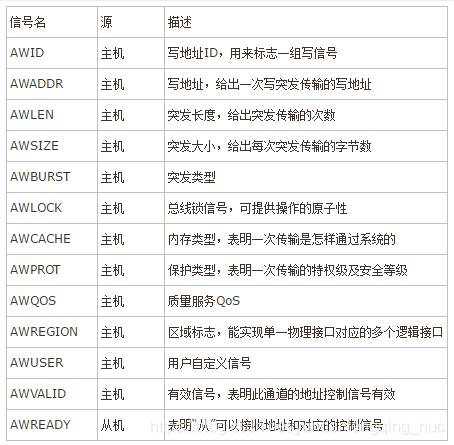

(b)信号描述

表 2-1 全局信号

表 2-2 写地址通道信号

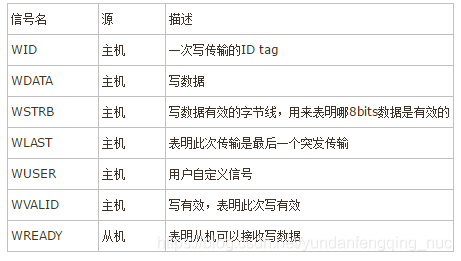

表 2-3 写数据通道信号

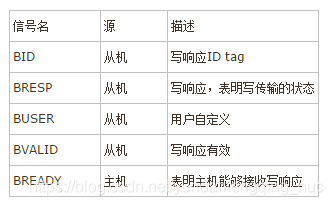

表 2-4 写响应通道信号

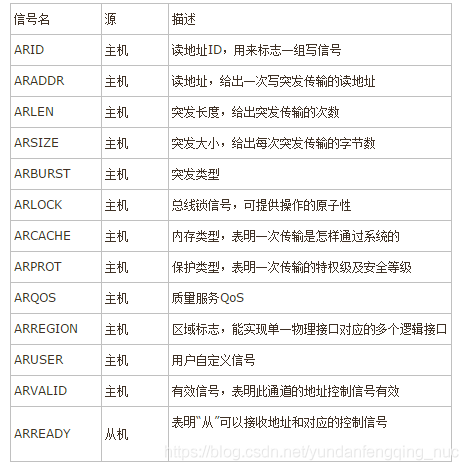

表 2-5 读地址通道信号

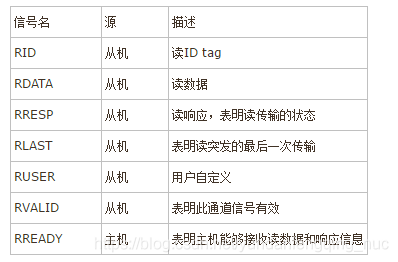

表 2-6 读数据通道信号

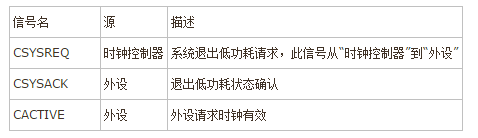

表 2-7 低功耗接口信号

(c) 信号接口要求

3.1时钟复位

时钟

每个AXI组件使用一个时钟信号ACLK,所有输入信号在ACLK上升沿采样,所有输出信号必须在ACLK上升沿后发生。

复位

AXI使用一个低电平有效的复位信号ARESETn,复位信号可以异步断言,但必须和时钟上升沿同步去断言。

复位期间对接口有如下要求:①主机接口必须驱动ARVALID,AWVALID,WVALID为低电平;②从机接口必须驱动RVALID,BVALID为低电平;③所有其他信号可以被驱动到任意值。

在复位后,主机可以在时钟上升沿驱动ARVALID,AWVALID,WVALID为高电平。

3.2基本读写传输

握手过程

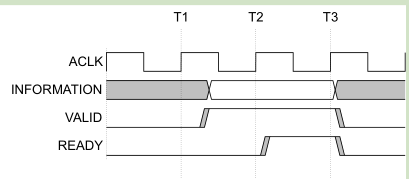

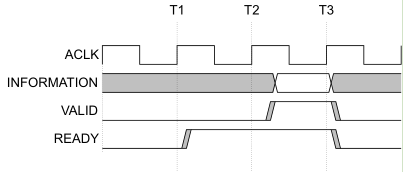

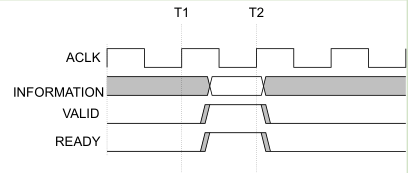

5个传输通道均使用VALID/READY信号对传输过程的地址、数据、控制信号进行握手。使用双向握手机制,传输仅仅发生在VALID、READY同时有效的时候。下图是几种握手机制:

图 3-1 VALID before READY 握手

图 3-2 READY before VALID 握手

图 3-3 VALID with READY 握手

通道信号要求

通道握手信号:每个通道有自己的xVALID/xREADY握手信号对。

写地址通道:当主机驱动有效的地址和控制信号时,主机可以断言AWVALID,一旦断言,需要保持AWVALID的断言状态,直到时钟上升沿采样到从机的AWREADY。AWREADY默认值可高可低,推荐为高(如果为低,一次传输至少需要两个周期,一个用来断言AWVALID,一个用来断言AWREADY);当AWREADY为高时,从机必须能够接受提供给它的有效地址。

写数据通道:在写突发传输过程中,主机只能在它提供有效的写数据时断言WVALID,一旦断言,需要保持断言状态,知道时钟上升沿采样到从机的WREADY。WREADY默认值可以为高,这要求从机总能够在单个周期内接受写数据。主机在驱动最后一次写突发传输是需要断言WLAST信号。

写响应通道:从机只能它在驱动有效的写响应时断言BVALID,一旦断言需要保持,直到时钟上升沿采样到主机的BREADY信号。当主机总能在一个周期内接受写响应信号时,可以将BREADY的默认值设为高。

读地址通道:当主机驱动有效的地址和控制信号时,主机可以断言ARVALID,一旦断言,需要保持ARVALID的断言状态,直到时钟上升沿采样到从机的ARREADY。ARREADY默认值可高可低,推荐为高(如果为低,一次传输至少需要两个周期,一个用来断言ARVALID,一个用来断言ARREADY);当ARREADY为高时,从机必须能够接受提供给它的有效地址。

读数据通道:只有当从机驱动有效的读数据时从机才可以断言RVALID,一旦断言需要保持直到时钟上升沿采样到主机的BREADY。BREADY默认值可以为高,此时需要主机任何时候一旦开始读传输就能立马接受读数据。当最后一次突发读传输时,从机需要断言RLAST。

通道间关系

AXI协议要求通道间满足如下关系:

写响应必须跟随最后一次burst的的写传输

读数据必须跟随数据对应的地址

通道握手信号需要确认一些依耐关系

通道握手信号的依耐关系

审核编辑:汤梓红

-

NVMe简介之AXI总线2025-05-21 908

-

AMBA3.0 AXI总线接口协议的研究与应用2023-09-20 922

-

AXI4-Lite协议简明学习笔记2023-06-19 5955

-

AXI总线协议简介2022-10-10 11469

-

AXI总线协议的简单知识2022-07-15 4292

-

AXI接口协议详解2022-04-08 6021

-

AMBA 3.0 AXI总线接口协议的研究与应用2021-04-12 1205

-

SPI总线协议介绍2021-03-03 2134

-

AXI总线协议总结2021-02-04 1896

-

基于AXI总线的加法器模块解决方案2020-12-23 3473

-

AXI总线协议的几种时序介绍2019-05-12 11881

-

玩转Zynq连载3——AXI总线协议介绍12019-05-06 2791

-

AXI 总线和引脚的介绍2018-01-05 11424

全部0条评论

快来发表一下你的评论吧 !