AXI通道定义及AXI总线信号描述

描述

学习内容

本文主要介绍了AXI通道以及在每个通道下信号的概述。

AXI通道定义

简单回顾前文提到的AXI的通道定义,AXI协议是基于突发的,并定义了以下独立的传输通道:

• read address

• read data

• write address

• write data

• write response

每个独立通道由一组信息信号、VALID信号和READY信号组成。用于提供双向握手机制。VALID信号:信息源端使用VALID信号来显示何时是有效地址;数据或控制信息是否在通道上可用。READY信号:目的端使用READY信号来显示何时可以接受信息。LAST信号:读数据通道和写数据通道都包括一个LAST信号,以指示传输中的最后一个数据。

读写数据地址通道

读写通道都各自包含了他们各自的地址通道,地址通道携带了所有被需请求的的地址和相关的控制信息。

读数据通道

读数据通道把读数据和读响应信息从slave传送到master。其中包含下述信息:

数据总线,可以是8、16、32、64、128、256、512、1024位。

一个读响应信号用于表示读操作完成状态。

写数据通道

写数据通道将写数据从master传送到slave。其中包含下述信息:

数据总线,可以是8、16、32、64、128、256、512、1024位。

一个字节的通道频闪信号(WSTRB)指示8个数据位,指示哪些数据字节是有效的。

写数据通道信息总是被当作缓冲处理,因此主机执行写操作时,不需要从机确认之前的写操作。

写响应通道

写响应通道由从机发送给主机,包含了写响应信号,用于指示当前写操作是否完成。所有写操作都需要在写响应通道上发送完成信号。

AXI总线信号描述

了解完通道的内容,接着介绍具体的信号功能。本节介绍的是AXI4-Full的信号功能,后文将介绍AXI4-Lite接口,相对AXI4-Full,AXI4-Lite接口信号会少很多。

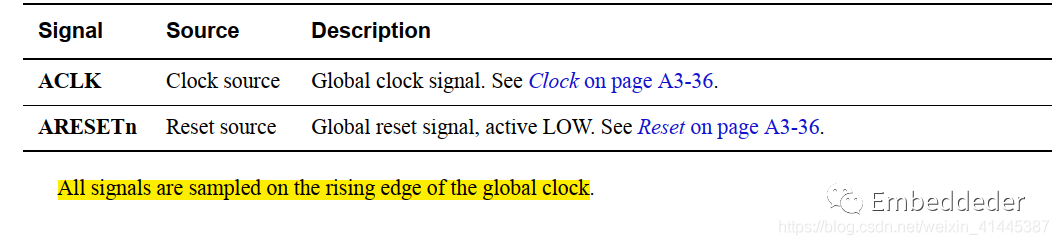

全局信号

ACLK :全局时钟。

ARESETn :复位信号低电平有效。

在AXI总线中所有的数据都是在全局时钟的上升沿进行采样的。

写地址通道信号

下面的表格列举出写地址通道的信号,常用的信号将加粗标注。

| AWID | Master | 写地址ID。这个信号是信号的写地址组的识别标签。指定某些特殊传输任务的顺序 |

| AWADDR | Master | 写地址。写地址给出了写突发传输下第一个数据的地址。 |

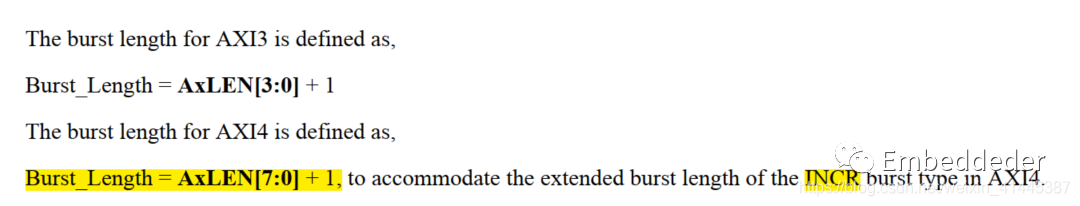

| AWLEN | Master | 突发传输长度。AWLEN给出了在一次突发传输中的确切数目长度。在AXI3和AXI4定义不同 |

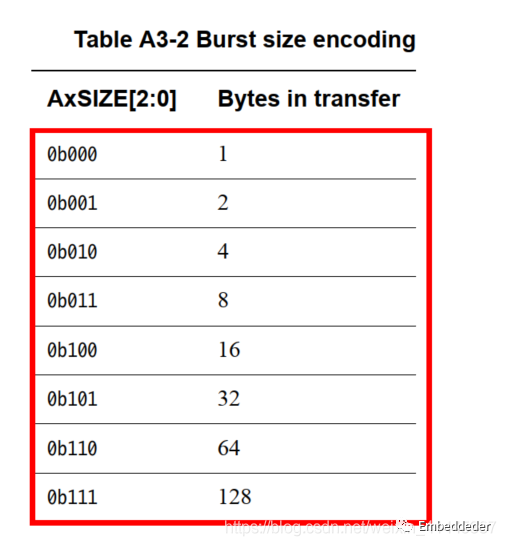

| AWSIZE | Master | 突发传输的大小。这个信号指示了单次传输的的数据大小。 |

| AWBURST | Master | 突发传输的类型。突发类型和大小信息,确定如何计算突发内每个传输的地址。 |

| AWLOCK | Master | 锁存的类型。提供关于转移的附加信息。在AXI3和AXI4定义不同,区分正常传输(0)和独有传输(1) |

| AWCACHE | Master | 内存类型。这个信号指示操作如何在系统中进行。总线中的存储类型(0010:不缓存模式) |

| AWPROT | Master | 保护类型。这个信号表明操作的优先级和安全级别,以及操作是数据访问还是指令访问。 |

| AWQOS | Master | 服务质量QoS。为每个写操作发送的QoS标识符。仅在AXI4中支持。 |

| AWREGION | Master | 区域ID标识符。允许一个slave上的单个物理接口用于多个逻辑接口。仅在AXI4中支持。 |

| AWUSER | Master | 用户信号。可选写地址通道自定义信号。(完成用户的自定义操作),仅在AXI4中支持。 |

| AWVALID | Master | 写地址有效。这个信号表明通道正在发送有效的写地址和控制信息。 |

| AWREADY | Slave | 写地址准备。这个信号表明从机准备接受一个地址和相关的控制信号。 |

| Signal | Source | Description |

|---|

如何确定突发传输的大小、长度、类型?

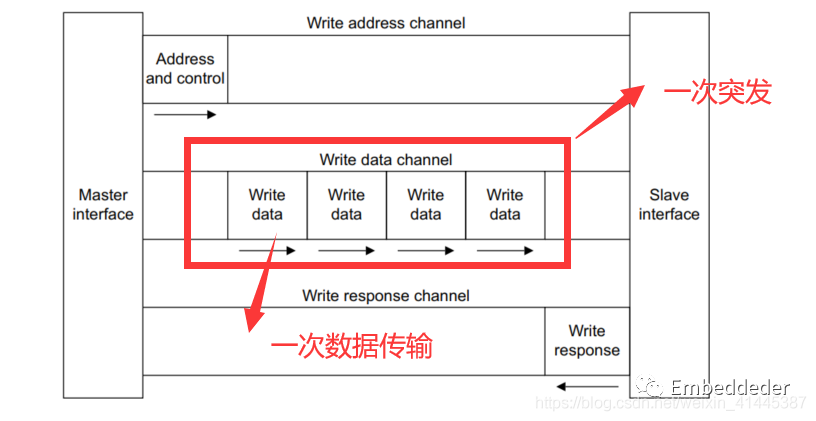

下面给出一个例子:如下图所指示:下图是一个读地址通道的操作,这里用方框框选的数据传输,是一次突发传输。对于该次突发传输:一共进行了四次数据传输,所以突发的长度就是4。然后针对一次数据传输,每次数据传输位宽,为突发传输的大小。假设传输的数据是8位的,这里的突发长度就是8。

对于突发传输的长度的不同,这里直接引用ARM的文档内容参考即可。

对于突发的大小,这里定义了组寄存器来标识传输的数据位宽:

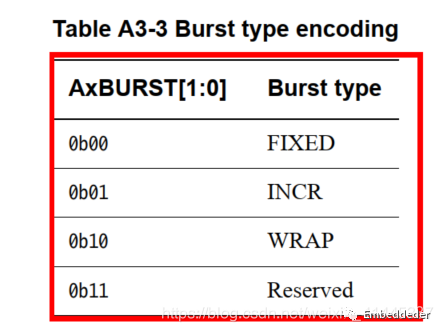

对于突发的类型,这里有三种突发类型分别如下:

FIXED(固定型):在一个固定的突发中,地址对于突发中的每一次传输都是相同的。这种突发类型用于重复访问相同的位置,例如加载或清空FIFO。INCR(自增型):在递增的突发中,突发中每个传输的地址是前一个传输的地址的增量。增量值取决于传输的大小。例如,在一个大小为4个bvtes的突发中,每个传输的地址是前一个地址的加4个。这种突发类型用于访问顺序存储器。

WRAP(回环突发):回环突发类似于递增突发。不同的是,如果达到了地址上限,地址将被重新装一个较低的地址。这种突发类型用于高速缓存线访问。使用回环突发必须遵守下列限制条件:

起始地址必须与每次传输的大小一致;

突发的长度必须是2、4、8或16。

回环突发要求:

突发使用的最低地址与要传输的数据的总大小对齐,即为((突发中每个传输的大小)×(突发中传输的数量))。这个地址被定义为换行边界。

在每次传输之后,地址以同样的方式增加,就像增加带宽一样。但是,如果这个增加的地址是((wrap boundary) +(要传输的数据的总大小),那么地址就会绕到wrap boundary。

在突发中的第一次传输可以使用一个比绕包边界更高的地址,这取决于适用于绕包突发的限制。这意味着对任何第一个地址高于边界的操作,会自动换行突发。

突发类型的寄存器的解码表如下:

写数据通道信号

| WID | Master | 写ID。这个信号是写数据传输的ID标签。仅在AXI3中支持 |

| WDATA | Master | 写入数据 |

| WSTRB | Master | 写频闪信号。该信号指示哪些字节通道保存有效数据。写数据总线的每8位有一个写频闪位。 |

| WLAST | Master | LAST指示信号。这个信号指示写操作中的最后一次传输。 |

| WUSER | Master | 用户信号。可选写入数据通道的自定义信号。仅在AXI4中支持。 |

| WVALID | Master | 写有效。这个信号表明有效的写数据和频闪是可用的 |

| WREADY | Slave | 写准备。这个信号表明从机可以接受写数据。 |

| Signal | Source | Description |

|---|

写响应通道信号

| BID | Slave | 写ID。这个信号是写数据传输的ID标签。仅在AXI3中支持 |

| BRESP | Slave | 写响应。这个信号指示写操作的状态。 |

| BUSER | Slave | 用户信号。可选写响应通道中的自定义信号。仅在AXI4中支持。 |

| BVALID | Slave | 写响应有效。该信号表明通道正在发出有效的写响应信号。 |

| BREADY | Master | 写响应准备。这个信号表明主机可以接受写响应。 |

| Signal | Source | Description |

|---|

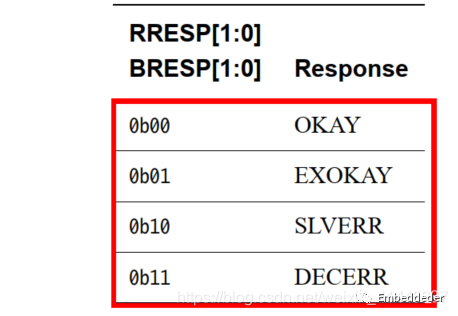

对于写响应通道的BRESP信号,具体响应有下述四种类型:

OKAY:正常访问成功。表示正常访问成功。也可以指示独占访问失败。

EXOKAY:独占访问。指示独占访问的读或写部分已经成功。

SLVERR:从机错误。当访问成功到达从机时使用,但是从机向主机返回一个错误条件。

DECERR:解码错误。通常由互连组件生成,以指示在操作地址处没有从从机响应。

BRESP信号解码表如下:

读地址通道信号

| ARID | Master | 读地址ID。这个信号是信号读地址组的识别标签。指定某些特殊传输任务的顺序 |

| ARADDR | Master | 读地址。读地址给出了读突发传输下第一个数据的地址。 |

| ARLEN | Master | 突发传输长度。AWLEN给出了在一次突发传输中的确切数目长度。在AXI3和AXI4定义不同 |

| ARSIZE | Master | 突发传输的大小。这个信号指示了单次传输的的数据大小。 |

| ARBURST | Master | 突发传输的类型。突发类型和大小信息,确定如何计算突发内每个传输的地址。 |

| ARLOCK | Master | 锁存的类型。提供关于转移的附加信息。在AXI3和AXI4定义不同,区分正常传输(0)和独有传输(1) |

| ARCACHE | Master | 内存类型。这个信号指示操作如何在系统中进行。总线中的存储类型(0010:不缓存模式) |

| ARPROT | Master | 保护类型。这个信号表明操作的优先级和安全级别,以及操作是数据访问还是指令访问。 |

| ARQOS | Master | 服务质量QoS。为每个读操作发送的QoS标识符。仅在AXI4中支持。 |

| ARREGION | Master | 区域ID标识符。允许一个slave上的单个物理接口用于多个逻辑接口。仅在AXI4中支持。 |

| ARUSER | Master | 用户信号。可选读地址通道自定义信号。(完成用户的自定义操作),仅在AXI4中支持。 |

| ARVALID | Master | 读地址有效。这个信号表明通道正在发送有效的读地址和控制信息。 |

| ARREADY | Slave | 读地址准备。这个信号表明从机准备接受一个地址和相关的控制信号。 |

| Signal | Source | Description |

|---|

读数据通道信号

| RID | Slave | 读ID标签。这个信号是识别标签的读取数据信号的从机产生的 |

| RDATA | Slave | 读入数据 |

| RRESP | Slave | 读取响应。这个信号指示读传输的状态。。 |

| RLAST | Slave | LAST指示信号。这个信号指示读操作中的最后一次传输。 |

| RUSER | Slave | 用户信号。可选读取数据通道中的用户自定义信号。仅在AXI4中支持。 |

| WVALID | Slave | 读有效。该信号表明通道正在发送所需的读取数据。 |

| RREADY | Master | 读准备。该信号表明主机可以接受读取数据和响应信息 |

| Signal | Source | Description |

|---|

Reference

正点原子ZYNQ视频教程。

ARM官方文档:IHI0022D

审核编辑:汤梓红

-

Xilinx zynq AXI总线全面解读2020-12-04 9351

-

基于AXI总线的加法器模块解决方案2020-12-23 3475

-

ARM+FPGA开发:基于AXI总线的GPIO IP创建2020-12-25 6997

-

NVMe IP之AXI4总线分析2025-06-02 6196

-

ZYNQ & AXI总线 & PS与PL内部通信(用户自定义IP)2018-01-08 14611

-

玩转Zynq连载3——AXI总线协议介绍12019-05-06 2792

-

AXI总线的相关资料下载2022-02-09 819

-

看看在SpinalHDL中AXI4总线互联IP的设计2022-08-02 3299

-

AMBA AXI总线学习笔记2015-11-11 1299

-

AXI 总线和引脚的介绍2018-01-05 11426

-

你必须了解的AXI总线详解2020-10-09 9236

-

ZYNQ中DMA与AXI4总线2020-11-02 5294

-

AXI总线学习(AXI3&4)2021-12-05 980

-

AXI4协议五个不同通道的握手机制2023-05-08 2277

-

AXI总线工作流程2023-05-25 2004

全部0条评论

快来发表一下你的评论吧 !