FPGA 应用的电源模块的选择

可编程逻辑

描述

现场可编程门阵列 (FPGA) 是许多原型和中小批量产品的核心。FPGA 的主要优势是开发过程中的灵活性、简单的升级路径、更快的上市时间和相对较低的成本。一个关键的缺点是复杂性,FPGA 通常包含复杂的片上系统 (SoC)。

这种复杂性对电源提出了苛刻的要求。为应对这些挑战,电源需要多个输出以及开关稳压器的组合以提高效率和线性稳压器以实现清洁电源。

本文描述了 FPGA 的特殊电源要求,解释了如何为这些智能芯片设计电源,然后回顾了针对 FPGA 应用的电源模块的选择。

计算系统功率

为FPGA供电似乎为整个系统供电。电源设计工程师面临着提供 3 到 15 个电压轨(有时甚至更多)的挑战;而这仅仅是开始。FPGA 通常使用需要低核心电压的最新晶圆制造技术制造,但电源还必须为特殊模块和电路的多个轨道供电,提供多个电压电平,为高功率模块提供额外电流,并满足对噪声敏感元件的要求。

只是让事情变得更复杂一些,即使是来自同一制造商的 FPGA 也可能会有很大差异,因此工程师为每个芯片选择最佳电源至关重要。该选择取决于诸如每个电源轨的电压和功率需求、电源轨的排序要求和系统电源管理需求等因素。

设计 FPGA 电源的第一步是确定各个电压轨及其要求。FPGA 供应商通常会提供一个“引脚列表”,指定连接到设备电压轨的每个供电引脚的电压电平。例如,表 1显示了Altera 的Stratix IV GX FPGA的 一些电压轨。

表 1:Altera Stratix IV GX 的电压轨子集。(Altera 提供)

从表 1 可以看出,FPGA 的电源轨运行在几个不同的电压下,具体取决于供电的模块。要求通常包括内核(为内部逻辑阵列供电)、I/O(驱动 I/O 缓冲器,这些缓冲器可以分组在不同的电压下运行)、锁相环 (PLL)(为 PLL 供电)核)和收发器(为收发器、接收器和发射器提供数字和模拟电路)。

一旦确定了各个电压轨,下一步就是依次计算每个轨的电流消耗。应将共享铁轨的电流消耗添加到正在分析的铁轨中,以得出该铁轨的总数。FPGA 制造商经常为此提供在线计算器。接下来,工程师应将构成 FPGA 的所有元件的功耗相加,以准确估算整个芯片的功耗。

计算完功耗后,下一步是检查每个电源轨的电压变化容限和最大电压纹波规范。这些参数通常可以在 FPGA 的数据表中找到。

负载调节规范确定了电压调节器输出可能因负载变化而偏离的范围(以 mV 为单位)。如果电源来自开关 DC-DC 电压转换器(“开关稳压器”),则负载调节的典型规格为 ±5 mV。如果电压轨指定为 1.2 V,这只是 0.4% 的偏差。

电压纹波以 mV 为单位从峰到峰测量,其幅度取决于为所分析的特定轨供电的稳压器的设计。输出滤波严重影响电压(和电流)纹波性能。(请参阅 TechZone 文章“电容器选择是良好稳压器设计的关键”。)大多数 FPGA 可承受高达 2% 或更高的电压纹波,这完全在现代开关稳压器的能力范围内。

开关稳压器还是线性稳压器?

FPGA 电源设计过程的下一步是决定一个特定的电源轨应该由开关稳压器还是线性稳压器供电。需要特别注意为 PLL 和收发器电路等噪声敏感电路供电的模拟电源轨。这些轨道上的过多噪声可能会影响电路性能。

线性稳压器提供无纹波电源,响应速度快,使用更简单,并且比开关器件占用更少的空间。它们是噪声敏感型 PLL 和收发器轨的不错选择。主要缺点是效率低下,尤其是在输出电压远低于输入电压的情况下。

开关稳压器是更高功率轨的更好选择,因为其更高的效率比更低的噪声更重要。它们是为 FPGA 的数字内核逻辑和 I/O 供电的理想选择,其中电流要求很容易达到数十安培。开关稳压器的缺点是它更复杂、更大,并且需要更多的外部元件。

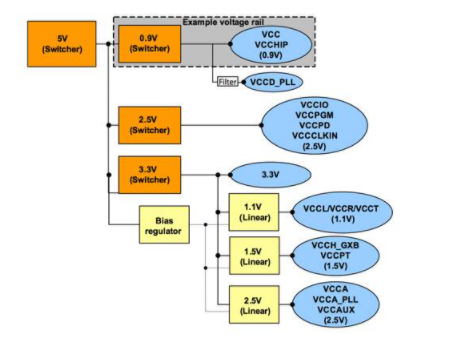

由此产生的电源可能有些复杂,包括“电源树”中的多个开关稳压器和线性稳压器(图 2)。

图 2:由开关和线性稳压器组成的 FPGA 电源。(Altera 提供)

FPGA电源模块

FPGA的电源 通常包括开关稳压器和线性稳压器的组合,以合理的效率提供不同的电压和稳定的电源。设计这样的电源并非易事,但通过将电路基于将多个开关和线性稳压器集成到单个芯片中的电源模块,事情可以变得更加简单。

例如, Maxim 的 MAX8660电源模块包含四个开关稳压器(以 2 MHz 运行,因此鼓励使用小电感器)和四个线性稳压器。开关稳压器自动从脉冲宽度调制 (PWM) 切换到轻负载操作,以降低工作电流并延长电池寿命。

该器件为开关稳压器提供 0.725-3.3 V (0.4-1.6 A) 的输出电压,为低压差 (LDO) 线性稳压器提供 1.7-3.3 V (30-500 mA) 的输出电压,所有电压均在 2.6 至6 V 输入。

该芯片还集成了电源管理能力和功能,例如输出开/关控制、低电量检测、复位输出和两线 I 2 C 串行接口。

Intersil为小型 FPGA 应用提供ISL9440 。该芯片结合了三个开关稳压器和一个 LDO 线性稳压器。每个输出可调低至 0.8 V,该器件采用 4.5-24 V 电源供电。

ISL9440 在紧凑的 5 x 5 mm QFN 封装中提供内部软启动和独立使能输入,以简化电源轨排序。该芯片采用内部环路补偿来最大限度地减少外围组件,从而实现紧凑的设计和较低的总体解决方案成本。

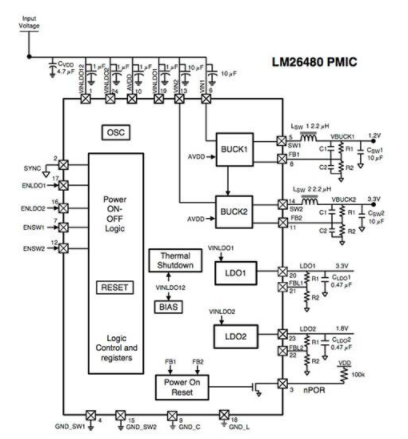

德州仪器(TI) 还提供将开关稳压器的效率与线性稳压器的无噪声电源相结合的电源模块。例如,LM26480(图 3)集成了两个 1.5 A 降压(“降压”)开关稳压器和两个 300 mA 线性稳压器。该器件采用 2.8 至 5.5 V 电源供电,第一个开关稳压器在 1.5 A 时提供 0.8-2 V,而第二个在 1.5 A 时提供 1.0-3.3 V。2 MHz 开关稳压器的工作效率高达 96%。线性稳压器在高达 300 mA 时提供 1-3.5 V。

图 3:Texas Instruments 的 LM26480 集成了两个开关稳压器和两个线性稳压器。

-

如何选择合适的电源模块?你了解电源模块可靠性测试吗?2024-07-04 2490

-

如何选择适合自己应用的AC/DC电源模块?2024-05-30 1384

-

如何选择适合自己需求的DC电源模块?2024-04-28 967

-

DC电源模块的选择技巧2024-03-01 1969

-

了解DC电源模块的基本参数及选择方法2024-01-10 1777

-

选择正确的DC电源模块的重要性2023-12-01 1273

-

如何根据不同仪器选择适合的电源模块?2023-11-10 1551

-

如何选择合适的电源模块?2023-08-01 2169

-

如何选择合适的电源模块2023-04-14 3574

-

FPGA应用的电源模块的选择案例2023-03-30 2993

-

电源模块的选择、国内外知名电源模块厂家排名及厂家优势特点汇总2021-11-06 3324

-

电源模块的正确选择2018-06-24 6744

-

教您电源模块的选择技巧2018-06-23 5993

全部0条评论

快来发表一下你的评论吧 !