SystemVerilog如何进行有效的功能验证

可编程逻辑

描述

摩尔定律指出,集成芯片可容纳的晶体管数目约每18个月增加一倍,性能也将提升一倍。对于FPGA和数字IC设计开发的工程师们而言,感同身受的是,在庞大复杂的系统研发过程中,设计和验证几乎同等重要,甚至验证工作将花费整个周期的70%~80%。

如何进行有效的功能验证,是我们必须面对的课题。随着芯片设计验证技术的发展,SystemVerilog语言在业界获得了广泛应用。本文将介绍常用的验证技术和方法。

无论是从事FPGA开发,还是数字IC设计,验证是一个无法逃避的问题,是整个项目周期中极为重要的一环。

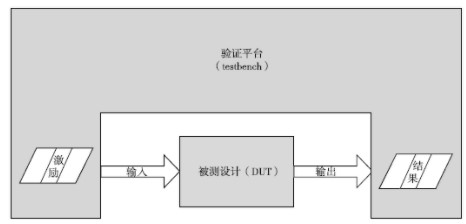

验证是一个覆盖面比较广的课题,主要包括功能验证、物理验证、时序验证等。我们常常涉及功能验证,以确保设计能够按照设计规范实现应有功能。为了完成功能验证,我们需要搭建验证平台testbench,这也是业界最常用的验证手段。

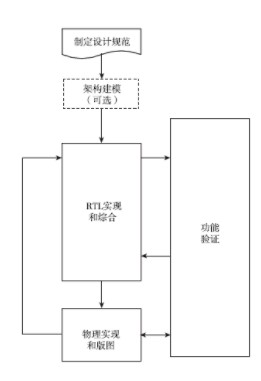

芯片设计流程

我们以专用芯片(ASIC)设计举例,从设计规范到投片的设计流程,如图:

与ASIC设计不同的是,在FPGA的设计流程中,没有物理实现和版图设计这一块,因为FPGA已经是经过测封后的成品,只需要按照设计架构进行开发和验证。因此,数字IC工程师与FPGA工程师常常可相互转换。

RTL设计是将设计规范进行逻辑代码实现的过程,我们常常使用verilog HDL或VHDL语言进行设计。通过采用相对合理的设计方案,在资源消耗、处理速率和时延上进行平衡。

功能验证作为一个独立模块,但验证过程却相当复杂:定义测试用例,搭建测试环境,运行测试用例,以及保证功能覆盖率。

怎样进行有效功能验证,确保设计可靠性,是我们最关心的课题。

验证平台

以FPGA开发为例,当我们完成功能模块设计后,别急着进行综合与实现,以及上板调试,进行行为仿真或功能仿真验证是必要的。

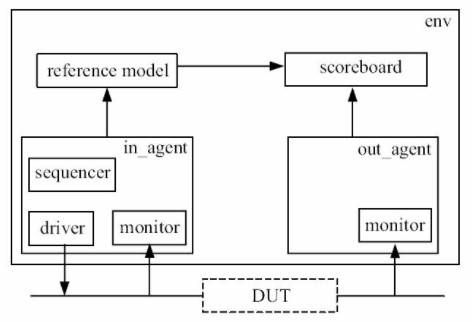

在功能验证中,我们在被测设计(Design Under Test,DUT)外搭建验证平台,就像这样:

验证平台可以用来做什么,又应该怎么做?

如上图所示,对于DUT,我们需要通过testbench产生测试激励,然后把测试激励应用到DUT中,而DUT产生的输出结果,我们需要进行检查,看验证测试是否通过,也就是,我们要确保输出结果和期望一致。

产生用户激励常用方法:一种是提供确定输入,进行直接测试(direct test);另外就是产生随机数据,进行随机测试(random test)。

通常,我们需要产生必要的使能信号、测试数据、地址等,通过DUT接口送入。

在高级验证平台种,激励被工程师建模并封装,进行事务级验证(transaction based verification)。

验证的目的,在于检查DUT的输出是否和期望一致。常用发方法和途径有以下三种。

(1)通过视图(波形窗口)检查。我们通过仿真器查看信号波形,这也是常用的方法,不过也存在缺点,对于复杂的设计,信号接口众多,数据量大,人眼视觉容易出现错误。

(2)自动化后处理对比。记录DUT的输出,通过运行脚本对比结果。我们可以将需要的结果写为文件保存,导入MATLAB进行对比分析。也可将期望得到的结果与DUT输出的结果通过程序自动对比分析。

(3)做一个实时监测器自动检查。当然,监测器需要进行开发,当对比发生错误时,通过设置错误标志和打印信息提示,便于快速发现错误,节省仿真时间。

在功能验证时,需要考虑主要功能点,提供比较完备的测试用例。对于FPGA功能模块的验证,或许用不上去搭建复杂的验证平台,但是这样的验证方法和思想依然可借鉴。在芯片设计领域,验证工程师作为独立岗位,承担着设计把关的重任,一旦投片,基本就决定这款芯片的命运了。

像笔者这样的FPGA工程师新手而言,主要任务就是算法实现。算法工程师把算法模型交给你,你就开始制定功能模块实现方案、与前后级商讨接口、RTL设计、仿真验证到上板调试。相对于数字IC工程师的独立性而言,FPGA工程师需要的技能也许更多:首先要懂算法,至少要理解算法处理流程;其次,常规技能要掌握,就是RTL设计能力;仿真验证能力,如何设计好的testbench来验证你的DUT,保证系统集成时不会有问题;最后还需要上板调试,需要掌握调试手段和验证分析能力,对整个系统需要比较熟悉,常常涉及射频和协议栈。隔行如隔山,精力也有限,因此挑战必然存在。

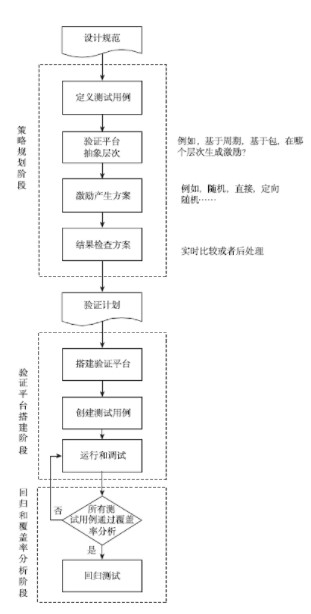

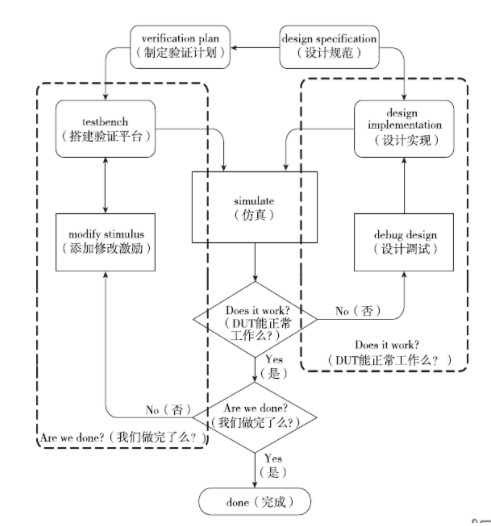

整个验证流程,我们通过下图来说明。

这里上图提到的回归测试和覆盖率收敛,对于小白或新手而言,可能比较陌生,尤其是对于我这样的非验证岗人员。

一旦几乎全部测试用例被成功执行,那么验证就进入了回归测试(regression test)和覆盖率收敛阶段。

回归测试要求能够周期的批处理运行,并且激励能够得到重现,成功或失败都能够自动检查。

这个时候,所有测试应该在每天或每周做回归周期性运行,查看覆盖率,解决可能存在的bug,尽可能实现覆盖率100%。

对于做FPGA的工程师而言,仿真时间太长,就不爽了。我们关心的是,功能验证和逻辑验证。覆盖率没有100%,也不要紧。不管是Vivado还是Quartus II自带的仿真器,或者Modelsim,都可用来做仿真。使用Modelsim做来联合仿真时,需要注意版本匹配和库文件编译。

验证技术和方法学

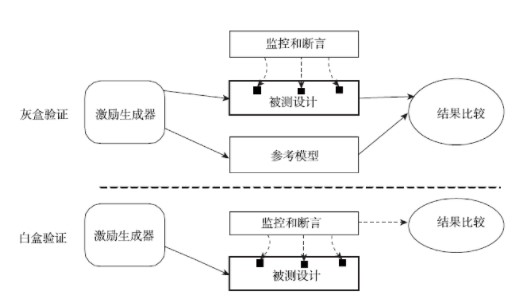

有三种常用验证手段:白盒、黑盒和灰盒验证。

三种主要验证技术:形式验证、仿真验证和硬件加速验证。

三种主要验证方法学:随机激励生成、断言验证和覆盖率验证。

做功能验证,目标就是验证设计能否能够像预期工作。然而,可能存在一些设计缺陷并没有在输出边界暴露出来,检测产生遗漏等。

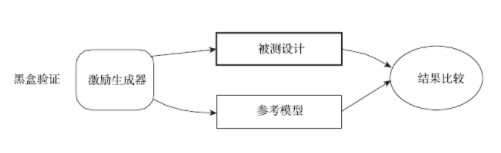

黑盒验证:只通过其边界信号来验证一个模块或设计的功能。验证模型:

黑盒验证有优点,也有缺点。优点就是看起来testbench搭建简单,缺点就是DUT内部错误不好验证。FPGA仿真验证,就类似这样。对于算法实现而言,常常利用FPGA仿真结果与MATLAB运算结果对比,比如画个图,画条线,数据相减,计算方差等等。内部逻辑则可通过观察波形来判断,局限于复杂度不高的情况。

白盒验证和灰盒则通过在设计内部或者外部输出信号放置监控器或断言来保证设计操作的正确性,不需要参考模型。

关于验证技术中的形式验证、仿真验证和硬件辅助加速验证等,其概念和使用方法,咱们不详细去讨论了,有兴趣的朋友,去找几本SystemVerilog验证的参考书看看。

在功能验证中,验证工程师面临着以下挑战:

完备性:最大限度验证DUT的行为,然而,怎样去获取必须被验证的场景,提高覆盖率。

可重用性:考虑如何优化验证环境架构,使其可在不同场景下重用。若每做一个工程或迭代更新一个版本,都需要重新去设计testbench,那会累死三军。

可靠性:在验证中减少手工操作,以减少认为错误和节省时间,然而,搭建一个自动化系统也并非易事,需仔细分析和搭建,同时采用约束随机进行验证。

效率:在给定时间内,对验证工作投入的产出最大化,提高验证的成功率。对于设计师而言,我们常常采用重用技术,比如某个通用模块,可在不同工程中使用,我们进行简单移植修改即可。然而验证就没有这么幸运了,场景不同,激励也不同,产生的结果也不同。

性能:验证程序性能上的挑战就是要如何最大化验证程序的效率。验证耗时费力,所以,每年在秋招春招时,大量芯片类企业招验证工程师。笔者去年秋招时,本来投递设计岗,然后当你笔试或者面试的时候,给你安排验证的岗位。

功能验证方法学,就是验证电子系统的技术和科学。

前面,笔者在《FPGA工程师的核心竞争力—方法篇(一、二)》中,总结了UltraFast设计方法学,从而有效提高设计和效率。

而对于验证这一环,也是有章法可循。

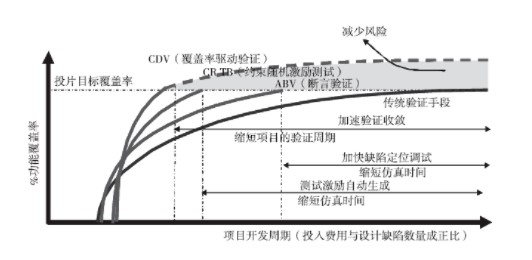

设计与验证,相辅相成,如下图:

DUT能正常工作吗?测试功能点是什么?怎么测?功能对不对?我们做完验证了吗?简直就是灵魂拷问。

在验证方法中,断言验证(ABV)、约束随机激励测试(CR TB)、覆盖率驱动验证(CDV)等技术将会极大提高验证效率。缩短验证周期,快速定位错误,加速激励生成和有效实现验证收敛。

对于FPGA工程师而言,在进行设计和仿真验证中,最常用的语言是verilog HDL或VHDL,各有千秋。verilog HDL用起来比较灵活,有C语言基础和硬件思维,就可以快速入门。VHDL语法严谨,有利于大规模系统集成。

SystemVerilog是业界新兴的工程语言,基于verilog HDL进行了扩展,包括对硬件建模的扩展和验证断言方面的扩展。

SystemVerilog具有以下优点:

(1)单一,同时支持设计和验证的标准语言。

(2)支持约束随机的产生。

(3)支持覆盖率统计分析。

(4)支持断言验证。

(5)面向对象的编程结构,有助于采用事务级的验证和提高验证的重用性。

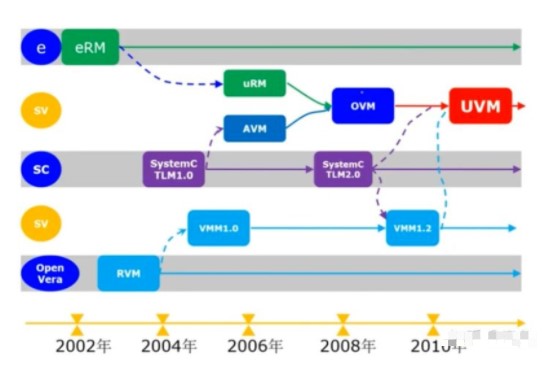

基于SystemVerilog的验证方法学有:OVM、VMM和UVM。目前,业界最流行的是UVM。相信你在或将会在今后的“金九银十”的秋招时,会被问到是否对UVM有所了解。如果你是看到本文了解到UVM这个概念,那么赶紧再深入了解一下。

下图是验证方法学的发展时间线:

UVM (Universal Verification Methodology)通用验证方法学。它起源于 OVM(Open Verification Methdology),其正式版是在2011年2月由Accellera推出的,得到了Synopsys、Cadence和Mentor的一致支持。UVM几乎完全继承了OVM,同时又采纳了Synopsys在VMM中的寄存器解决方案RAL。UVM继承了OVM和VMM的优点,克服了各自的缺点,代表了验证方法学的发展方向。

下图是典型的UVM验证平台框图:

由于SystemVerilog可完全兼容Verilog,所以你在.sv文件中加入几行Verilog语法的程序也不会出错。比如读写文件的操作,前几天,笔者也不了解这个SystemVerilog的用法,就在微信群里问这种小儿科问题:

“SystemVerilog和Verilog在读写文件操作上,有什么区别?”

$fopen,$readmemh/$readmemb,$fwrite,$fclose依然可用。

SystemVerilog中可操作字符串,这对于存储初始化文件(.mif)的读操作比较友好,并且可跳过文件中的注释。

SystemVerilog中信号定义,可用logic来代替Verilog中的reg和wire。

关于任务task的使用,文件指针等等,可以参阅SystemVerilog设计和验证的书籍,讲得很详细。

审核编辑:刘清

-

基于VMM验证方法学的MCU验证环境2014-03-24 3956

-

SystemVerilog 的VMM验证方法学教程教材2012-01-11 59507

-

[启芯公开课] SystemVerilog for Verification2013-06-10 8957

-

做FPGA工程师需要掌握SystemVerilog吗?2017-08-02 7099

-

验证方法简介2022-02-13 5780

-

基于SystemVerilog语言的验证方法学介绍2011-05-09 1097

-

基于SystemVerilog的I2C总线模块验证2011-12-22 544

-

SystemVerilog的正式验证和混合验证2021-03-29 932

-

SystemVerilog语言介绍汇总2021-10-11 3287

-

SystemVerilog对硬件功能如何进行建模2022-03-30 2778

-

利用Systemverilog+UVM搭建soc验证环境2022-08-08 1252

-

IEEE SystemVerilog标准:统一的硬件设计规范和验证语言2022-08-25 772

-

FPGA学习-SystemVerilog语言简介2022-12-08 3286

-

虹科分享 | 如何进行Mapping温度分布验证?概念、原理与方法(二)2022-07-19 2075

-

SystemVerilog在硬件设计部分有哪些优势2023-10-19 2516

全部0条评论

快来发表一下你的评论吧 !