介绍Xilinx的Polar Encoder IP核使用方法

今日头条

描述

随着5G 国际标准的出炉,Polar码顺利入选控制信道编码方案,世界上各大通信设备生产商便开始基于标准设计基站和终端产品。

我们明白,从纯算法到实现工程化,中间还有很长一段路要走。一方面,我们需要保证算法的性能良好;另一方面,便于硬件实现。本文将从Polar码编码角度,介绍Xilinx的Polar Encoder/Decoder IP核的使用方法。

按理说,我们应该分析Polar码的编码原理和算法构造,然而,专业性实在太强,定义、定理和公式及推导,以及算法性能比较及硬件实现方案,足够写出一篇硕士论文,甚至博士论文。因此,笔者不打算详细讲,包括里面的详细推导也需要花很长的时间,有兴趣研究这个方向的同学,可以多找几篇质量较好的论文研读。

目前也有一些硕博论文在研究和实现Polar编、译码,相信今后一段时期,还会有相关的研究成果问世。因此,若你还未走出象牙塔,拥有足够的时间去探索,去发现不一样的东西。若已经在工作岗位上,并正从事相关的研究设计工作,那么,笔者很乐意请教交流。比如,在开发过程中,会遇到哪些坑,有哪些需要注意,提高工作效率和缩短开发周期。

本文是笔者的一个学习笔记,主要是利用Xilinx公司的Polar IP核进行应用开发,并介绍MATLAB软件中的关于Polar编码的函数。

由于所用的IP手册通常是需要购买了Xilinx公司或第三方厂家的IP 核才会提供相关的文件资料,因此,想获取公开的关于5G信道编码的IP核资料比较难。

先介绍干货,关于资料的问题,在后面谈。

Polar IP介绍

Xilinx提供的Polar Encoder/Decoder IP v1.0支持Polar编码和译码。Polar码可配置,基于逐块使用。关于该IP的详细介绍,可参考文献[1]-[2],本节做简要介绍。该IP支持的器件:UltraScale、UltraScale+和7系列。注意,在本文中,块是由编码器或解码器处理的数据基元单元的通称。码字是已编码块的特定形式,在讨论用于生成它的代码参数时使用。

根据IP产品指南,Polar Enocder/Decoder IP核,在400MHz时钟频率下,最高吞吐量如下:

Polar解码器:>80Mb/s(N=1024,K=200)

Polar编码器:>700Mb/s( N=1024,K=200)

这里,K是输入信息bit长度,N是输出码字长度。

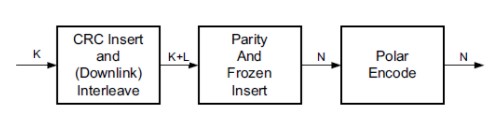

前向纠错(FEC)码(例如Polar码)提供了一种方法去检测核识别纠正不可靠或嘈杂通信信道上的数据传输错误。根据5G NR物理层协议,Polar码的编码过程,如图所示。

前级的传输块信息bit,插入CRC校验,下行链路还需插入交织,奇偶校验及冻结bit插入(非必须),再送入编码器进行编码。

特性总结:

Polar Encoder/Decoder IP核是一个高度灵活的软判决实现为Polar码提供以下特性。

Decoder执行列表大小为8的串行抵消列表(SCL)解码,根据3GPP TS 38.212 V15.1.1,通过奇偶校验和/或CRC比特来增加比特。

能够基于逐块或传输指定输入和输出数目。

通过AXI-Lite接口最高支持配置128个代码。

逐块选择代码。

码字大小从N = 32到N = 1024,K从2到N,交织时Kmax为140。

作为编码器,内核接受K bit信息,并输出N个编码bit。作为一个解码器,内核接受N个软值对数似然比(LLR),并输出K个硬判决bit。

解码器接受8bit软值LLR输入,并假设饱和对称。

仅支持按顺序块执行。

输入输出宽数据接口。

单独的输入和输出流允许提供控制参数和状态逐块地进行。

应用领域:

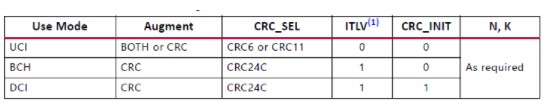

例如5G无线,参考3GPP TS 38.212 V15.1.1 Multiplexing and channel coding(Release 15),支持DCI、UCI、和BCH。Polar使用模式设置,如下表所示。

注意,这个表很重要,很重要,特别是对于使用该IP核进行应用开发的朋友而言。

产品规格

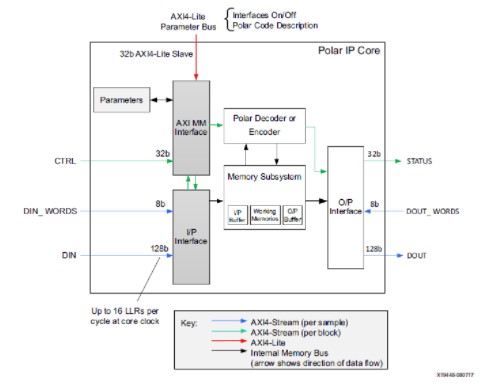

Polar编码器/解码器Core的框图如图所示:

该Core使用AXI接口。AXI4-Lite存储器映射总线用于参数(例如Polar码定义)持续缓存多个块,AXI4-Stream接口用于逐个样本提供数据(例如,DIN)基于逐块的配置(例如,CTRL)。这些接口处理提供数据外,还提供握手信号。

每个块通过数据输入接口(DIN)在多个周期内输入。在每个周期中传输的数据率由一个单独的数据流(DIN_WORDS)来设置,其中DIN上的每个事务都有一个值。输出是以类似的方式在DOUT输出流上生成,在输入数据流DOUT_WORDS上指定了传输的数据量。

对于每个块,在控制(CTRL)输入流上需要一个输入,指定要使用的代码和用户提供的ID字段。每个数据块需要一个控制字,数据输入暂停,直到相关的控制字可用为止。当解码(或编码)时,DOUT接口输出数据伴随着状态(STATUS)输出接口上的状态字一起输出。

该图包含了非常丰富的信息,对于从事IC设计或FPGA开发的朋友来说,这样的框图看到过太多太多,我们在论文里或者设计报告里,经过要这样画一个框图。

这里面包含了接口、内部功能单元及必要的图注。通常,箭头方向指明数据流向,左边是输入端口,右边是输出端口,但不是绝对。

为便于集成和操作,IP核通常采用业界标准接口,例如上图中给出的AXI4-Stream、AXI4-Lite等。

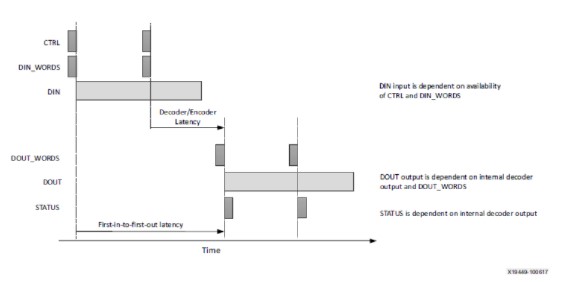

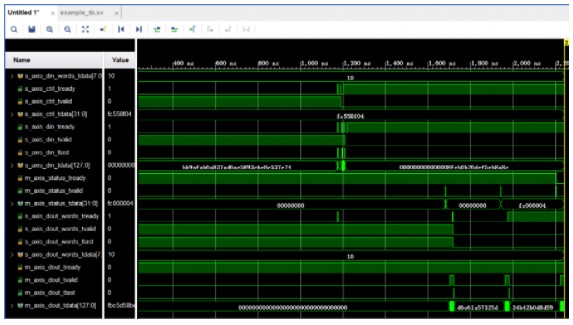

所有AXI4-Sream接口包含用于流控的valid 和ready握手。上图中,数据依赖关系,如下图所示。

根据图示可知,输入DIN上数据输入依赖于CTRL和DIN_WORDS,DOUT输出的数据依赖于内部解码器输出和DOUT_WORDS。CTRL的输入与DIN_WORDS的相关输入之间存在延时,并且DIN被接受,需要通过通道上的tready来断言。同样,DIN_WORDS与DIN也存在延时。如果要最小化DIN上的延时,那么CTRL和DIN_WORDS应该提前提供。同样,在输出端,为了避免输出DOUT延迟,若有必要,应该尽早驱动DOUT_WORDS。接口有浅缓存,在CTRL上提供相关的块控制之前,DIN和DIN_WORDS上在允许输入少量数据。

当我们拿到这样的IP指南时,首先就要先看看这个IP能够实现什么功能,适用于哪种协议或标准,IP核端口及信号定义,以及重要的注释信息。

对于通用的FIFO、RAM等,会用即可。难点在于根据某些标准协议或算法而有针对性开发的IP核,通常应用起来也要花一些时间去看文档,并了解背后的协议和算法。例如,对于应用于5G信道编译码的Polar IP和LDPC IP,涉及标准协议和一系列参数配置,并不像使用一个FIFO那样简单。

更多关于端口描述和寄存器空间的内容,请参阅参考文献[2]。这里不再占用篇幅和时间码字了。

Polar Encoder IP应用

本节内容,是大家最为关心的,拿到资料后,我们初步了解了这个IP是干嘛的,有什么特性,有哪些端口,如何利用该IP进行设计,流程是什么,怎么仿真验证。

这里,假设你已经看完了产品指南的资料,你已经迫不及待准备开始动手了。

然而,你却迷惑了:我有Polar 编解码 IP的license吗?我该用哪个版本的Vivado设计套件?我如何去写一个testbench来验证,我的参考模型在哪里?

关于Polar IP license的问题,解决办法有两个:

(1)若你已经入职,那么找你项目组的负责人,他会想办法去购买,买回来就可以用了;

(2)若你还在求学,然而导师想让你研究Polar码,要自己动手去进行硬件实现,你想找个参考和性能对比对象,然鹅没有足够的资金去购买一个IP,并且很不值得,那么你可以去Xilinx官网申请一个评估版的license进行试用。

然后进去申请一个免费的评估license,可以搜索你想申请的license。一般需要你注册,并且提前准备好你主机的MAC地址,以备填写信息所用。

关于Vivado设计套件版本的问题,看哪个版本支持5G等开发就用哪个,笔者用的是Vivado2018.3。

关于如何写testbench的问题,这个问题确实很重要,也有很多参考书和博客在比较详细的介绍。前面的文章《SystemVerilog与功能验证方法学》提到过关于testbench验证平台的问题。我们要注意的是,测试激励的产生以及对DUT输出结果的检测。首先为DUT提供输入信号,用逻辑和存储文件产生必要的信号;其次,要注意各端口测试激励的时序关系,应根据DUT的需求进行设计;最后,对于DUT的输出,我们可以进行写文件操作,保留仿真产生的结果,便于数据分析。

对于参考模型,我们常用的就是MATLAB链路算法模型。例如对于Polar的编码,MATLAB中提供了库函数nrPolarEncode,该函数是根据5G NR标准协议编写的,可直接调用。

万事俱备,只欠东风。我们把申请好的license加入到license管理器中对应的路径后,更新确认是否可用。

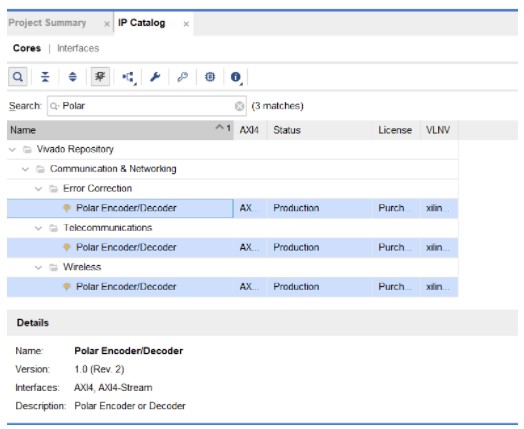

新建一个工程,通过Vivado的IP目录,我们轻松找到Polar IP核:

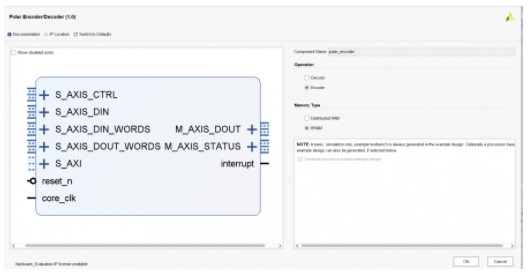

然后进行简单的配置,例如选择进行编码,存储资源类型可以选DRAM或BRAM。“OK”后导出IP核,综合方式可以选全局或者OOC,默认是OOC方式。

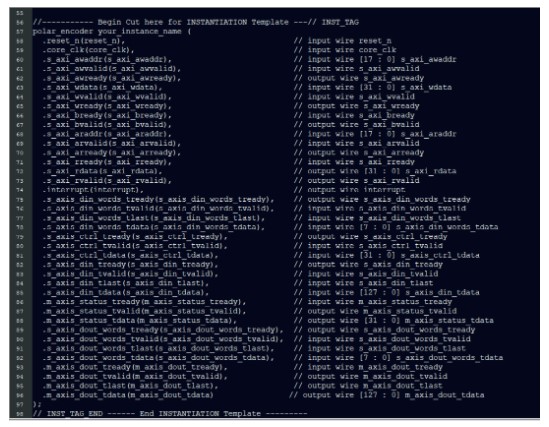

然后我们将IP的例化文件复制粘贴到工程的v文件中,并定义好集成的模块名。

当我们例化好IP 核后,将必要的input和output 端口通过顶层文件进行定义。

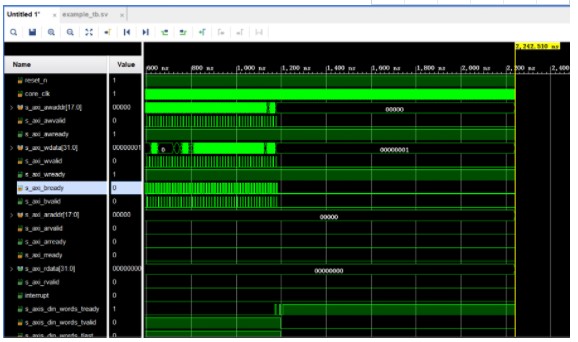

接下来,就着手编写testbench了。当你不知道怎样去写一个令人满意的验证IP 的testbench时,你可以在IP sources栏,选择该IP,右键去选择“Open IP Example Design”打开IP的例程,查看例程的testbench是怎样写的,并且可以直接进行仿真。当然,你也可以自己编写一个testbench。

跑个例程是很简单,然鹅,你的目标可不是跑个例程就结束了。

这里在应用Polar 编解码IP核时,最重要的是什么呢?其实是根据实际情况去配置参数寄存器。

当时笔者也是没搞懂这个寄存器到底应该怎样去配置,才能得到想要的结果,每次以为已经按照指南操作了,可是编码结果就是和MATLAB中的结果对不上,对不上,你绝望吗?

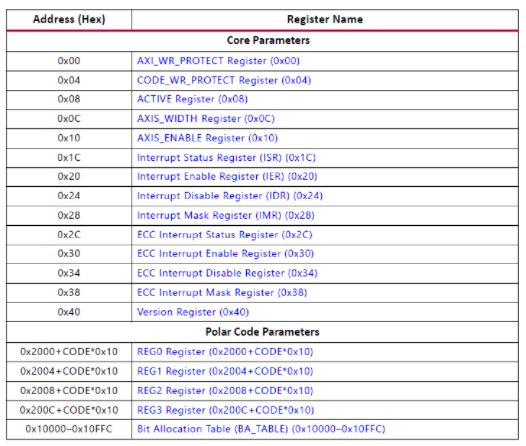

没错,笔者要说的就是下面这个寄存器空间。

当仔细看完IP指南后,笔者还是很懵的。直到尝试了好几天,才终于搞定了。期间,甚至去Xilinx论坛提问了,当我已解决后的某个周末,论坛回邮件了。当然我只是问了一个不是最重要的问题,而是一个非常普通的不算是问题的问题,因为指南里其实已经说了,只是当时已经怀疑自我了。

在指南里,上面这个表的每一个地址及对应的配置参数,都有说明,然鹅,当你看到上表的最后一行,你会很困惑:这个位分配表我哪里知道?!

当初笔者天真的以为,假如按照输出的码字全是信息bit,自己去造一个位分配表,然鹅,还是太年轻。

仿真过几次,不对啊。

然后又去Xilinx官网找资料,找到了参考文献[3],并且通过文中的连接,获取了一份重要的C模型和MATLAB模型的代码,这个文档就是介绍如何去造位分配表。而C模型和MATLAB代码,正是在下苦苦寻找的位分配表的产生来源。

要说,这个位分配表,是依据协议来产生的,IP核利用了寄存器映射,指明输出码字每一位的类型:冻结位、信息位、CRC位、奇偶校验位。

依据这个MATLAB代码,笔者根据实际参数进行配置,然后产生了位分配表,再把这个表写入MIF文件,通过testbench读取并写入IP核的参数总线。最后,编码输出的结果终于和MATLAB对上了!

注意,MATLAB的版本最好是2019a/b及以上。

对比结果就不贴图了,本来这篇水文是不能写出来的,在不涉密的情况下,我只能这么水水的描述一下,以飨读者。

在整个Polar Encoder/Decoder IP核的开发应用中,需要注意以下几点:

(1)确定参数配置方式,最好采用可编程方式配置;

(2)对于DIN_WORDS、CTRL、STATUS、DOUT_WORDS端口输入,要结合前文提到的数据接口依赖关系;

(3)对于不同的信道(如PBCH,PDCCH),IP核的配置不太一样,仔细看IP指南和本文提到的很重要很重要的那个图表。

如果你有足够的时间,完全可以自己动手去开发一个Polar IP核,挂在网上,说不定可以卖出好价钱。

今天就到此为止,本文介绍得不是很详细,但笔者遇到的那些坑,基本上指出来了,希望对读者朋友有帮助。

审核编辑:刘清

-

jf_25224524

2024-08-05

0 回复 举报您好,没有看到参考文献的信息,可以再发以下吗 收起回复

jf_25224524

2024-08-05

0 回复 举报您好,没有看到参考文献的信息,可以再发以下吗 收起回复

-

chaoweilm

2022-09-13

0 回复 举报您好,我这polar的评估版的license申请不下来,请问可以分享一下吗?万分感谢! 收起回复

chaoweilm

2022-09-13

0 回复 举报您好,我这polar的评估版的license申请不下来,请问可以分享一下吗?万分感谢! 收起回复

-

如何申请xilinx IP核的license2024-10-25 2725

-

FPGA学习笔记:RAM IP核的使用方法2023-08-29 5933

-

FPGA学习笔记:ROM IP核的使用方法2023-08-22 7932

-

Xilinx Vivado DDS IP使用方法2023-07-24 8935

-

Gowin MJPEG Encoder IP用户使用指南2022-09-30 711

-

Gowin MJPEG Encoder IP用户指南2022-09-15 696

-

Xilinx-DCM的使用方法技巧2021-09-28 1167

-

Xilinx原语的使用方法2021-02-22 2456

-

xilinx的Chipscope的使用方法2018-01-12 7786

-

xilinx原语使用方法2017-10-19 1340

-

xilinx 原语使用方法2017-10-17 1341

-

Xilinx系列FPGA芯片IP核详解2017-06-06 31280

-

Xilinx Vivado的使用详细介绍(3):使用IP核2017-02-08 3176

-

xilinx FPGA的FFT IP核的调用2016-12-25 6543

全部0条评论

快来发表一下你的评论吧 !