浅谈闪速存储器和存储单元连接方式

存储技术

描述

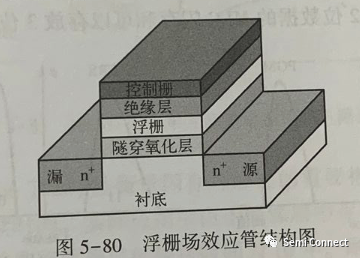

闪速存储器(Flash Memory)又称闪存(Flash),是一种非易失性存储器,用存储单元阈值的高低表示数据。浮栅(Floating Gate )场效应管(见图5-80)是Flash存储单元采用的主要技术。浮栅上的电荷决定了场效应管的阈值:编程通过量子隧道效应将电子注入浮栅阈值增大,代表逻辑“0”;擦除则相反,将电子从浮栅中提出,阈值减小,代表逻辑“1”。

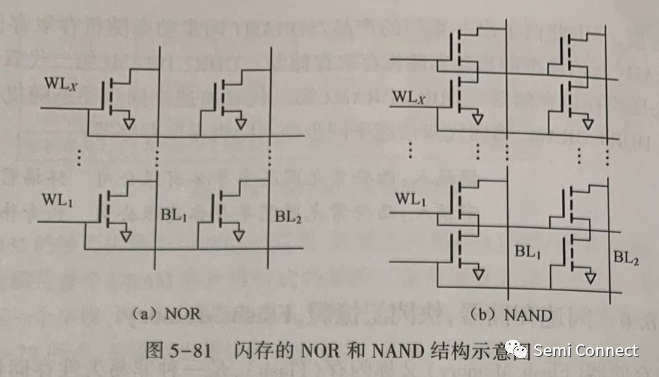

按照存储单元连接方式的不同,闪存分为或非闪存(NOR Flash)和与非闪存(NAND Flash)两种,它们的存储单元阵列如图5-81所示。NOR Flash 单元并联连接,比NAND Flash单元面积大容量小。NOR Flash的操作类似于SRAM和DRAM,可以实现快速随机读取,所以多用于代码存储。NAND Flash单元串联连接,成为一个存储单元串,减少了接触孔的数量。NAND Flash平均单个存储单元的面积接近4F2(F为工艺特征尺寸),比NOR Flash 集成度更高,多个存储单元串构成存储单元块。NAND Flash 的擦除操作以块为单位进行,其读操作和编程操作以页为单位进行,非常适合大容量的数据存储应用。NANDFlash普遍用在智能手机、数码相机、MP3等电子产品;还可用来实现固态硬盘(Solid State Drive,SSD),作为硬盘的替代品,具有抗振、速度快、无噪声、耗电低的优点。

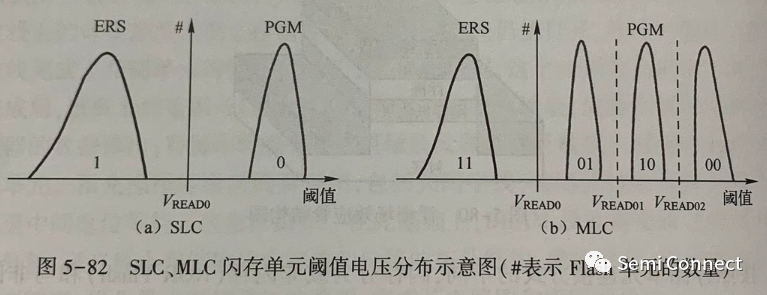

按照单个存储单元存储数据位的多少,Flash分为SLC、MLC、TLC等。SIC 、MLC闪存单元阈值电压分布示意图如图5-82所示。SLC闪存的1个Flash单元存储1位信息。为了实现更高的存储密度,多电平(Muti-Level)闪存单元将阈值电压编程为多个电平,1个场效应管可以存放1位以上的信息。目前已经实现了1个闪存单元可以存放2位数据的MLC闪存和可以存放3位数据的TLC闪存。

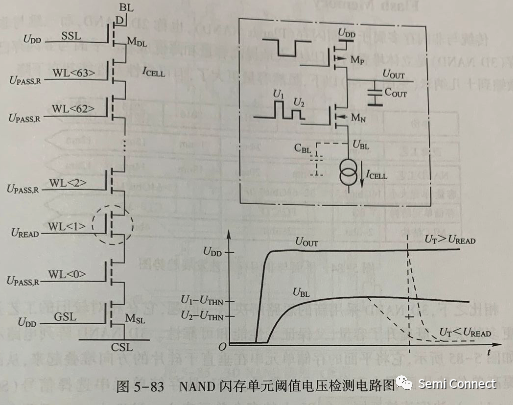

闪存存储单元所能存放的位数取决于阈值电压能被编程和被检测的精度。存储单元的阈值电压通过调整被选字线上的电压进行检测。不同的字线电压会导致位线流过存储单元的放电电流ICELL不同,通过识别电流大小即可判断阈值的大小。NAND闪存单元阈值电压检测电路如图5-83所示。首先,节点UOUT充电至UDD,并通过场效应管MN、对位线进行充电。由于MN的栅极电压为U1,所以位线充电至电压U1-UTHN,UTHN为阈值电压。然后,MN关闭,节点UOUT停止预充。存储单元串打开后位线开始放电,此时选中单元的字线电压为UREAD。最后,MN栅极电压为U2。此时如果UBL

保持时间(Retention Time)是衡量闪存可靠性的重要指标之一,表征了 Flash单元能保持数据的持续时间。实际应用中由于绝缘层中存在缺陷,浮栅上的电荷会逐渐泄漏。目前制造商通常规定的保持时间为10 年。耐久性(Endurance)是闪存设计的重要挑战,由于栅氧层在多次高电压操作后会逐渐损坏,并且随着工艺特征尺寸的缩小,相邻浮栅单元之间的耦合干扰愈发严重,一个单元能被擦除和重新编程的次数是有限的。目前,SLC耐久性的典型值为10万个擦除/编程周期,MLC的耐久性可低至1万个擦除/编程周期甚至更低。针对这些挑战,一方面通过工艺进步提升存储单元本身的耐久性,比如电荷俘获型(Charge Trap) Flash存储单元克服了浮栅单元之间的耦合干扰,使得Flash技术在平面可以继续微缩至十几纳米;另一方面通过芯片设计的改进降低阵列操作对存储单元的磨损,包括调整高电压操作的电压值以及时间长度,引入验证和禁止编程机制等。

编辑:黄飞

-

闪速存储器是u盘吗,闪速存储器一般用来做什么的2025-01-29 1838

-

存储器对全部存储单元刷新遍所需的实际刷新时间是多少2021-10-26 7345

-

MOS存储单元的工作原理2021-07-28 2061

-

存储单元结构2020-05-14 4521

-

单片机与闪速存储器的软硬件设计的注意事项2020-04-04 1861

-

单片机与闪速存储器的接口电路的注意问题2019-05-28 1560

-

NAND 闪速存储器的内部结构2018-04-11 2353

-

闪速存储器的概要2018-04-10 2852

-

闪速存储器的分类及特征2018-04-09 3067

-

基于OTP存储器存储单元读取阀值2017-11-07 2386

-

闪速支持芯片的PSD设备和闪速存储器在嵌入式系统中的设计2009-05-13 373

全部0条评论

快来发表一下你的评论吧 !