使用架构仿真延长消费产品的电池寿命

描述

对于消费类应用,响应时间、显示分辨率和电池寿命是最重要的特性。电池的生命周期与其容量、功率峰值和使用情况成正比。由于成本、空间和可靠性方面的考虑,电池尺寸不能随意增加。半导体功率损耗取决于电容、线负载、栅极、电源电压、信号转换和泄漏电流。系统电源以显示器、触摸电容、处理器和内存为中心。处理器和处理系统(如单板计算机、电子控制单元 (ECU) 和高性能计算)的延迟、吞吐量和热设计功率 (TDP) 是产品设计的驱动标准。降低功耗时首先想到的算法是电源门控,当没有任务执行时关闭设备或网络的技术。由于对安全、时间期限和实施成本的影响,建议比部署更容易。

对于任何新系统,电源状态的数量、并发线程操作、转换时间和切换都需要在最终确定规范之前进行详细的电源评估。此外,规范必须在性能、功率、功能和有时可靠性之间进行权衡。当今系统上的处理选项、接口容量、应用变化、显示系统和其他 MEMS/机械系统使得使用 Excel 等分析方法预测功耗变得非常困难。功率测量需要结合资源和周期精确模型来做出具有极高发生概率的预测。

使用来自 Mirabilis Design 的VisualSim等软件包的系统级建模,或 C++ 中的事务模型,长期以来一直用于探索电子和半导体的性能。VisualSim 等图形建模环境允许对系统进行交互式评估,而编程语言则提供更大的开放性。这些模型将定义资源、硬件、调度程序、流量、用例和网络。硬件平台的周期精确定义不是设计过程早期的主要考虑因素,认为可以随着评估范围的缩小添加它以回答特定问题,例如周期性刷新对 1X 或 1X 时功耗的影响2X。在这个时序模型中,VisualSim 添加了功率探索,从而提供完整的系统分析解决方案。

VisualSim 是一种基于模型的系统仿真软件,它使用基于组件的建模方法加速开发并提供大量报告。该系统可以是处理器、片上系统、自动驾驶辅助系统、飞行航空电子设备或冒险相机。建模组件可以是资源、FPGA、分立组件、电气系统、MEMS、处理器、基于分布的流量生成器、硬件外围设备和软件任务图。资源是消耗时间或数量的子系统。资源的示例可以是万向节电机或加速度计。

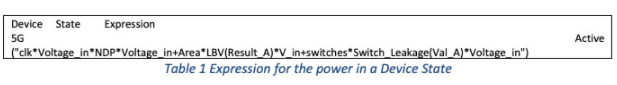

要将功耗分析纳入系统级仿真,系统模型必须包含每个设备的每个状态的功耗。功率数可以是电压、面积、开关、泄漏和 LDO 效率的值或组合。电源状态值的示例如表 1 所示。

该模型必须包含转换的影响,并随着用例和设备上执行的流量的变化而动态地从一种状态移动到另一种状态。对新状态的更改可以是开始新的执行,在一段时间不活动后进入深度睡眠,执行低优先级与高优先级的用例以及特定条件,例如内存激活和刷新。功率表达式值必须随时钟速度和温度等时序属性而变化。

功率分析从一个表格开始,该表格描述了状态和状态机处理管理中的功率表达式。模拟器或 VisualSim 事件日历必须支持基于时间的功率测量、每个资源和设备随时间的动态状态变化,以及基于应用程序和用户活动的状态之间的转换。电源管理器将包含带有变量的复杂表达式,以定义每个状态下的电源。这些表达式可以包含泄漏、面积、电压水平和应用任务之间的差异。这些变量可以包括时钟速度、启用的开关数量和捕获线长度的抽象——延迟和泄漏。蒙特卡罗模拟可以捕捉抖动、随时间的变化、用例、软件配置文件和流量分布。

有功功率表是架构探索的重要参与者,负责收集、向电池提供输入并处理电池的充电需求。生成的统计数据包括组件的能耗、系统的累积功率、瞬时负载、平均负载和每个组件的状态消耗时间线。

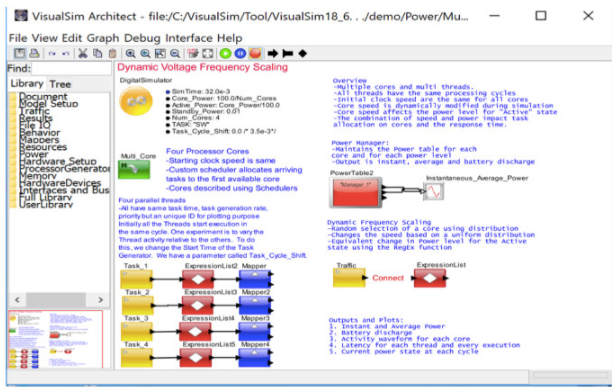

系统级功耗探索可以评估各种降低功耗和低功耗技术的优点和节省的能量。在这里,我们讨论这些技术并使用 VisualSim 中的仿真模型解释它们的影响。出于本研究的目的,我们使用四核处理器、调度程序代替实时操作系统、四个并发线程和按顺序触发处理资源上的线程的中断。我们已将模型参数化为内核的可变时钟速度、1 到 4 之间的可变内核数量以及线程触发之间的偏移。此外,我们还结合了电压和时钟速度动态变化的逻辑。与此描述相关的框图如图 1 所示。

图 1:多核架构和四个并发线程的系统级框图

进行了以下实验,我们查看了每个场景的延迟和功耗。

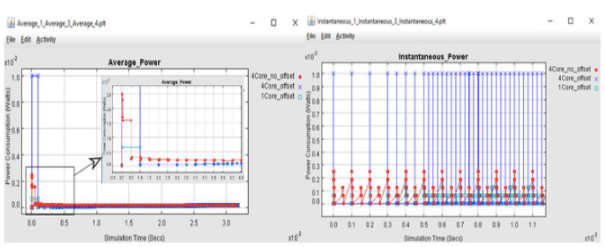

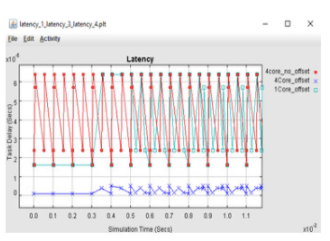

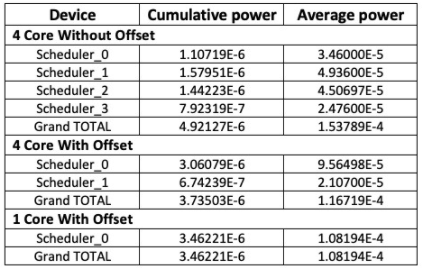

偏移并发任务:有四个任务,默认情况下这些任务同时触发。在这个实验中,我们将每个任务移动了 3.5 毫秒。这样,任务就不会同时开始。正如我们从图 2 中看到的结果,这种方法降低了功率尖峰。最大峰值从 1.0mW 到 7.5mW,节省 25%。从图 3 来看,延迟确实从 7 毫秒减少到 0.5 毫秒,这是一个显着的改进。从图 2 和表 2 中有趣的推论是,所有四个内核都不再被使用,并且在处理资源的任务请求中只是偶尔重叠。对平均功耗没有影响。

比较以 1GHz 运行的单核与以 250MHz 运行的 4 核:在本实验中,我们将所有任务定位在以 1GHz 速度运行的单核上。我们使用线程的偏移量。图 2 的结果显示瞬时功率和平均功率均显着降低。从图 3 中我们可以看到延迟图没有显着影响。您可以看到峰值功率与 1.0mW 的非偏移值相同,但平均功率减半至 0.15mW。这是因为处理速度有相当大的浪费。

图 2:LHS 显示了一段时间内的平均功率。RHS 显示随时间变化的即时功率。

图 3:随时间变化的延迟。

表 2. 上述实验的累积和平均功率

任务中一个有偏移的核心的累积和平均功耗小于有和没有偏移的四个核心。

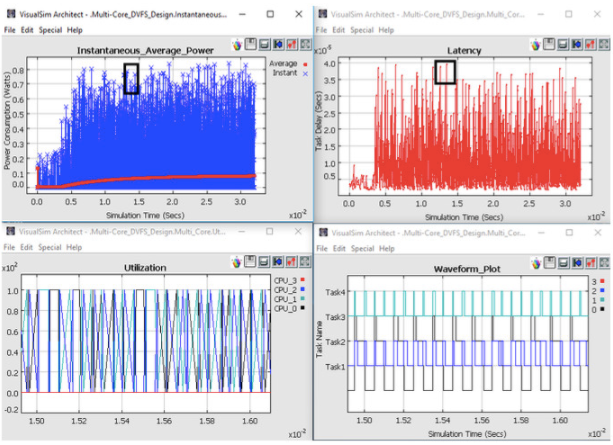

动态电压频率缩放 (DVFS):这是节省电力的首选技术,可根据任务要求改变时钟速度。一个很好的例子是 x86 处理器,它的额定频率为 3.2GHz,但在笔记本电脑上以 1.8GHz 运行。使用原型板,当电压频繁调整时,很难预测任务的延迟。在相关模型中,我们没有实现特定的算法,而是看到在很宽的时钟速度范围内功率和延迟的变化。结果如图 4 所示。我们在这次运行中使用了四个内核和四个偏移线程。请注意,功率和延迟会因时钟速度的变化而波动。延迟保持与原始偏移版本相同。DVFS 帮助我们大规模降低功耗。

图 4:具有四个并发线程和每个内核中不均匀时隙任务的四核的动态电压频率缩放中的功率、延迟和利用率变化

从图 4 中我们可以看到,对于较高延迟的任务(功率图中的黑框),瞬时功率较小,反之亦然。这说明了 DVFS 的功能,其中时钟速度对于小型处理任务会降低,这反过来会增加延迟并降低功耗。

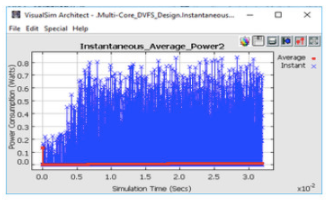

图 5:通过实施电源管理降低平均功率

在特定时间段后强制内核进入待机状态将降低功耗。从图 5 中我们可以看到实施电源管理后功率有所降低。

扩展 DVFS 示例,可以修改每个任务的开始和频率。分析生成的统计信息,我们可以看到正在使用的内核数量减少了(core_3),从而消除了额外的待机功耗并降低了功耗。如您所见,同时探索电源选项和软件调度非常重要。这将确保所需的响应时间,同时降低功耗。

电源门控:这是在一段时间不活动后将处理单元移动到较低功率状态的过程。一个常见的例子是笔记本电脑从活动到待机再到睡眠和休眠。在这个模型中,我们将电源门控状态机逻辑添加到电源表中。我们将空闲状态的延迟设置为 10us,将转换时间设置为 1us。设备在待机状态下停留的时间较短。从图 5 中我们可以看到,只要内核处于非活动状态,内核就会将其状态从待机更改为空闲。过渡时间对延迟的影响最小到零。

图 6:电源门控,其中内核在 0.1ms 不活动时从待机移动到空闲,转换时间为 1.0us

结论:

系统级仿真可用于半导体和系统级的广泛功率分析。将功率探索与性能研究结合使用可确保同时进行权衡,从而确保更高质量的产品。许多功率研究可以在产品实施之前在系统级完成,并消除集成过程中的所有意外。这项研究的另一个好处是热和机械工程师获得了完全验证的数据,而不是近似的最佳判断信息。将性能和功耗分析集成到单个系统级模型中的 VisualSim 等软件工具有助于更快地构建模型,使用较少的模型集减少模型维护,并在设计周期的早期进行更高质量的探索。

每个任务中偏移的含义提供了功耗和延迟的减少。

减少内核数量并提高处理器速度可以显着降低功耗。

根据任务要求改变内核的时钟速度是降低系统功耗的最佳方法。

在非活动期间使内核空闲可减少系统中的电力浪费。

审核编辑:郭婷

-

能量收集技术延长电池寿命2016-03-02 0

-

延长锂电池使用寿命的方法2017-09-15 0

-

超低功率8位微控制器延长电池使用寿命2019-07-25 0

-

开关电源的电池寿命怎么延长?2019-09-18 0

-

如何延长电池寿命?2021-05-12 0

-

如何延长蓄电池的使用寿命?2021-06-18 0

-

资料下载:凯利讯的能量收集技术延长电池寿命2021-07-05 0

-

自制电池寿命延长器2022-08-16 0

-

如何延长干电池使用寿命2009-11-07 1461

-

延长充电电池寿命的秘诀2009-11-04 875

-

怎样延长电池寿命2009-11-13 783

-

如何有效延长电池寿命2020-05-30 2221

-

如何延长电池的使用寿命2022-01-23 5382

-

使用架构仿真延长消费产品的电池寿命2022-07-24 712

全部0条评论

快来发表一下你的评论吧 !