特高频局部放电检测仪的设计方案

电子说

描述

摘 要:根据电力变压器特高频局部放电信号特征,文中设计一种基于FPGA+ARM 架构的特高频局部放电检测仪。该架构通过利用 FPGA强大的可编程能力,不仅大大减少了硬件设计的复杂度,而且还提高了整个系统运行的速度,同时在FPGA 中创新性地设计了可以灵活控制VGA 大小的DAC8562模块及可灵活控制滤波程度的FIR滤波器模块,为在复杂的环境中快速有效地检测出局放信号提高了保障。利用ARM芯片强大的数据处理能力对数据进行处理及多重参数的配置,从而快速准确地检测出特高频局部放电。最后,通过系统测试,文中设计的特高频局部放电检测仪具有极好的稳定性,能够满足工程实际需求。

0 引 言

提高变压器设备运行可靠性,及早发现电力设备在实际运行过程中的故障与风险,对于电网的安全稳定运行有着极其重要的作用。根据相关研究结果表明,电力变压器中绝缘故障所占比达到了50%以上,是造成电力变压器故障主要的原因之一[1]。

目前,常用的局部放电检测方法主要有脉冲电流法、超声波检测法和特高频检测法。然而,脉冲电流法需要进行离线检测,超声波信号在各种介质中传播会产生较大的衰减和畸变[2]。文献[3]中虽然采用了特高频局放检测,但其局放信号是采用高速数据采集卡进行局放信号采集,设备成本高。因此,本文采用FPGA+ARM架构进行特高频局部放电检测仪设计,不仅降低了系统硬件设计的复杂度,还减少了系统内部资源的消耗及成本。同时,有效地利用了FPGA强大的可编程能力和ARM 强大的数据处理能力优势[4]。最后,在 FPGA中创新性的设计了可以灵活控制VGA大小的DAC8562模块及可灵活控制滤波程度的FIR滤波器模块,为在复杂的环境中快速有效地检测出局放信号提高了保障。

1 特高频局部放电的硬件设计

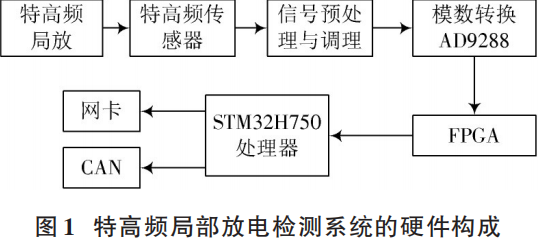

特高频局部放电检测仪的硬件主要包括信号预处理单元、信号调理单元、A/D采样单元、FPGA单元和ARM单元。当变压器发生局部放电时,会产生超高频的电磁波,特高频传感器接收后经转换输出为微弱的电压信号。首先,特高频局部放电检测仪前端硬件电路包括对微弱的电压信号进行滤波、放大、检波预处理;接着,对检波后的电压信号进行调理后经高速ADC芯片转换成数字信号,FPGA将采集到的数字信号存入外扩SRAM;最后,ARM处理单元将来自SRAM的数据进行分析处理,并与上位机进行通信,实现对特高频局放的存储与在线监测。检测系统硬件结构如图1所示。

1.1 信号预处理

由于局部放电辐射到空间的电磁波极其微弱,特高频传感器耦合得到的信号幅值很小。因此,首先要对信号进行放大处理。同时,由于特高频局放的信号频率在 0.3~3 GHz 范围内[5],为了避免低于0.3 GHz和高于3 GHz信号的干扰,需要设计带通滤波电路。再者,由于特高频传感器的输出信号的频率很高,如此高频率的信号只有高速示波器才可以采集。为了节约成本,本系统采用是先对其进行包络检波降频,然后再对其进行信号采集。包络检波是指检波器输出电压反映高频调幅信号包络变化规律的过程[6]。

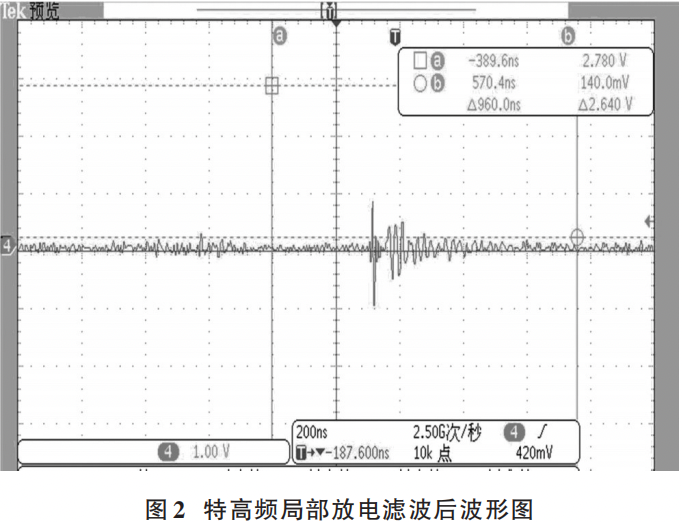

由于包络检波后可以保证AD9288 能采集到局部放电脉冲的峰值和相位,而对于局部放电的检测往往关心的是脉冲的幅值和相位,因此检波后的信号依然可以反映局部放电的特征。在实验室的条件下,采用电火花打火器在特高频传感器周围进行打火,打火后产生的电磁波经特高频传感器转化为电压信号,实验结果如图2所示。由图可知,发生放电时,产生了高达上GHz的mV级的电压信号,且其频率周期是 ns级别。

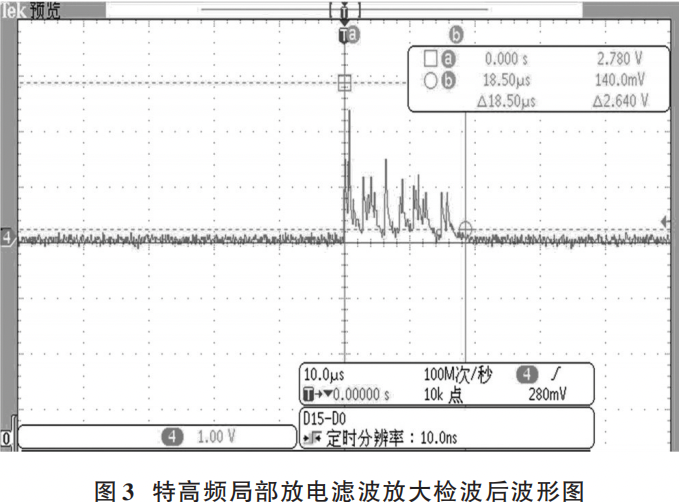

将信号继续接上设计的放大检波模块后,实验结果如图3所示。由实验结果可知,微弱的电压信号得到了明显的放大,已经达到了V级别。并且检波模块达到了很好的降频效果,其频率周期降到μs级别,为后期的A/D采样芯片的选型提供了可能,大大降低了后期数据采集的难度。

1.2 信号调理

1.2.1 电压跟随器

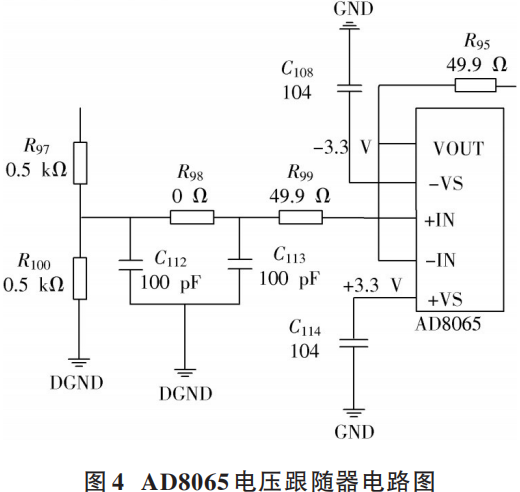

电压跟随器具有很高的输入阻抗和很低的输出阻抗,是最常用的阻抗变换和匹配电路,作为整个电路的高阻抗输入级,可以减轻对信号源的影响,作为整个电路的低阻抗输出级,可以提高电路带负载的能力。本设计中选用AD8065作为电压跟随器,它具有失调电流小、速度快的优点[7],很好地抑制了局放信号的衰减,将前级检波后的局放信号很好地与差分放大器连接到一起,起到承上启下的作用,很好地解决了前后电路阻抗匹配的问题。

电压跟随器电路如图4所示。

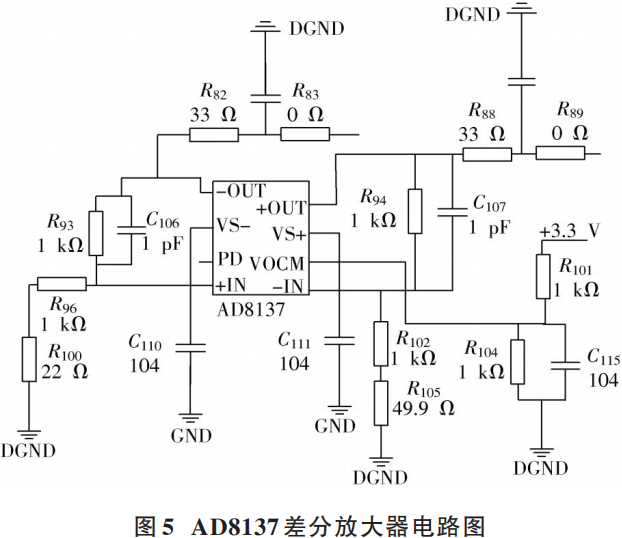

1.2.2 差分放大器

本文选用AD8137作为差分放大器,它具有低噪声、低失真和宽动态范围等优点,非常适用于要求低功耗和低成本的系统[8]。差分放大器把原来的单端信号变成了差分信号,为后级的程控放大电路需要差分信号提供了可能,同时使信号的抗干扰性得到了增强。差分放大器电路如图5所示。

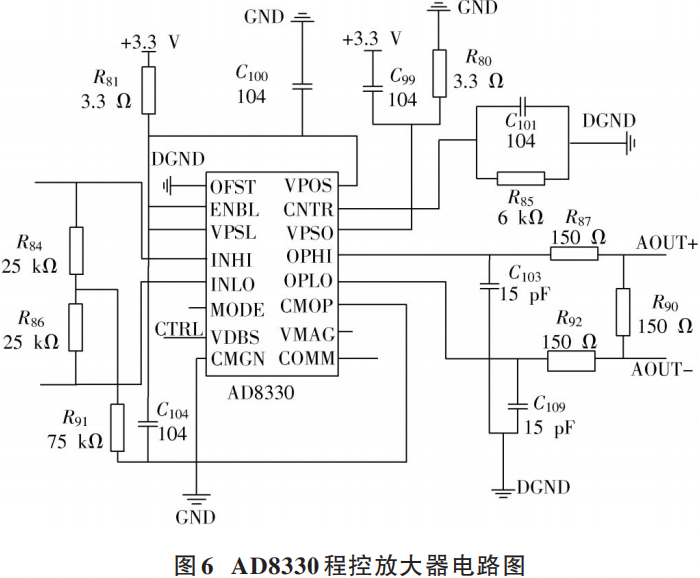

1.2.3 程控放大器

本文选用AD8330作为程控放大器,它是一款带宽高达150 MHz 的宽带宽电压控制型可变增益放大器[9];同时它的增益范围最高可达0~100dB,适合用于差分信号输入电路、低功耗、需要精确定义增益的电路设计。本设计中利用FPGA控制DAC8562的输出电压 ,DAC8562 的输出电压与AD8330的VDBS引脚相连,从而实现了AD8330的可变增益。通过灵活配置VGA的大小,为现场复杂的环境能够准确地检测到局部放电信号提供了便利。程控放大器电路如图6所示。

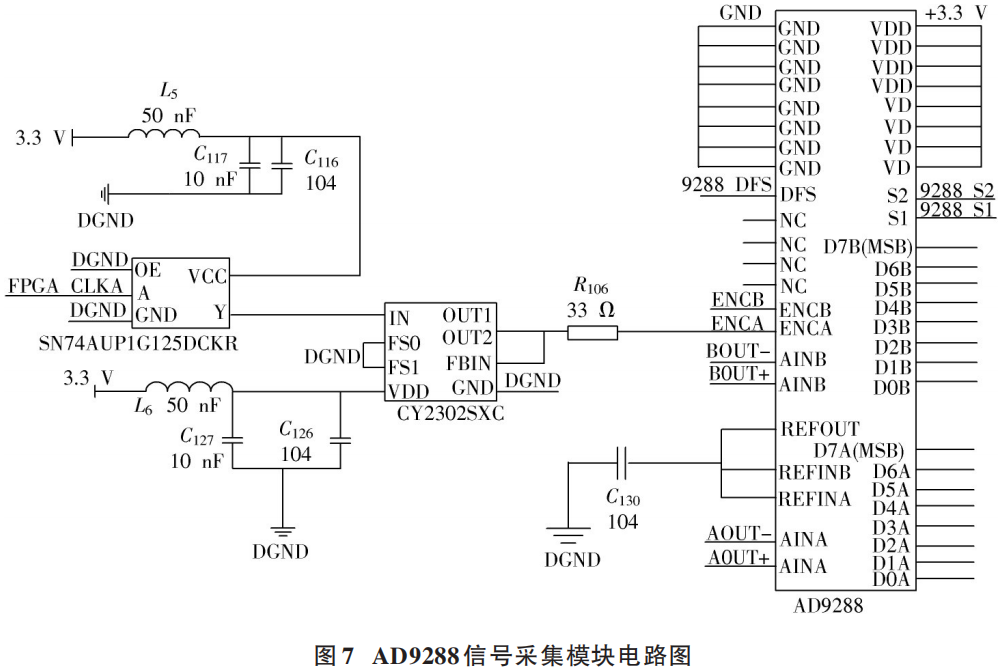

1.3 信号采集模块

信号采集模块包括A/D转换模块以及FPGA模块。AD9288是一种高速、低功耗、具有双通道8位转换精度、最高采样速率可达100 MSPS的A/D采样芯片[10]。FPGA通过输出时钟信号来控制AD9288的采样频率,AD9288将采集到的模拟信号转换成数字信号,并将数据存放到FPGA外扩的SRAM中。信号采集模块电路如图7所示。

2 特高频局部放电检测仪的软件设计

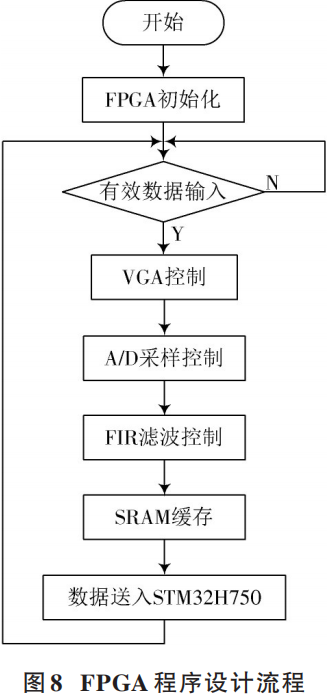

2.1 FPGA 的程序设计

FPGA的顶层模块主要包括FMC通信模块、读写SRAM模块、AD9288模块、FIR滤波模块和DAC 8562模块。各个模块之间相互配合,实现了特高频局部放电信号的采集,各个模块的功能如下:

1)FMC通信模块用于与ARM进行通信;

2)读写 SRAM 模块主要用于对采集到的局放数据进行存储与上传;

3)AD9288模块主要用于对A/D采样频率的控制;

4)FIR滤波模块主要用于对现场复杂环境下的干扰信号进行滤波;

5)DAC8562 模块主要用于控制程控放大器的倍数,以便于更加精确地检测到局放信号。程序流程如图8所示。

2.2 ARM 处理器程序设计

特高频局部放电检测仪是利用超高频传感器来检测电力变压器内部发生局部放电时产生的电磁波信号,并能够清晰地显示局部放电信号的特征图[11]。因此,能否准确地采集到局部放电信号是关键。本程序采用可灵活配置系统参数的设计方式,大大提高了在现场较为复杂的环境中能够准确地采集局放信号的可能性。

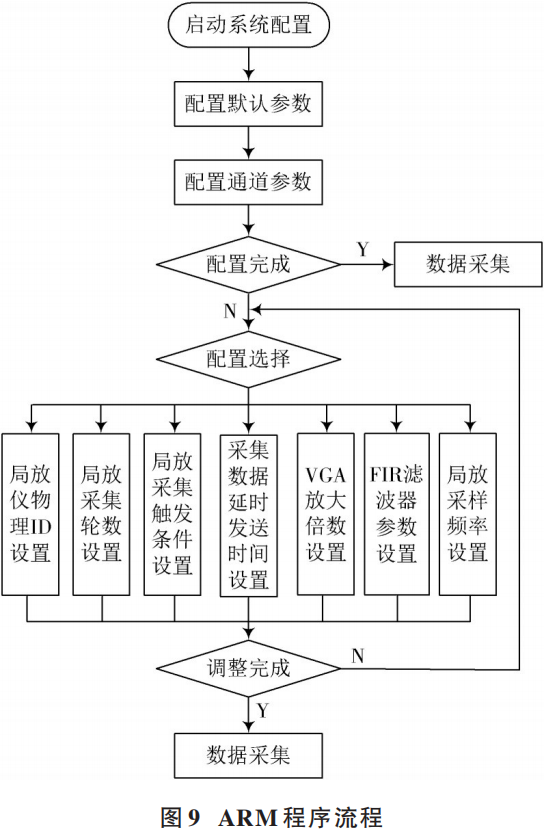

在实际的系统参数配置过程中,主要是根据现场实际情况,选择调整特高频局部放电数据采集系统中相关特性的参数配置,为了能够达到在不同的现场环境中拥有一个最优的参数配置,来实现整个系统的软、硬件运行能够拥有一个较高的准确性与可靠性的目标。其具体的配置流程如图9所示。

3 系统测试

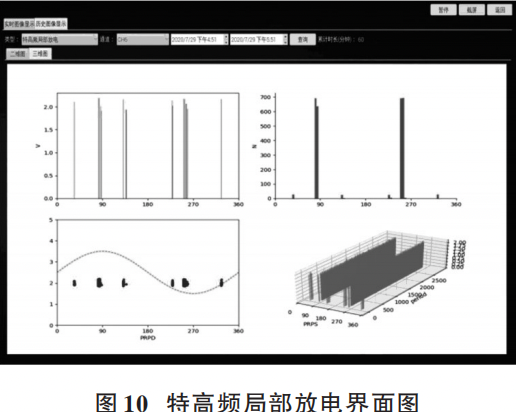

本文设计与开发了一套基于Qt的变压器状态监测系统[12]。利用Qt作为界面主开发框架,且以串口通信、QCustomPlot、MySQL数据库等作为辅助支撑,提供扩展接口和数据协议接口[13]。在树莓派一体机上实现了特高频局放信号数据的传输与数据显示的功能,最终在实验室条件下,通过打火产生的特高频局放信号通过特高频传感器和设计的信号处理电路后,将数据上传至上位机后显示的界面结果如图10所示。由图可知,设计的特高频局放传感器与信号处理电路能够准确地显示特高频局部放电的幅值相位图、相位次数图、PRPD图、PRPS图,成功地实现了对特高频局部放电的监测,为后期的局部放电的模式识别和定位提供了极大的便利。

4 结 语

本文提出一种基于FPGA+ARM的特高频局部放电检测仪的设计。该方法利用FPGA强大的可编程能力,大大减少了硬件设计的复杂度和提高了整个系统运行的速度,同时在 FPGA中创新性地设计了可以灵活控制VGA大小的DAC8562模块,以及可灵活控制滤波程度的FIR滤波器模块,为现场复杂的环境下准确检测到特高频局放信号提供了保证。同时利用了ARM在通信、数据处理、人机界面上有很好的表现的特点,大大提高了系统能够实时监测的可行性。实验结果表明,设计的特高频局部放电检测仪稳定性很好,满足实际的需求。

作者简介:

江友华(1974—),男,博士,教授,研究生导师,研究方向为谐波、电能质量及变压器状态监测。

黄荣昌(1994—),男,硕士研究生,从事变压器局部放电监测研究工作。

顾胜坚(1961—),男,高级工程师,从事电力变压器、电抗器、组合式变电站等电力设备的设计、研究及制造。

杨兴武(1981—),男,博士,副教授,主要从事电力系统无功补偿与谐波抑制技术、风电与太阳能并网控制等研究工作。

吴卫民(1974—),男,博士,教授,主要从事先进电力电子技术及可再生能源利用方面的研究工作。

刘 军(1973—),硕士,高级工程师,杭州钱江电气集团股份有限公司总工,长期从事变压器设计及故障评估方面的工作。

-

从零开始部署:特高频局部放电UHF检测——电力设备的“听诊器”2026-03-20 315

-

局部放电检测设备都有哪些?2025-08-15 1226

-

特高频局部放电检测技术的优势2025-08-14 1003

-

JFD-2000A多通道局部放电检测仪操作使用2025-02-27 430

-

局部放电检测仪的结构——每日了解电力知识2024-05-20 1661

-

多功能局部放电带电检测仪的介绍——每日了解电力知识2024-04-28 1410

-

中智诚ZCJF-V3局部放电检测仪2022-07-27 670

-

手持局部放电检测仪的维护方法2022-03-03 5920

-

典型的局部放电测量电路与局部放电测试仪分享2020-11-23 3670

-

局部放电检测简介2020-11-13 2920

-

为什么局部放电检测很重要?2020-05-19 2638

-

局部放电检测仪的使用注意事项2020-03-07 2773

-

【UT4418申请】特高频全景局部放电检测仪2015-10-27 2321

全部0条评论

快来发表一下你的评论吧 !