低密度NOR闪存可延长嵌入式应用的产品寿命

存储技术

描述

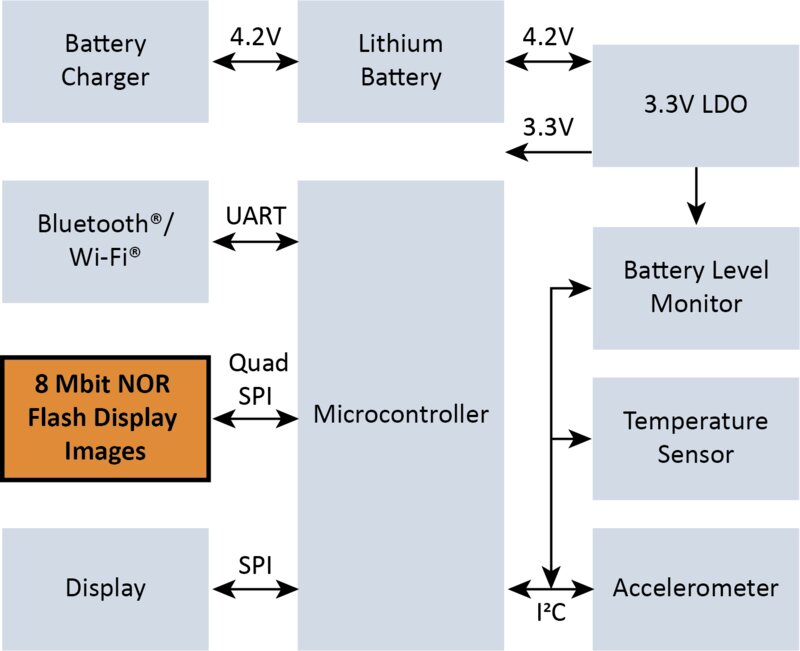

小型独立和嵌入式系统——想想车库开门器、电钻、生产线设备和医疗分析系统——通常包含一个 8 位或 16 位微控制器 (MCU),周围是一组模拟和传感器集成电路 (IC) 、显示和通信接口 IC,在某些情况下,还有 SRAM、EEPROM 和 NOR 闪存 IC,这些 IC 不包含在所选微控制器中(见图1)。当这些工业或医疗产品继续投放市场 20 年甚至更长时间时,终端设备制造商会感到最高兴。

当 IC 供应商宣布因迁移到新工艺节点而导致生命周期结束 (EOL) 时,这通常会成为这些系统制造商的重新认证争夺战,从而转移工程资源并增加现有项目的意外支出。NOR 闪存 IC(这些产品通常只需要 1 Mbit 到 8 Mbit)是一个特别繁重的长寿部件。这是因为更大密度的 NOR 闪存系列成员(256 Mbit 到 1+ Gbit)推动了内存供应商的业务决策,因此不断推动更小的几何工艺和更短的产品生命周期。

本文讨论了 NOR 闪存寿命问题和 Microchip Technology 的解决方案。

低密度内存的前景

领先的 NOR 闪存供应商正确地专注于他们的高利润、大容量、高密度存储部件。每家公司都有责任专注于自己的优势,以便在为客户带来最大价值和最低成本点的同时实现利润最大化。在 NOR 闪存的四个十年中,这意味着幸存下来的内存供应商需要抛弃过去几年的低密度产品。

随着高端密度产品的上升,几年后,非常低密度的产品将停产,如此循环往复。对于拥有 20 年产品寿命的嵌入式系统供应商而言,这些 IC 中断不仅意味着当前供应商部件的新版本,还意味着新供应商。

这个痛苦问题的一个解决方案是通过使用 128-Mbit NOR 闪存 IC 来保存 4 Mb 的用户编程代码来“面向未来”系统设计。这种方法显然会导致功耗和整体系统成本的低效。另一种解决方案是使用非传统的 NOR 闪存供应商,该供应商出于其他商业原因提供相同的内存产品 20 多年。该供应商可能不具备存储量的规模经济,无法在首次投标时提供最低的当前成本点,但随着时间的推移,在考虑可能的重新鉴定成本和进行这些重新鉴定所损失的工程资源时,最重要的是对于这个供应问题,可能是一个成本低得多的答案。

Microchip 多年前就发现了这一挑战,因为它影响到广泛的嵌入式客户群。这种密度趋势对业务计划和业务目标的负面影响需要进行战略路线修正。结果是非传统的 NOR 闪存 IC 供应商提供串行 SRAM IC、串行 EEPROM IC、模拟和传感器 IC 产品。只要客户需要,这些“其他商业原因”提供了继续供应低密度 NOR 闪存 IC 的动力。此外,这些内存产品供应目前停止在 64 Mbit 以上的密度,重点内存供应商将在未来 20 年或更长时间内继续提供产品。

推荐 的 NOR 闪存器件具有预编程的 MAC 地址

图 1是正在讨论的系统类型的表示:一个被其他 IC 包围的 MCU,以赋予嵌入式应用程序生命和用途。在此示例中,8-Mbit 设备(突出显示)包含几个不同的显示图像,只要程序代码(在本例中嵌入在 MCU 中)需要它,它们就会通过触摸屏显示输出 IC 共享。这款外部 NOR 闪存 IC 的主要特点是 8 Mbits、标准 SPI 接口、低待机电流、低写入电流、小面积和 20 年的生产可用性。

图 1:由于微控制器是嵌入式系统的核心,特定应用还需要其他几种 IC 技术,包括 NOR 闪存。(图片:微芯片)

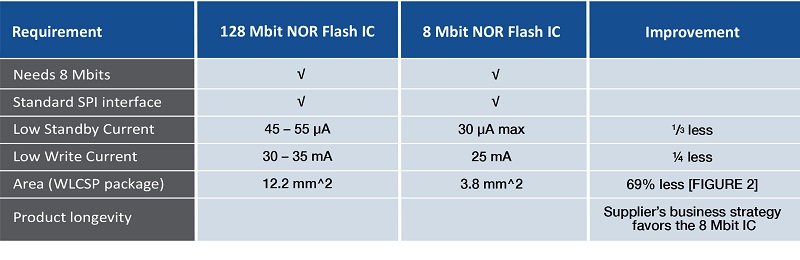

表 1比较了处理 EOL 低密度 NOR 闪存的两种提议的解决方案:用于面向未来的 128-Mbit NOR 闪存 IC 和非传统存储器供应商提供的长期可用的 8-Mbit NOR 闪存。显然,8-Mbit NOR 闪存 IC 最能满足嵌入式应用的要求。

表 1:128-Mbit NOR 闪存 IC 与 8-Mb NOR 闪存 IC 的比较显示了优势。(图片:微芯片)

使用低密度 NOR 闪存

如前所述,虽然低密度 NOR 闪存可能不适合大型 NOR 闪存供应商的计划或战略,但它非常适合嵌入式公司的产品供应和系统方法战略。例如,一个典型的家庭很容易拥有几十个带有 8 位、16 位甚至 32 位 MCU 的嵌入式系统。这些系统中的大多数不需要大量代码,因此 NOR 闪存通常提供程序代码、校准数据、校准参数、事件日志等。

尽管许多 MCU 带有内置闪存来完成这些工作,但在某些情况下,如图 1 所示,外部 NOR 闪存对其中一些应用更有意义。给出的常见原因是总系统物料清单 (BOM) 成本权衡与提供的 MCU 闪存大小、MCU 功能与嵌入式闪存大小的不匹配、生产线制造期间测试集的更快刷新时间、现场升级的系统内刷新事件等.

此外,诸如现场可编程门阵列和复杂可编程逻辑器件等门数较低的专用集成电路使用小型 NOR 闪存进行应用内编程、引导代码和就地执行 (XIP) 操作。NOR 闪存 IC 非常适合提供低待机功耗的 XIP 应用,并且可以使用标准串行接口(例如 SPI)直接访问。

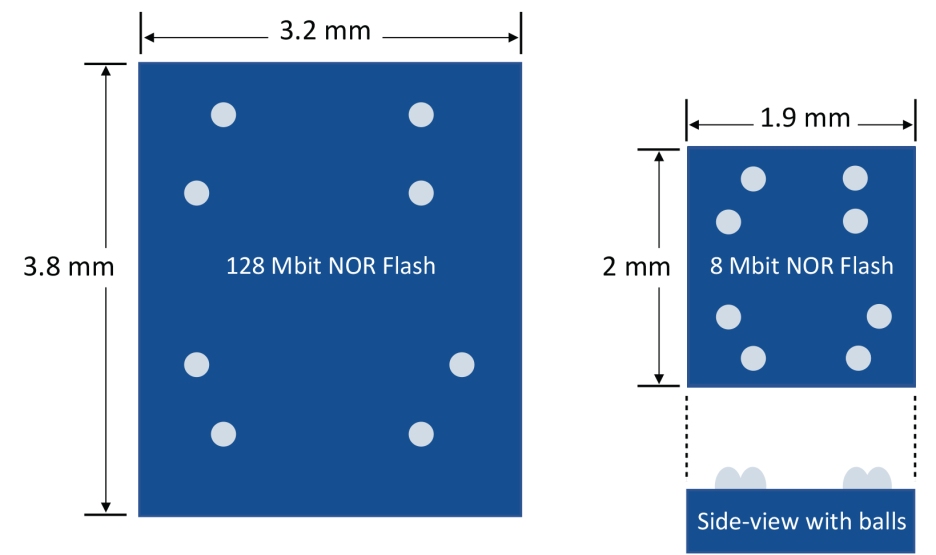

低密度 NOR 闪存器件采用 8 引脚封装,例如 8 引脚 SOIC 和 8 触点 WDFN (6 × 5 mm),板级效率也很高。对于电路板空间有限的应用,例如电动牙刷,晶圆级芯片级封装 (WLCSP) 可显着节省封装空间(几乎 69%),如图2 所示。

图 2:8 Mbit 与 128 Mbit WLCSP 的封装尺寸差异可能非常显着,尤其是在空间很关键的情况下。(图片:微芯片)

1000 ×更快的刷新时间

尽管 Microchip 是一家非传统存储器供应商,但它生产大量闪存。每年出货数十亿个 MCU,其中包括闪存。此外,通过 Microchip 收购 Silicon Storage Technologies (SST) 获得的被称为SuperFlash技术的闪存具有显着的技术和战略优势。这些闪存单元的结构可提供业界最快的擦除时间,与典型闪存器件相比,块擦除时间快 20 倍,全芯片擦除时间快 1,000 倍。

虽然重新刷新 NOR 闪存在大型 NOR 闪存供应商的世界中并不常见,但通过降低制造成本(例如在生产线上重新刷新内存映像以提高系统测试覆盖率)和提供一种低功耗、快速升级现场系统的方法。

回到上面的 128-Mbit 比较,128-Mbit NOR 闪存(没有 SuperFlash 技术)的典型最大块擦除时间为 0.7 秒到 1 秒。相比之下,8 Mbit NOR 闪存(具有 SuperFlash 增强功能)的块最大擦除时间仅为 25 毫秒(快 30 倍)。除了节省时间之外,在一个重写周期中,每次块擦除的擦除/重写功率差异约为 800 ms × 33 mA。

新设计中的 NOR 闪存

Microchip Technology 对嵌入式系统的许多领域都有独特的见解,而 NOR 闪存是这种见解不可或缺的一部分。为了让人们对使用寿命长达数十年的设计充满信心,只要客户需要更换产品,它就有一种既定的做法来确保可用性。虽然一些供应商可能会退出 NOR 闪存产品甚至宣布 EOL,但这一承诺可以确保小型、中型甚至大容量应用的可用性。这种使用寿命确保客户可以获得他们嵌入式系统所需的部件——只要需要。

审核编辑:汤梓红

-

原创:应用串行NOR闪存提升内存处理能力2012-12-12 2403

-

1μAIi同步升压转换器可延长便携式设备的电池寿命2019-06-14 1949

-

80μA静态电流同步降压控制器可延长汽车应用中的电池寿命2019-07-18 1217

-

SOT-23 SMBus风扇速度控制器可延长电池寿命并降低噪音2019-07-25 1712

-

可延长电池动作时间的电源电路2009-09-22 606

-

电视机除尘可延长使用寿命2010-02-22 1272

-

恒忆创新多位配置串口NOR闪存加速嵌入式应用性能2010-03-08 1161

-

飞兆半导体推出N沟道MOSFET器件可延长电池寿命2010-03-20 1437

-

带信号处理功能的超低功率音频编解码器可延长消费电子产品的电池2010-01-04 1029

-

FPGA平台架构在嵌入式系统中的使用2019-04-13 1752

-

串行SPI NOR闪存与并行NOR闪存之间的对比2021-03-03 2539

-

高效的双向主动平衡器可延长电池运行时间2021-03-19 915

-

可延长小型电池续航力的超低静态电流 IC2021-03-21 768

-

MRAM HS4MANSQ1A-DS1用于固态硬盘(SSD)可延长寿命2024-03-18 1454

-

具有ULQ™ 模式、可延长电池寿命的4.5V至24V、8A同步降压稳压器TPS51396A数据表2024-03-26 597

全部0条评论

快来发表一下你的评论吧 !