硅 IPD 节省电路板空间,解决设计挑战

今日头条

描述

作者:Gina Roos,电子产品总编

小型化是采用集成无源器件 (IPD) 的最大驱动力,它可以在各种终端产品中替代分立电容器、电阻器和电感器,尤其是智能手机等不断缩小的消费设备。它们有多种口味——硅、玻璃、陶瓷,甚至砷化镓 (GaAs)。由于晶圆工艺的固有优势,包括可重复性和严格的公差控制,基于硅的 IPD 已经取得了长足的进步,并且仍然是 IPD 的首选基板材料。

根据 MarketsandMarkets 发布的一份新报告,IPD 市场正在快速增长,预计 2023 年将达到 15 亿美元,高于 2018 年的 10 亿美元,复合年增长率为 8.8%。Yole Développement (Yole) 表示,特别是薄膜或硅基 IPD 因其在间距、容差、柔韧性和封装方面的更高性能而取得进展,预计 IPD 市场将超过 10 亿美元到 2022 年。

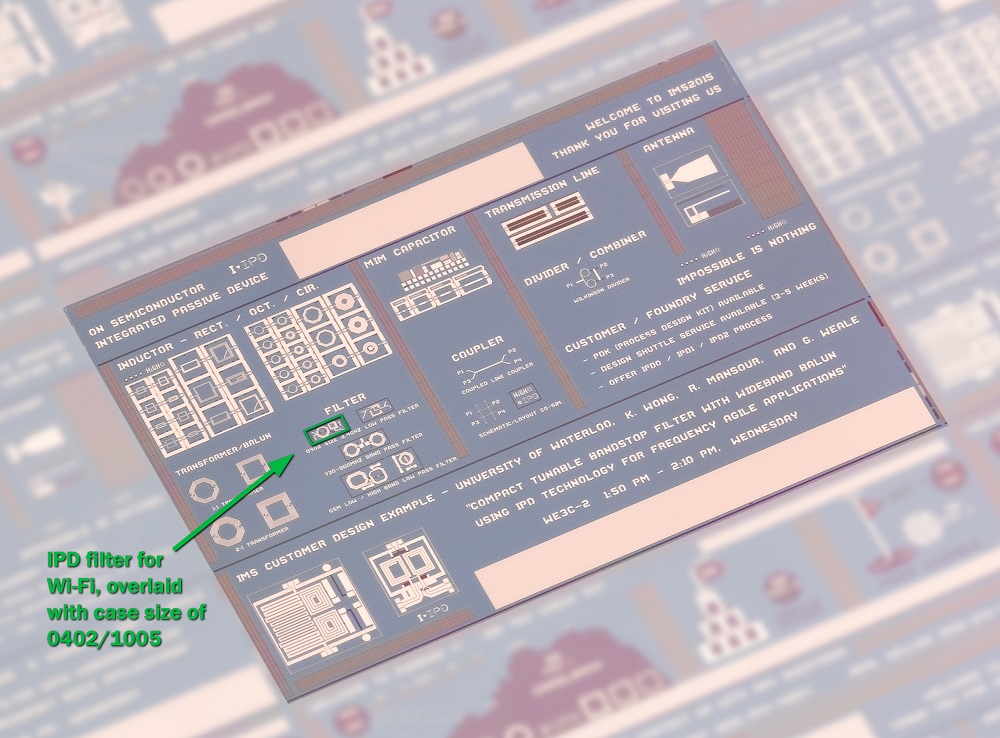

IPD 的主要应用是静电放电 (ESD) 和电磁干扰 (EMI),它们具有完善的标准。然而,使用平衡不平衡转换器、双工器和滤波器的射频前端模块的 IPD 集成正在取得进展,目标是便携式、无线和射频应用。射频 IPD 市场中有不少厂商提供标准或定制设备。其中包括村田 IPDia、安森美半导体、意法半导体和 Qorvo。

RF IPD 的优势IPD 技术可用于各种 RF 设计——包括巴伦、耦合器、双工器、滤波器、分路器和匹配网络——将电容器、电阻器和电感器组合在一个封装中。安森美半导体首席工程师兼 IPD 产品线经理 Kim Eilert 表示,最大的需求驱动因素是尺寸、容差和性能。

安森美半导体在其基于硅的 High-Q 铜平台上构建定制射频 IPD 。Eilert 的部分工作是帮助客户设计 IPD 并确保他们在产品上取得成功,这就是为什么她会告诉您 RF IPD 不推荐用于 <500 MHz 的频率。“IPD 中没有足够的金属来获得良好的损耗性能,除非它只是一个电容器或电阻器,”她说。“[在那个频率下]使用另一种技术会更好。”

然而,她补充说,有些应用程序是定制的。其中包括需要小型化、严格公差和更高性能的应用。

Eilert 说,当设计工程师开始设计系统时,他们通常会考虑多种技术,并且会考虑成本、尺寸、热性能和组装简易性等因素。他们将考虑几种技术并评估他们需要什么。

“当人们决定使用 IPD 时——无论是在玻璃、陶瓷、硅还是 GaAs 上——一般来说,他们都受到轮廓高度以及 x 和 y 尺寸的驱动,”她补充道。“能够使 IPD 变薄以匹配有源 IC 的确切高度是一个优势,因为您可以缩小整个模块的 z 高度。”

IPD 比离散解决方案小得多,x/y 尺寸的节省可能很大。“通过添加集成,您可以缩小组件所需的 x/y 占用空间,”Eilert 说。“有时,这不仅仅是‘锦上添花’,而是绝对的要求。”

另一个推动 IPD 设计的因素是容差。“如果您单独购买过滤器的每个组件,它们都有各自的容差,因此整个系统的容差比将其制造为单独的芯片时更宽。”

“因为我们在这个 [IPD] 芯片上同时制造所有东西,例如,单个芯片上的所有电容器都将相互匹配。所以有性能优势。在更高的频率下也有性能优势——同样,因为它都是在具有良好 [亚微米] 尺寸控制的晶圆上制造的。”

寄生效应是设计师面临的另一个挑战。“有时在更高的频率下,安装组件的不良寄生效应确实会破坏设计的性能,”Eilert 说。“当你将所有东西都集成到一个芯片中时,你就不再需要应对安装寄生效应了。”

Eilert 的建议是始终要求提供示例芯片。在电感器的情况下,Q 或高质量因数通常被认为是一个关键指标。她建议,获取一个示例芯片并自己测量它。“通常,代工厂拥有这些信息并且可以提供,但设计人员在进行这些比较时需要请求原始数据。”

她还要求设计人员考虑整体谐振器 Q,而不是查看单个组件并将电感器与电感器以及电容器与电容器进行比较。

“当我们设计谐振器时——在大多数情况下,滤波器设计人员就是这么做的——IPD 非常棒,因为您可以在电容器 (C) 旁边集成一个电感器 (L),”她说。“使用其他技术,可能会限制你获得这两个组件的距离。我建议他们比较整个系统——比较 LC 谐振器和 LC 谐振器。最终,这就是他们想要建立的。”

像大多数事情一样,自定义 IPD 需要权衡取舍。上市时间和成本是最大的两个。

“如果可以避免的话,我认为人们宁愿不参与单独的设计工作,”Eilert 说。“使用现成的组件有很多优势——它们很容易获得,设备非常熟悉,而且从成本的角度来看,与开发定制芯片相比,它需要更少的时间和资源。因此,需要有规模驱动因素或性能驱动因素来引导人们进行 IPD。”

需要性能的巨大机会由于晶圆工艺的可重复性和亚微米公差(高频优势),大多数商业频率(约 1 GHz 至 6 GHz)非常适合硅 IPD。

Eilert 说,许多客户正在使用 1-GHz 至 2.5-GHz 范围内的射频 IPD。IPD 也将非常适合 5G,它将达到 28 GHz——这对设计人员来说是一个挑战。

“例如,如果你必须设计一个 20 GHz 的带通滤波器,那么在可以非常精确地控制尺寸的晶圆技术上构建它是有利的,”她说。“由于这是一个晶圆工艺,我们使用光刻来定义迹线。您可以拥有 5 微米宽的迹线,并且所有东西都带有亚微米公差。”

硅的机械性能也是一个好处。“对于某些应用,希望 IC 的机械膨胀特性与载体封装相匹配,”Eilert 说。她补充说,对于硅 IPD,载体封装将由硅制成,有源 IC 由硅制成,因此不存在机械失配。

设计人员还可以在需要精确的电容或电感值时使用 IPD。“你可以购买现成的组件,但它们的价值范围是固定的,”Eilert 说。“如果您想要 4.7-pF 的电容,您现在可以购买各种规格的电容,但如果您想要像 4.85 pF 这样高度定制的电容,并且需要严格的容差,那么 IPD 就是您的最佳选择。 ”

安森美半导体提供示例芯片和功能齐全的设计套件,以帮助快速启动项目并向客户展示该技术可实现的目标。

Eilert 说,设计师很少坚持基线设计。“我们发现人们不想从目录中购买;他们想为他们的应用程序进行定制。一般来说,对于 RF 来说确实如此,您从一个示例开始,然后自定义引脚排列,或者自定义性能或阻抗以匹配您的特定 IC。它具有性能优势,但确实需要设计努力。”

设计师可以使用 IPD 做很多事情。Eilert 说,她甚至让一位客户构建了一个只有一个组件的 IPD,以获得精确的电感值,而另一位客户将整个 8 英寸硅晶片用于一个芯片作为一种中介层。

然而,安森美半导体有几个设计示例,其中 IPD 节省了大量空间。在一个案例中,该公司为新的 5G New Radio n78 频段构建了一个低成本和低插入损耗的带通滤波器,采用 1608 封装(1.6 x 0.8 mm),集成了 20 个组件。

但是,还有其他半导体制造商提供现成的射频 IPD。例如,意法半导体提供了一系列基于非导电玻璃基板技术的 IPD 的集成巴伦。这些是高度集成的匹配设备,由于采用 IPD 技术,可提供低信号损耗和低幅度和相位不平衡。

截至 2017 年底,ST 提供了 16 个集成巴伦,其封装尺寸低至 0.8 mm 2 和回流后高 0.56 mm。这些器件专为 ST 的 sub-1-GHz 或蓝牙低功耗 2.4-GHz 无线电以及其他制造商的各种收发器而设计。

ST 最新推出的 IPD 之一是为其 S2-LP 868-927MHz 低功耗无线电收发器匹配的巴伦,旨在节省物联网传感器、智能电表、警报器、遥控器、楼宇自动化和工业控制等产品的电路板空间.

ST 表示,3.26-mm 2 BALF-SPI2-01D3 集成了将天线连接到 S2-LP 无线电所需的所有阻抗匹配和滤波组件。该集成器件取代了由 16 个分立电容器和电感器组成的传统网络,该网络最多可占用 100 mm 2 的电路板空间,从而将占位面积减少 96% 以上。

“除了节省空间外,电路设计也大大简化,无需选择元件值或应对严格的布局挑战,”ST 表示。“巴伦针对 S2-LP 进行了全面优化,带有经过测试和验证的放置和连接建议,可以直接复制以最大限度地提高射频性能。”

随着产品不断缩小,预计对所有类型 IPD 的需求都会增长。

“随着市场的尺寸驱动,尤其是智能手机,存在缩小尺寸的压力;这不是可选的,”Eilert 说。“对于传统解决方案,它们对于下一代产品来说太大了。”

审核编辑 黄昊宇

-

SG-9101CA小体积晶振X1G005301001400节省电路板空间的理想选择2024-09-27 509

-

Diodes公司的微功率、推挽式、单极霍尔开关节省电池供电应用的电路板空间2023-09-13 1301

-

东芝推可节省电路板空间的步进电机驱动IC2022-08-26 1320

-

DN254-LT1806:325 MHz低噪声轨对轨SOT-23运算放大器节省电路板空间2021-05-08 917

-

DN266-LT1880 SOT-23 Superbeta运算放大器在精密应用中节省电路板空间2021-04-25 704

-

如何减少PCB上DC/DC转换器封装的热量?如何选择POL稳压器并节省电路板空间?2021-03-10 2293

-

325MHz低噪声轨到轨SOT-23运算放大器可节省电路板空间2019-07-26 1400

-

DN266 - LT1880 SOT-23 Superbeta运算放大器可在精密应用中节省电路板空间2019-06-04 1648

-

意法半导体推出两款新芯片组 可节省电路板空间2019-05-16 3820

-

飞兆集成式FET模块节省系统电路板空间2018-11-22 2465

-

组合式传感器可节省电路板空间和设计时间,并增强可靠性2018-11-13 1730

-

如何节省ZL9101M电源模块空间与降低物料成本2018-06-24 4621

-

能够简化系统、节省电路板空间和开发工作量的应用方案2018-05-25 3404

-

意法半导体推 PWD13F60 节省电路板空间60% 还能提升最终应用的功率密度2018-05-15 2096

全部0条评论

快来发表一下你的评论吧 !