分立式解决方案有利于栅极驱动器的原因

电子说

描述

60 多年来,组件集成一直是半导体行业的驱动力。它就在行业术语集成电路或IC中。年复一年,勤奋的电路设计师、工程师和产品营销人员都在寻找机会,将芯片提升到更高的集成水平,以降低成本、缩小设备和电路板尺寸,并最大限度地减少材料清单 (BOM)。

为什么不?系统设计人员将更多功能集成到 IC 中有许多充分的理由和优势。首先是方便。焊接一个芯片总是比焊接两个更好。接下来是互操作性。当然,集成组件是为协同工作而设计的。无需担心匹配数字接口、阻抗或混乱的胶合逻辑。最后,成本是组件集成的一大诱因。降低成本一直是现在在经济型计算系统和具有不断增加的功能的低成本微控制器 (MCU) 中实现的集成的承诺。

当功能在实现系统目标方面是互补的时,集成就很有意义。高性能运算放大器与模数转换器 (ADC) 的集成就是一个很好的例子。下一步是将这些模拟组件与 MCU 集成。它们一起完成了具有集成所有优势的系统要求。

然而,并非所有的集成都会带来优势而没有明显的劣势或权衡。在某些情况下,系统设计的更好选择可能是继续使用分立元件。通常,是否集成的决定因素是噪声对各种组件的影响。与嘈杂的开关元件集成的敏感模拟测量很少能改进系统。

集成受到质疑的另一个例子是系统的某些部分对空间至关重要。它通常与系统中的寄生电容、环路和电感有关。当必须最小化一个参数时,它通常优先于通过集成可能获得的任何优势。最后,集成的成本效益有时会逆转。这种情况出现在功率 MOSFET 中,其中分立元件最终比等效的集成器件更便宜,因为它们采用了专门的晶圆厂工艺和封装。

案例研究:隔离式栅极驱动器 隔离 式栅极驱动器是体现分立元件优于集成元件优势的常见元件。在电源转换系统中切换高压轨时使用隔离式栅极驱动器。

除了与有效驱动开关门相关的要求(快速电流源、低传播延迟和高瞬态抗扰度)外,还有与隔离相关的不同要求,例如封装间距。

隔离式栅极驱动器不适合集成到配对系统控制器中的原因很明显。例如,场效应晶体管 (FET) 栅极的快速、高压开关本质上是有噪声的。在典型的开关周期中,高边开关上的栅极电压穿过下轨和上轨之间的整个范围。在开关周期的某些区域,它可以在几十纳秒或更短的时间内改变数百伏或更多。

这种波动会在栅极驱动器输出上产生巨大的瞬变。专用栅极驱动器旨在抑制这些瞬变,但将这种噪声引入封装会影响芯片上的所有电路。如果这些电路是敏感的模拟电路或时间关键的数字电路,它们将不堪重负,其功能将徒劳无功。

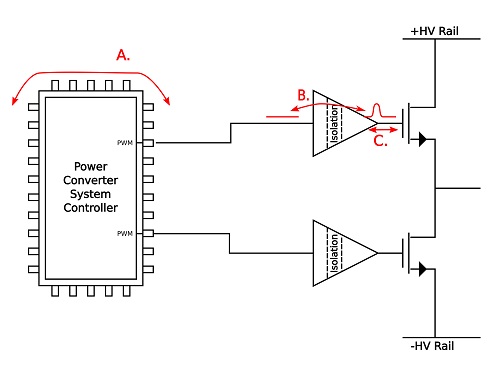

图 1:分立式隔离栅极驱动器通过多种方式优化系统: A) 可以减少控制器封装,并且不会浪费封装沿线的空间;B) 栅极驱动器经过优化以抑制瞬态噪声并防止控制器经历它;C) 通过将驱动器放置在 FET 附近,可以最大限度地减少寄生感应和电容。

这些组件不能选择集成的另一个原因是栅极驱动器需要靠近它负责的开关(图 1)。所使用的开关及其对散热器质量和气流的相关要求通常决定了开关子系统的大小。对于开关半桥,尤其是全桥,集成组件使栅极驱动器无法靠近所有正在使用的 FET(至少两个,但通常是四个或更多)设备。

在设计半桥或全桥电路时,元件布局和 PCB 布局对性能至关重要。为了获得最佳性能,必须将电流返回路径和寄生元件(杂散电容和电感)的影响降至最低。寄生电容和电感是不可避免的,但保持驱动器靠近 FET 可以最大限度地减少不利影响。

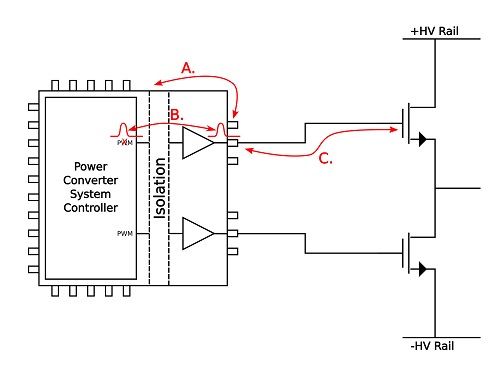

爬电要求 最后,与电流隔离相关的独特爬电要求阻碍了该组件的集成(图 2)。爬电距离定义为 IC 外部暴露金属之间沿封装的间距。通常,随着母线电压的增加,爬电距离会变大。隔离式栅极驱动器的典型爬电距离约为 4 至 8 mm,甚至更大。

图 2:集成隔离驱动器的问题包括 A) 由于爬电距离要求而浪费封装空间;B) 封装内对敏感数字信号的高压瞬态噪声耦合;C) 布局要求增加了到 FET 的距离和恶化的寄生效应。

在集成隔离式栅极驱动器的理论案例中,这种爬电距离要求会给其余组件带来很大负担。与系统控制器集成需要增大封装尺寸,并且没有引脚或裸露金属的大面积区域可能会减少爬电距离。

这可能会显着减少控制器可用的外围设备,这些控制器通常在设备的四个侧面都有引脚,每个引脚都分配有功能。增加封装尺寸和适应隔离栅的要求必然会增加系统成本。

Silicon Labs 提供多个高性能分立隔离式栅极驱动器系列。有些包括可放置在非常靠近电源开关的单栅极驱动器选项。其他系列具有高端/低端对,在抗噪和成本优化方面提供与分立驱动器相同的优势。但是,必须注意这些器件的布局,以保持对称的寄生环境。

例如,Silicon Labs 的 Si827x 驱动器系列提供了非常高水平的瞬态抗扰度。即使存在 200kV/μs 的共模瞬变,该器件也能按预期运行。其他栅极驱动器系列,例如 Si8239x,在具有 8mm 爬电距离的封装中提供高达 5kV 的隔离额定值。

集成与分立 在许多情况下,将组件集成到功能更强大的单个设备中是有意义的。几十年来,模拟和混合信号功能、存储器和高性能数字逻辑的集成一直是半导体行业的福音。

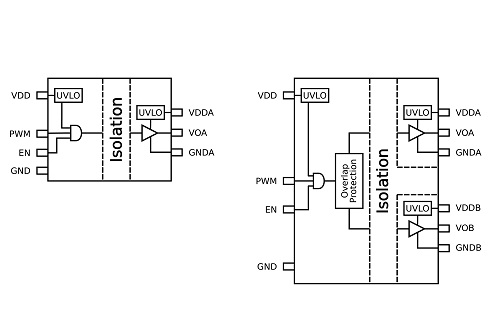

图 3:分立式隔离栅极驱动器为高效开关提供基本功能,包括用于异步控制的欠压锁定 (UVLO) 和使能引脚 (EN)。双隔离栅极驱动器增加了更多功能,例如重叠保护,但在布局时需要更加小心。

但是,在某些应用案例中,集成模型存在不足。用于电源转换器的开关电路的栅极驱动器必须保持分立元件,以防止噪声干扰系统控制器功能,并允许将驱动器放置在靠近开关的位置以减少寄生效应。

由于独特的封装尺寸要求,在系统设计中使用隔离式栅极驱动器作为分立元件可以降低整体系统成本。尝试集成这些组件会产生明显的负担,只能通过昂贵的非标准封装来解决。

审核编辑:郭婷

-

AM437x离散功率简化型分立式电源解决方案包括BOM及框图2018-10-10 2698

-

低成本LCD偏置电源分立式解决方案2018-11-19 3589

-

集成与分立式低电压电机驱动解决方案的主要差异2018-12-07 2659

-

支持多种汽车应用的微控制器分立式电源设计2018-12-28 1597

-

集成压控振荡器的宽带锁相环真的能取代分立式解决方案吗?2019-07-31 1835

-

为什么要在汽车PTC模块中用低侧驱动器IC替换分立式栅极驱动器?2022-11-04 998

-

开源硬件-TIDA-01162-集成与分立式低电压电机驱动比较 PCB layout 设计2017-11-03 1049

-

采用iCoupler技术如何简化半桥MOSFET驱动器的设计2019-07-29 3093

-

分立式半桥栅极驱动器设计2021-01-13 4265

-

分立式和集成式栅极驱动架构比较资料下载2021-03-30 772

-

为什么要在汽车PTC模块中用低侧驱动器IC替换分立式栅极驱动器2022-01-12 2560

-

[常见问题解答]UCC27517A-Q1:为什么要在汽车PTC模块中用低侧驱动器IC替换分立式栅极驱动器?2022-10-28 741

-

分立式 LED 驱动器-AN107392023-02-09 444

-

集成压控振荡器的宽带锁相环能取代分立式解决方案吗2023-11-22 379

-

在电机驱动器的UCC23513光兼容隔离式栅极驱动器中实现分立式 DESAT2024-08-30 438

全部0条评论

快来发表一下你的评论吧 !