低功耗快速采样的解决方案

描述

尽管数字技术占主导地位,但我们生活在一个模拟世界中。在域之间移动会引入量化误差;这是不可避免的。工程师的工作是使这种转换尽可能无缝,这就是 ADC 和 DAC 的用武之地。

模数转换 (ADC) 可以采用多种形式并有许多折衷方案。从根本上说,关键的品质因数是准确性和速度。更复杂的是,这两个参数通常是相反的。更高的精度需要更多的位,但增加更多的位会降低采样率。更快的转换通常以有效位数为代价。广义而言,选择是通过 Delta-Sigma 转换拓扑(高分辨率、长延迟)或闪存转换器(高速,但以功耗和面积为代价)。位于这两个极端之间的是逐次逼近寄存器或 SAR 转换器。这种“金发姑娘”技术在分辨率和速度之间提供了一个很好的折衷方案,但它也有其局限性。

一般来说,SAR 转换器是无线通信中使用的模拟前端 (AFE) 的不错选择,这要归功于它们兼具准确性和速度。随着物联网的范围从核心进一步延伸,将边缘永远向外推,对能够以更高频率(因此更高采样率)处理更复杂协议但功耗更低的 AFE 的需求不断增长。让我们不要将此称为问题,而是将其称为机会,在无线连接需要放入小到足以戴在耳朵里的东西中的时代,找到一种能够实现更小、更快和更低功耗的 AFE 的技术,并且有可能成为由从其操作环境中收集的能量提供动力。

特区的一点背景

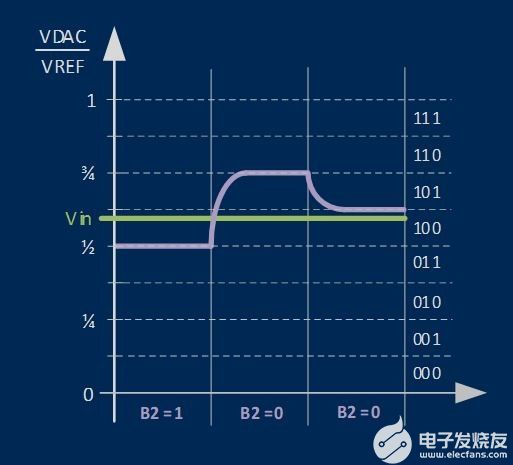

顾名思义,SAR 通过连续逼近模拟输入的值来运行,迭代地将输入电压与重复减半的参考电压进行比较,直到参考电压和源之间的差异无法区分或满足设计要求。每次比较都会产生一个“更高”或“更低”的结果,在数字输出中形成一个位,从最高有效位开始。这种情况一直持续到转换器以足够的精度生成足够的位来表示模拟输入。

图 1:3 位 SAR ADC 示例

由于所有步骤都需要在采样周期内完成,因此可能的位数主要取决于电路中需要更改的元件的响应时间。这包括用于与输入电压(通常存储在包含开关和电容器的采样保持电路中)进行比较的参考电压。反过来,该参考电压(通常)由数模转换器或 DAC 生成。因此,SAR 转换器的采样率将在一定程度上由用于生成参考电压的 DAC 和控制逻辑决定,但通常 SAR 性能实际上受到比较器速度的限制。输入端的开关电容实际上是一个低通滤波器,它引入了一个上限频率阈值,但由于开关电阻低且电容小,这意味着转换器通常可以处理数百 MHz 或更高的信号;特区的另一个积极特征。

就整体精度而不仅仅是分辨率而言,重要的是生成供 DAC 使用的参考电压(而不是 DAC 生成的用于比较器的电压)也要尽可能准确,因为所有其他测量都与这个。尽可能多地集成整个解决方案的 SAR,包括开关电容器 S&H 和 DAC 参考电压发生器,将提供最佳性能。

克服 SAR 转换器的限制

流水线 ADC 具有多个阶段,每个阶段都处理部分转换过程。随着每个阶段完成其操作,它可以自由地接受下一个样本。流水线 ADC 的主要优势之一是它的速度。一旦管道完全准备好,它就可以随着新样本“推动”数据而产生新的输出。虽然 SAR 的架构通常基于多次使用的单级,但流水线转换器使用并行性来加快速度。

将 SAR 和流水线方法相结合产生了所谓的 SAR 辅助流水线 ADC。Adesto 的工程师已经实施了这种方法来创建一个 ADC,该 ADC 可以在高带宽下以最高速度和精度运行,但需要最小的功率和面积。

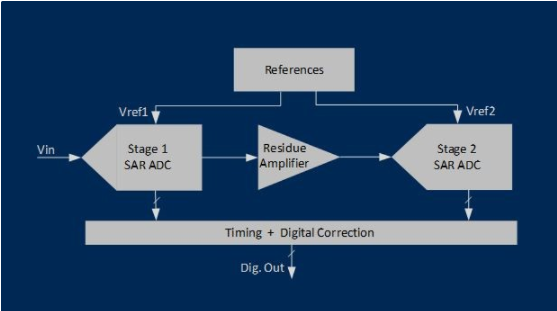

Adesto 开发的转换器使用两个 SAR 级;第一阶段处理输出的最高有效位,而第二阶段处理最低有效位。通过添加一个数字模块来处理定时和校正(参见图 2),SAR 辅助流水线转换器可以在不到同类 SAR 转换器一半的时间内生成结果,而不会产生与传统流水线 ADC(包括物理尺寸和功耗)。

图 2:SAR 辅助流水线 ADC 架构

简单来说,只要第一个 SAR 阶段完成转换,它就可以接受一个新样本,而第二个 SAR 阶段完成第一个样本的转换。级之间放大器的增益放宽了对第二个 SAR 的要求,从而产生了比 SAR 本身更节能的解决方案。

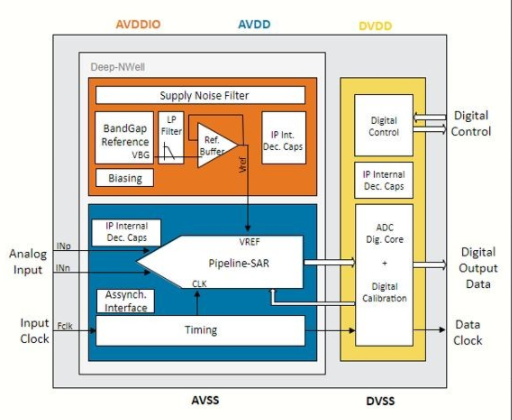

图 3 显示了 Adesto 的 SAR 辅助管道 ADC 的框图。

图 3:Adesto 的单通道 SAR 辅助管道 ADC

如图 3 所示,Adesto 开发的 IP 包含所有关键功能,包括参考电压发生器、定时和控制逻辑、数字校准以及去耦电容器。对所有模拟模块使用深 n 阱技术可提供对衬底噪声的抗扰度,当客户在可能没有专用模拟电源可用的设计中授权使用 IP 时,这一点尤为重要。该设计真正全面,因为它不需要外部电压基准或稳压器。

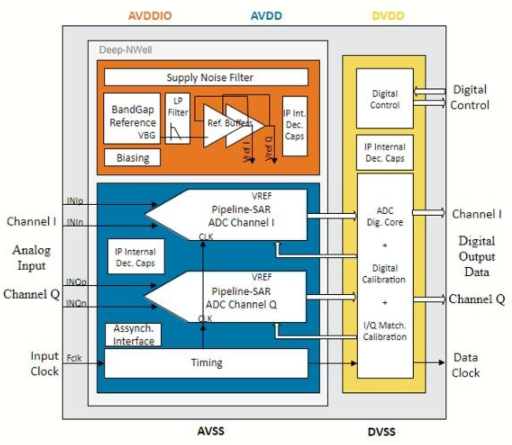

相同的内核 IP 已用于开发针对正交 I/Q 调制架构的双通道解决方案(图 4)。可以看出,一些功能可以在两个通道之间共享,同时包括单独的参考缓冲器和时钟树,以最大限度地减少通道之间的串扰。

图 4:Adesto 的双通道 SAR 辅助管道 ADC

这种方法提供的主要优势之一是其低功耗运行。Adesto 部署在现已上市的批量 IP 中,包括采用 28nm 工艺的双通道解决方案,在每个通道上提供 160Msamples/s,总功耗仅为 18mW。该 ADC 的总芯片面积仅为 0.055mm2,因此具有极高的面积效率。尽管具有这种集成度,但它可以提供 63.1dB 的 SNDR,并且通道之间的串扰低于 -80.0dB。

同一转换器的八通道版本可以同时处理四个 I/Q 通道,以 122.88Msamples/s 的速度运行,同时仍仅耗散 45mW。它的有效位数 (ENOB) 为 10.2 位,但仍只需要 0.3 平方毫米的芯片面积。Adesto 还可以提供 12 位 SAR 辅助流水线 ADC,在仅 0.05mm2 的裸片面积上实现 200Msamples/s 的采样率、10mW 的功耗。

AFE 严重依赖 ADC 的性能,而不起眼的 SAR 是工程师可用的最可靠和最通用的架构之一。这只是 Adesto 提供的 IP 的一个示例,该 IP 已经过优化以满足最新应用程序的需求。

审核编辑:郭婷

-

为什么选择 Nordic 的低功耗蓝牙解决方案?2026-04-16 124

-

有哪些低功耗测试方案让你相见恨晚?2020-04-23 2803

-

低功耗手持式/助听器应用的解决方案2019-07-23 3222

-

采用16-bit MCU的超低功耗运动检测系统解决方案介绍2019-07-19 2549

-

基于RN4020蓝牙低功耗PICtail/PICtail Plus解决方案2019-04-10 1787

-

基于FRAM的低功耗LED照明解决方案2018-09-10 1791

-

蓝牙低功耗应用的SimpleLink解决方案(4)2018-08-20 3681

-

2.4G低功耗无线方案2018-07-11 3566

-

超低功耗FPGA解决方案助力机器学习2018-05-23 6776

-

小尺寸、超低功耗的智能穿戴定位解决方案2017-09-28 4615

-

基于低功耗传感器解决方案2017-09-18 818

-

Nordic 低功耗蓝牙键盘解决方案2013-11-04 4216

-

提供硬件加密解决方案,待机低功耗解决方案2011-02-15 2157

全部0条评论

快来发表一下你的评论吧 !