总结一下高速信令的指标与应用场景

描述

不知道这篇文字应该叫电路逻辑结构还是高速信令,想写的原因是基于之前学习模型或者看芯片的设计规范时,会有下面的一些信息:

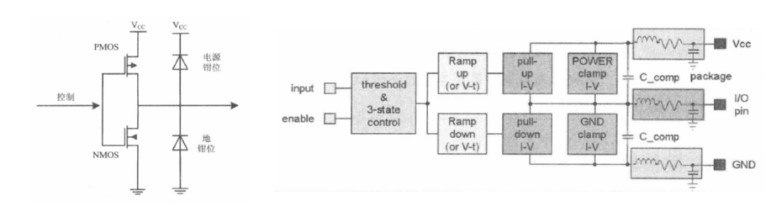

IBIS模型,电路逻辑模型结构里面有COMS电路,由一个上拉的PMOS管和一个下拉的NMOS管构成,在I/O的接口位置,还有两个钳位二极管。

IBIS模型简化结构

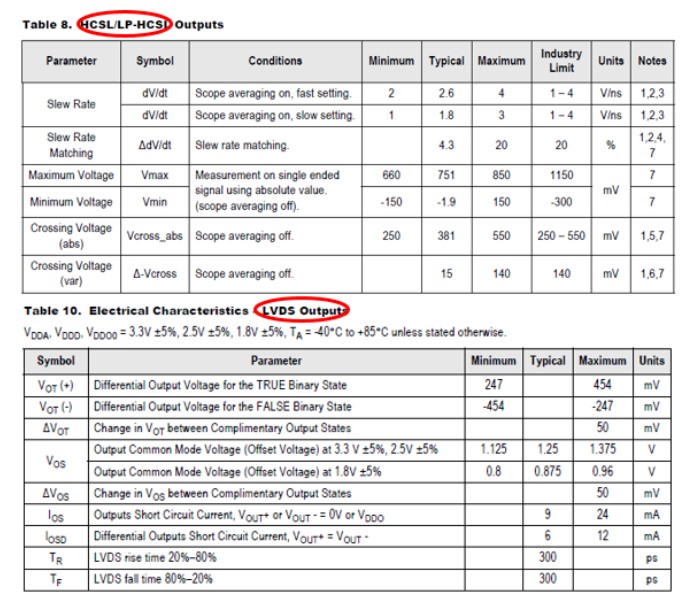

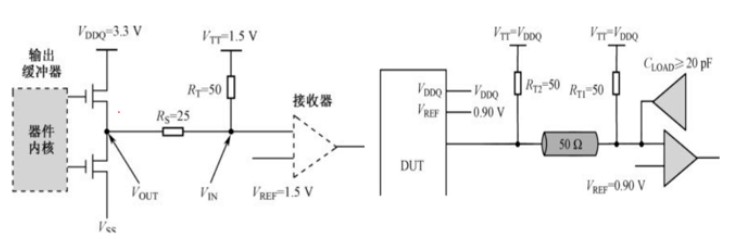

看芯片datasheet ,也会有各种电路逻辑结构:

所以,就想了解一下这些电路逻辑结构。

信号完整性的工作,不管是SI,PI还是EMI,都是管控信号传播路径,来满足相关标准。而我们看到的红圈标记的东西,是另一种标准,即发送/接收端确定以何种的高低电平与结构进行信号转移传递。有的资料说,这就是高速信令。

TTL 和CMOS逻辑电路是大学时期数字信号的基础知识,那里面有逻辑电平分类:5V(5V TTL 5V COMS)3.3V ,2.5V,1.8V等。TTL 和CMOS逻辑电路都是5V电源电压。但这里面还有区别,输入高低电平和输出高低电平不一样,比如TTL输出高电平>=2.4V,而CMOS输入高电平是3.5V,这时候CMOS电路检测不到高电平,就满足不了要求。

可以通过转换符合电平输出的芯片,或者增加上拉电阻的方式,来输出符合要求的电平。一般来说CMOS电路可以直接驱动TTL,但是TTL 不能直接驱动CMOS。

所以不同信令之间需要转换电路来完成对接。

TTL 电路是电流控制器件,CMOS电路是电压控制器件,这有什么区别呢?电压控制需要一个开关的过程,有传输延迟,大概在25~50ns,电流控制虽然延迟小,但功耗大。

不同应用会选择不同的逻辑电路。背板系统的总线驱动之前采用TTL或CMOS逻辑电路。但是其3.3~5V的高电压摆幅导致高功耗,也不能提供正确匹配所需的负载条件。这个时候,采用GTLP(Gunning Transceiver Logic Plus),更低的电压摆幅和集电极开路输出级解决了这些问题。

差分信令,第一时间想到的就是LVDS。

LVDS(Low-Voltage Differential Signaling,低电压差分信令)又称RS-644总线接口,是一种数据传输和接口技术。LVDS是PCB板级或子系统间高速数据传输的一种高可靠、低功耗、低噪声、低成本的解决方案。

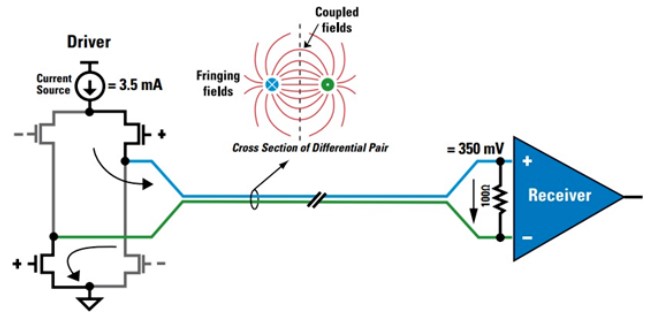

LVDS采用的是电流模逻辑。LVDS输出包括一个恒流源,它驱动差分对的电流。两个N管导通,在接收器前的匹配电阻上产生正向压降,输出高电平;两个P管导通,在接收器前的匹配电阻上产生反向压降,则输出低电平。接收器匹配电阻上的压降,正向为高,反向为低。

这一逻辑结构采用低功耗CMOS管,电流源的电流一般为3.5mA,接收器前的匹配电阻一般为100Ω,产生的压降为350mV。

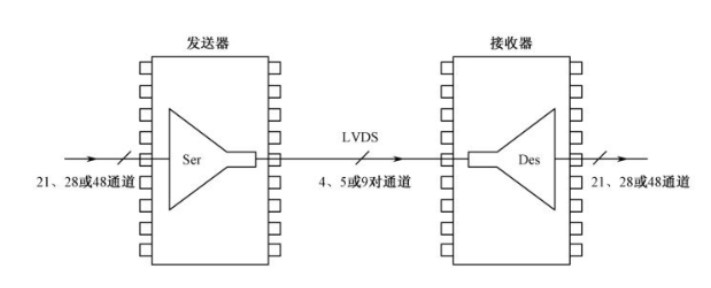

LVDS与TTL/CMOS逻辑的接口设计非常方便,采用SerDes芯片就可以轻松实现TTL/CMOS逻辑并行总线到LVDS串行总线的转换,以及从LVDS串行总线到TTL/CMOS逻辑并行总线的转换。

高速信令有单端信令和差分信令之分。

信令指标有很多,比如:逻辑信号电平,应用场景,电压摆幅,驱动方式,负载匹配,是否支持热插拔,支持最大的数据率等。

逻辑电路及电压要求

说到应用场景,总结一下常见的一些高速信令:

AGTL+(Assisted Gunning Transceiver Logic+)用于处理器、存储器和I/O之间的多处理接口以及各种Intel芯片组的系统总线的信令技术。

HSTL(High-speed Transceiver Logic)一般工作在200MHz以上,是高速存储器应用的I/O接口首选,非常适用于多存储器组地址总线的驱动。在中频范围(100~180MHz),I/O端口的单端信令还有GTL/GTL+、SSTL和LVTTL。

SSTL(Stub-Series Terminated Logic)信令标准是专为高速存储器应用开发而制定的。特别针对工作频率为333MHz或以上单双数据率的SDRAM,还支持众多存储器、3D图形卡、LCD显示、DTV接口和机顶盒等。

JEDEC定义了3种SSTL标准:EIA/JESD8-8 3.3V SSTL(SSTL 3);EIA/JESD8-9B 2.5V SSTL(SSTL 2);EIA/JESD8-15 1.8V SSTL(SSTL 18)。

ECL差分信令能提供比其他任何逻辑更短的传播时延和更高的切换速率。有的器件每个差分对能够传输12Gbps的数据率,应用在高速测试仪器、光纤网络仪器、超高速路由器、网络存储设备、10 Gb以太网、企业计算服务器和高性能工作站等。

CML(Current-Mode Logic)信令属于ECL工艺,广泛应用于新型高速器件,应用于网络物理层和SerDes器件。CML串行差分信令数据率为1~10Gbps,速度取决于驱动器和接收器的生产工艺技术。

应用部分,硬件工程师很关注,信号完整性方面,我们更关注相关逻辑电路在实际版图的设计,相关规则:1.走线阻抗匹配;2.对称性走线;3.减少过孔数量及相关不连续点;4.走线角度……都是关于管控信号完整性的高速设计的相关规则。未来高速设计的规则会成为一种常态,如何在设计中管控和取舍,这里就不过多展开了。

审核编辑:刘清

-

高速数字化仪的技术原理和应用场景2024-10-21 3984

-

信令测试仪器的技术原理和应用场景2024-10-31 3637

-

MOS管的应用场景2018-11-14 6519

-

简单总结一下电容和二极管应用场景和选型方式2022-02-11 1096

-

总结一下OpenCV遍历图像的几种方法2023-01-18 2443

全部0条评论

快来发表一下你的评论吧 !