将FPGA技术与mcu相结合单芯片解决方案

控制/MCU

描述

嵌入式设计人员花费大量时间为手头的任务寻找合适的微控制器 (MCU)。通常,空间是一种约束,原始性能、I/O、内存资源、功耗和外围设备的正确组合成为寻找合适的圣杯。

如果您具有特定设计所需的特殊逻辑,则搜索会变得更加复杂。也许这是一种“秘方”,您的公司比任何人都知道如何做得更好,并使最终产品脱颖而出。在这种情况下,很可能没有人按照您想要的方式制造 MCU。

还有另一种选择:协同 MCU 和 FPGA 配对。高度密集的 FPGA 可以吸收如此多的逻辑,以至于它们可以与微控制器甚至内部微控制器结合,从而比单独使用任何一个部分做得更多。此外,您的逻辑的专有本质隐藏在 FPGA 内部,不会被窥探。

本文讨论了允许设计人员将 FPGA 技术与嵌入式处理器相结合的几个选项。我们将研究单片方法、片上系统 (SoC) 解决方案、堆叠和模块。

单芯片解决方案

可以使 Micros 运行得非常快。我们都熟悉触手可及的数千兆赫处理器。然而,更快的处理器通常成本更高且更难实现。PCB 走线变成了传输线,需要严格的阻抗控制,尤其是在关键路径信号上。并非每个设计都能承担使用此类设备进行开发的成本和时间。

这使得以较低速度运行的成本更低、更通用的处理器成为我们设计的替代、更经济的选择。对于要求不高的应用,仅此一项就很好,但是当对速度的需求超过了微型的周期时间时,我们就不得不做出选择。基于软件的方法无法与功能的硬逻辑实现的速度竞争。您可以在板上使用离散逻辑,或将处理器内核与纯逻辑资源(如 FPGA)耦合。

虽然使用更简单、不太复杂的处理器可以相当容易地设置、控制和监视实时控制和状态机设计,但有时需要更高端的外围设备、更宽的数据路径、更高的安全性和更快的执行速度需要。这种级别的处理器马力的一个很好的例子是Micro Semi SmartFusion2系列部件,例如M2S050T-FGG896,它实际上是基于 SoC 的,将硬核 IP 块和 FPGA 结合在一个芯片上。通过利用器件内的硬核 IP,工程师可以在最小的硅片空间内最大限度地利用许多系统共有的功能资源,同时为使用 FPGA 结构和固件的设计定制提供充分的灵活性。

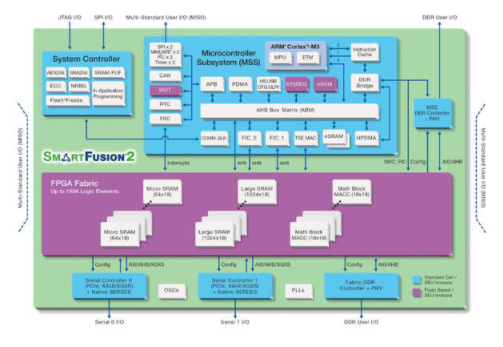

166 MHz ARM® Cortex™-M3 处理器内核与许多高端外设(如 CAN、以太网、PCI Express、SERDES 和 DDR 功能)相结合,同时耦合到基于 Actel 闪存的 50-Kgate 逻辑模块(图 1)。

图 1:166 MHz ARM 内核提供了一个具有良好性能的通用平台。在与嵌入式 50-Kgate FPGA 逻辑架构交互时,它可以跟上更高速度和更高要求的任务。逻辑结构为内核提供硬算术块以及可定制的外设功能和 RAM 资源。

ARM 低功耗内核与 Actel 的 Flash Freeze 实时电源管理系统相结合,可实现 1 mW 的待机功率额定值,而在所有 50 K 四输入基于查找表的逻辑时仍可达到令人印象深刻的 10 mW 功耗元素通电。

SmartFusion2 部件针对军事、航空和太空应用,并被吹捧为高可靠性,并通过使用免疫零 FIT 闪存单元、受保护的存储器和 ECC/EDAC 保护来防止单事件故障发生。256 位和 384 位高级加密标准 (AES) 和安全散列算法 (SHA) 的加密利用非确定性随机位生成器来防范可预测的加密代码。

模块化解决方案

模块化解决方案也是一个有价值的选择,可以使用低速处理器或高端尖叫器。虽然模块的成本通常高于单芯片解决方案,但它们提供更快的上市时间和原型周期、低风险的处理器引擎以及通常成熟且功能齐全的开发工具。当需要推出自己的产品以降低成本时,它们也可以用作参考设计。

可轻松用于原型设计的模块化解决方案的一个很好的例子是DLP Designs的 DIP 封装DLP-FPGA模块(图 2)。在这里,USB 链路控制器内的专用处理器只是充当 Xilinx XC3S250E 250-Kgate Spartan® 3E FPGA 的网关。它使用内置的配置加载器,并且本身可以是一个开发工具。可以使用来自 USB 或目标板的电源,该模块包含稳压器、RAM 和 SPI 闪存,用于在上电时自动配置。

此 DIP 外形模块上的专用处理器可轻松进行基于 USB 的编程和调试。FPGA 基本上可以免费运行您的设计。

此外,基于 Mac、PC 和 Linux 的系统可以通过 USB 端口连接以对 FPGA 进行编程并配置 40 个 I/O、板载 128 Kx8 SRAM 和 SPI 闪存。这部分已准备好进行逻辑综合,并使用数字时钟管理器来确保干净、低偏差的内部信号。包括培训和教程,以帮助您完成在 FPGA 中设计、加载和运行设计的过程。

信号处理模块

对于信号处理,自适应或自修改设计可能需要将高速乘法和累加功能与足够快的处理器相结合,以便在数字域中模拟模拟世界。Critical Link

的L138-F1-236-RL MITYDSP (图 3)是具有两个处理器的模块化示例,TI 的 OMAP-L138 双核应用处理器提供 456 MHz ARM926EJ-S MPU 与 456 MHz 浮点 TMS320C674x 紧密耦合VLIW DSP 以及 Xilinx Spartan-6 XC6SLX45 FPGA,具有多达 6,822 个 6 输入查找表逻辑元件,支持超过 1 GHz 的数据速率。它旨在插入标准 SO-DIMM-200 接口,并可在 –40° 至 +70°C 扩展温度环境中运行。

两个高性能处理器(一个 DSP)和一个高速 FPGA 在这个紧凑的 SO-DIMM 模块上紧密耦合,只需插入更多模块即可扩展性能和并行处理应用程序。

这是一个功能非常强大的小模块。板载 10/100 EMAC MII/MDIO 以太网接口、两个 USB 端口、SATA 和 MMC/SD 存储卡接口、视频输入和视频输出,以及 96 条 I/O 线。JTAG 开发通道可让您快速加载、测试、仿真和调试您的设计。处理器环境支持 QNX、Linux、Windows 和 ThreadX 实时操作系统 (RTOS),并具有大量闪存(512 MB 的 NAND 和 8 MB 的 SPI NOR)和 RAM(256 MB 的 DDR2)。

这些处理器和逻辑引擎的模块化特性意味着可以将多个单元插入单个主板,以实现可扩展、可扩展和并行处理的应用。

另一个设计用于并行处理环境的模块可通过使用 Cogniblok-4K Neuron 处理器的 Cogniem 901-1001 SDK 开发板进行测试和开发。这些是可配置和可堆叠的模式识别模块,旨在并行处理复杂任务,如模式识别和运行流程密集型算法。人工智能处理器和 FPGA 与Everspin Technologies

的 4 MB High-Rel Magneto RAM(MRAM,基于巨磁电阻,不受 EMI、RFI 和 EMP 条件影响)的组合让这些模块以并行、多轴配置互连,以执行认知计算、传感器融合、视频分析等。一旦管道被填满,复杂的任务就可以虚拟实时完成。一个独立的 USB 协处理器将电路板桥接到 USB,以便快速开发和下载。

总之,micro 与 FPGA 的结合可以实现高度的灵活性和性能,并简化更新。这对于自适应算法、开发新技术以及在您希望随着学习曲线的上升而改进算法或过程技术的任何设计特别有用。

-

ARM7与FPGA相结合的应用2008-06-17 4739

-

Airfast射频功率解决方案2013-07-02 2587

-

桥接电机控制和高级通信的单芯片驱动器解决方案2018-12-29 2903

-

采用16-bit MCU的超低功耗运动检测系统解决方案介绍2019-07-19 2464

-

基于FPGA单芯片实现ARM系统设计解决方案2021-07-12 3844

-

FPGA实现ARM系统处理的解决方案解析2021-07-14 4044

-

错过后悔的MCU微型打印机解决方案2021-11-01 1820

-

嵌入式Linux和Java技术相结合的开发环境2021-11-04 1149

-

FPGA与SRAM相结合完成大容量数据存储2010-02-06 619

-

利用OTP技术的CSOC单芯片解决方案2010-04-13 1446

-

人工智能和模拟功率分析相结合的网络安全解决方案2018-11-23 3949

-

工业控制中ARM7与FPGA相结合的应用2019-09-04 1639

-

以太网与数字电网相结合的解决方案2020-01-04 1681

-

OpenHarmony Dev-Board-SIG专场:打造MCU+语音的智能家居单芯片解决方案2021-12-28 2175

-

英飞凌推出PMG1-B1 PD MCU的单芯片解决方案2023-04-04 1097

全部0条评论

快来发表一下你的评论吧 !