系统芯片设计—系统总线(System Bus)

电子说

描述

系统总线(System Bus)是系统芯片中各个设备(如嵌入式处理器,存储器和外设等IP核)之间通信与互连的公共硬件通道,其为设备间访问共享硬件提供了一种互连机制,在数字系统中承担数据传输的任务。

系统总线连接的设备根据功能的不同分为主设备和从设备。主设备指可以主动发起传输任务的设备。例如,处理器可以通过总线控制外设,读/写数据;一些外设也可以通过总线访问其他外设,读/写数据。从设备是响应主设备发起的传输任务的设备。例如,存储器响应主设备的读操作,返回读数据。此外,一些设备既可以作为主设备主动对总线发起访问,又可以作为从设备被动响应总线事务。

系统芯片中,通常设计多个主设备和多个从设备。不同的从设备在总线上对应着互不重叠的地址区间,总线通过主设备发起传输任务的目标地址。不同总线协议会设计不同的主设备访问方式。例如:AMBA 2.0协议中规定,同一条AHB(Advanced High Perfoormance Bus)总线上的设备共享固定的地址数据传输通道,这意味着其中一个主设备占用AHB总线后其余主设备均处于等待状态;而AMBA 3.0协议中的AXI总线则使用不同的ID号来区分主设备,主设备可以在其他主设备的访问未完成的情况下继续发起请求。

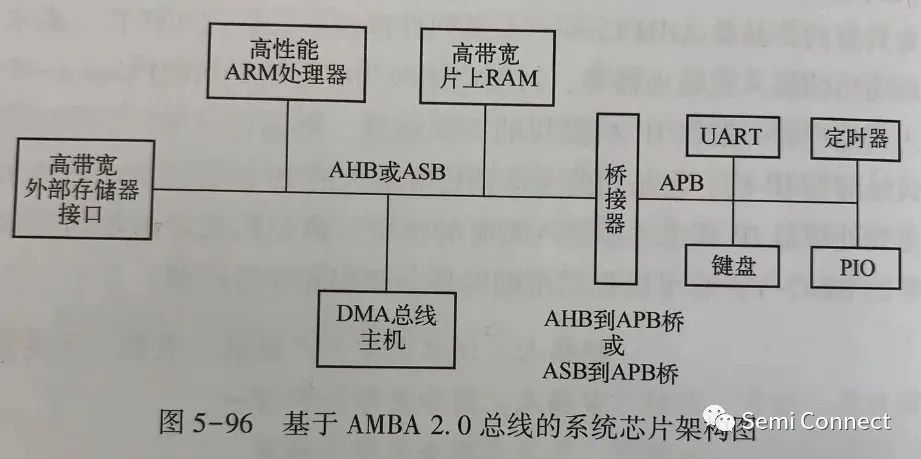

一个基于AMBA 2.0总线的系统芯片架构如图5-96所示。AHB总线连接嵌入式处理器和存储器等高速设备,APB总线连接串口,定时器等低速设备。总线仲裁机制包括轮询机制和优先级机制。总线在传输数据时,可以采用不同的传输类型以适应不同长度和速度的传输需求。高性能ARM处理器是系统的主设备,它可以通过AHB总线访问高带宽的外部存储器接口和高带宽片上RAM,也可以通过桥接器访问APB总线上的低速设备UART,键盘,定时器和PIO等。

根据工作频率的不同,总线被设计为高速总线和低速总线:高速总线支持较高的时钟频率,拥有较高的数据带宽和性能,但功耗也较高,一般适用于CPU和DMA等高速设备的连接;低速总线工作频率较低,虽然性能较差,但功耗较低,适合挂载键盘,串口等低速外设。高速总线和低速总线之间可以用过桥进行连接通信。目前,业界系统芯片中较有影响力的总线包括AMBA总线,CoreConnect总线,Wishbone总线和OCP总线等。

审核编辑 :李倩

-

CW32系统总线有哪些?2025-12-15 103

-

嵌入式系统总线2021-12-22 990

-

总线矩阵是如何对系统总线和DMA进行仲裁的2021-11-08 2103

-

什么是总线系统2021-09-10 1412

-

AHB系统总线分类2021-08-20 2445

-

AHB系统总线2021-08-12 2310

-

系统总线是什么_系统总线分为哪三类2019-11-15 59581

-

请问什么PSoC组件与系统总线时钟同步?2019-09-11 1524

-

系统总线测量该怎么使用?2019-08-14 1604

-

系统总线的类型2018-11-27 15559

-

使用系统总线测量和改善嵌入式系统的性能2012-03-28 1109

-

机电综合管理系统总线控制仿真软件设计2009-10-23 4198

全部0条评论

快来发表一下你的评论吧 !