CAST与它最受欢迎的IP

电子说

描述

CAST专注于开发,销售和支持各种用于ASIC或FPGA的数字硅IP内核。电子系统设计人员使用这些IP能够缩短开发周期并降低量产风险。

CAST自1993年成立以来,一直专注于可重用IP内核业务。我们已经帮助全球成千上万的公司获得了竞争优势。他们使用我们的IP已经制造出了数十亿个出货产品。我们三分之一的销售额都是来自于再次使用的客户。

CAST为系统设计师提供了独特的CAST IP使用体验:

·优秀的IP产品:由我们的工程师或者相关应用领域出色的紧密合作伙伴开发完成;

·无与伦比的技术支持:所有售前和售后支持都由经验丰富的IP销售和工程团队(包括IP 实际开发人员)提供;

·灵活的许可方式:可以满足各个项目的不同要求。

CAST的IP产品覆盖了从前沿技术到传统的基于标准的各种功能。

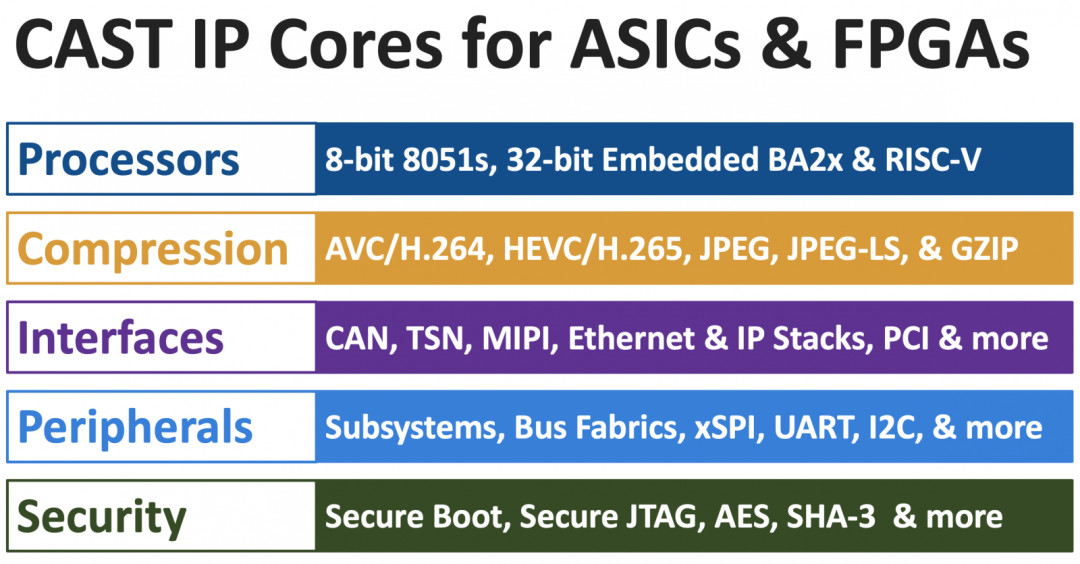

CAST Products Overview

这类数字IP可提供用于ASIC设计的可综合RTL,也可提供常用FPGA上的网表和结构化ASIC。

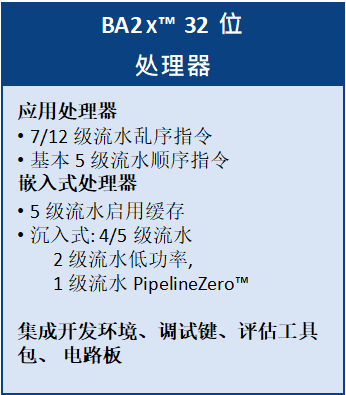

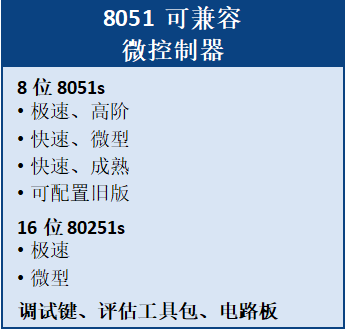

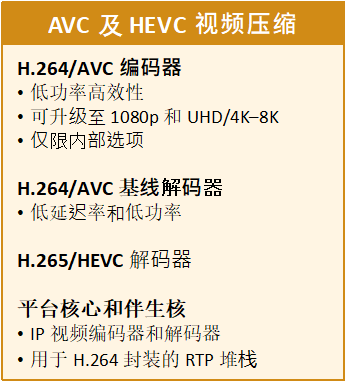

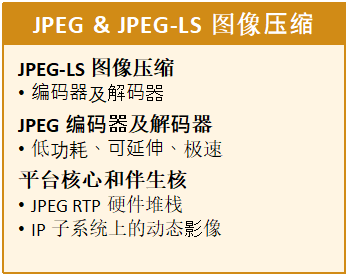

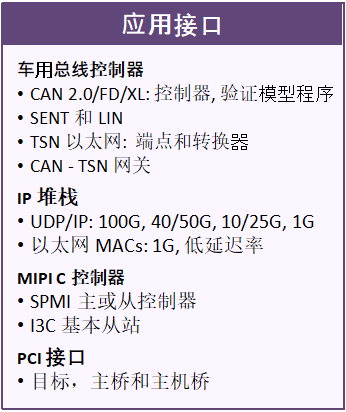

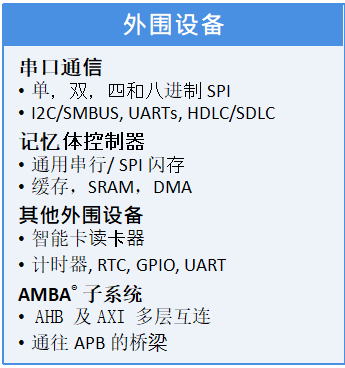

按照上面导航菜单中的分类方式,我们的IP包括:8位,16位和32位控制器和处理器;数据,视频和图像压缩;基于标准的接口;常用的外设;以及系统安全和加密单元。

重点产品包括:

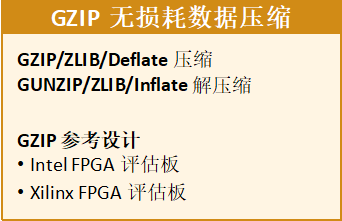

·吞吐速率超过200Gbps的GZIP内核;

·经多次量产验证的,ISO26262认证的CAN和TSN控制器;

·高效能的视频和图像编解码器;

·代码密度高和低功耗的32位处理器和可靠的8051微控制器;

·完全硬件化的UDP / IP堆栈,可用于超过100Gbps的媒体流;和

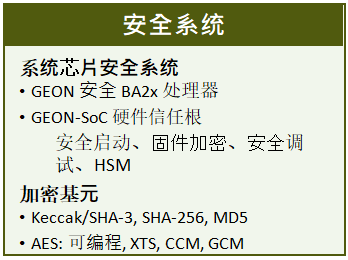

·完整的SoC安全解决方案。

每个IP产品都采用了最佳实践的编程规范进行开发。并且经过严格的验证以求达到质量和标准的一致性;我们的大多数IP产品都经过了多次量产验证。

非常易于集成,交付的内容包括完整的文档以及我们25年来不断完善的各种可重用的辅助工具。许多内核还提供评估板,预集成子系统和验证IP。

多元化的IP应用

公司丰富的产品线能满足不同客户的特定需要,由前端创新IP核以至标准可靠的基本技术均一应俱全,当中包括为专用集成电路而设的可综合RTL设计、专为FPGA而设的网表以至系统化专用集成电路。

易于使用及集成

CAST IP的设计始终贯彻易于使用,便于整合及验证的方针。

公司可交付产品包括高质量代码、详尽文档、开发支持,如仿真模型、测试用例及处理器调试介面及集成开发环境。

参考设计可简化售前评估,大部分IP核均提供验证模型程序。

经验证品质可靠产品

CAST 十分注重质量标准,所有IP产品在推出市场前均需通过严格测试。除了进行仔细的内部检测,我们亦参与业内互操作性测试活动,亦与知名半导体公司合作,以保持产品的高运转性及融合畅顺性。由於公司经已为众多客户在数以百计应用领域设计及生产数以亿计的IP 核,我们的方案绝对可靠。

卓越支持

CAST所提供超卓的客户支持在业内享负盛名,我们的目标是帮助客户取得最大的成功,我们不单是销售IP,而是以公司的经验及资源,助您逐步实现目标。

CAST最受欢迎的IP之一

CAN-控制器

CAN 2.0, CAN FD & CAN-XL 总线控制器

实现了一个CAN总线控制器,该控制器根据CAN 2.0,CAN FD和CAN XL规范执行串行通信。它支持最初的Bosch协议和ISO 11898中定义的和ISO规范(包括ISO 19898-4中定义的时间触发操作(TTCAN)),并且经过优化以支持流行的AUTOSAR和SAE J1939规范。

CAN协议为网络节点之间传输的帧采用了多主控总线配置,并在不增加主处理器负担的情况下进行错误处理。该内核使用户可以在各个组件之间建立经济可靠的链接。它对主处理器来说是一个内存映射I / O设备,它访问CAN内核来控制帧的发送或接收。

CAN内核易于使用和集成。具有可编程的中断,数据和波特率。可配置数量的独立可编程接收滤波器。;以及通用处理器接口或可选的AMBA APB或AHB-Lite接口。它实现了灵活的缓冲方案,允许对内核大小进行微调以满足每个特定应用程序的需求。

接收缓冲区的数量是综合时可配置的。实现了两种类型的发送缓冲区:高优先级的主发送缓冲区(PTB)和低优先级的辅助发送缓冲区(STB)。PTB可以存储一条消息,而STB包含的缓冲区段数量是综合时可配置的0到16个区段。

该内核实现了类似于飞利浦SJA1000以及PeliCAN扩展模式的功能。并提供了错误分析,诊断,系统维护和优化的功能。

CAN内核已在多个量产设计中得到了广泛的验证和检验。

支持CAN规范

CAN 2.0和CAN-FD(ISO 11898-1.2015,以及较早的ISO和Bosch规范)

CAN XL(CiA 610-1规范)

TTCAN(ISO 11898-4 1级)

针对AUTOSAR和SAE J1939进行了优化

增强功能

错误分析功能可实现诊断,系统维护和系统优化

上次错误类型

仲裁丢失位置

错误警告限制

仅侦听模式可实现CAN总线流量分析和自动的比特率检测

回环模式进行自我测试

支持时间戳,符合CiA的603规范

可选的ECC存储器支持

灵活的消息缓冲和过滤

可配置的接收缓冲区数

1个高优先级发送缓冲器

可配置数量的低优先级发送缓冲区

FIFO或优先级模式的发送缓冲器

可配置数量的独立可编程29位接收滤波器,1至16

易于使用和集成

可编程数据速率,带有CAN 2.0的高达1 Mbit / s,带有CAN FD选项的高达几个Mbit / s

可编程波特率预分频器:1至1/256

单发传输模式,可降低软件开销并快速重新加载传输缓冲区

可编程中断源

通用的8位主控制器接口和可选的32位AMBA-APB或32位AHB-Lite

安全功能(可选)

SO-26262 ASIL-B就绪:为SRAM实现了ECC,为内部逻辑保护实现空间冗余

根据要求提供ISO-26262 ASIL-C

零风险

兼容任何支持ISO-11898的CAN2.0收发器(PHY),以及NXP,MicroChip,OnSemi,Infineon等的各种收发器(PHY)。

经多次量产检验

高效便携的设计

提供RTL,可移植到ASIC和FPGA技术

CAN-CTRL内核可以集成在使用CAN或基于CAN的更高层通信协议的设备中。除了传统的汽车应用外,此类设备还用于工业(例如CANopen和DeviceNet协议),航空(例如ARINC-825和CANaerospace协议),船舶(例如NMEA 2000协议)和其他应用中。

内核包括成功实现设计所需的一切资料:

VHDL或Verilog RTL源代码

综合后EDIF(网表许可)

测试平台

行为测试

综合后验证

仿真脚本

综合脚本

Linux驱动

文档

审核编辑 :李倩

-

[投票评选]2025电子发烧友开发板测评大赛--最受欢迎开发板2025-10-13 3613

-

最受欢迎的编程语言、IDE和数据库都是哪些2020-07-18 2578

-

预测:2012年最受欢迎消费性移动应用Top 102009-11-27 462

-

预测12年最受欢迎消费性移动应用Top 102009-12-01 855

-

2010年最受欢迎的10项Android应用2010-10-29 688

-

最受欢迎的Windows Phone 7应用top102011-07-11 850

-

iPhone6s去年出货量全球第一 成最受欢迎手机2017-03-23 1181

-

DAP 调查:Manjaro荣获最受欢迎的Linux 发行版2018-04-24 2111

-

十大最受欢迎的Linux发行版2020-09-07 5701

-

v2004、1909已成最受欢迎和最稳定的win10版2020-11-27 5151

-

Netflix上最受欢迎的电视节目和电影将不再是公司的秘密2020-12-18 2702

-

多款Intel 9代酷睿斩获最受欢迎CPU大奖2021-01-19 3030

-

Oculus Quest 2已成最受欢迎的VR头显2021-03-08 4667

-

苹果13哪个颜色最受欢迎2021-09-22 62347

-

来自科幻中最受欢迎的PCB灵感机器人之一2022-07-25 649

全部0条评论

快来发表一下你的评论吧 !