芯片设计之逻辑综合过程

电子说

描述

工程师通过逻辑综合过程,将代码转化为电路图,聘请sysnopsys公司的综合工程师需要每天付费约1500美元。

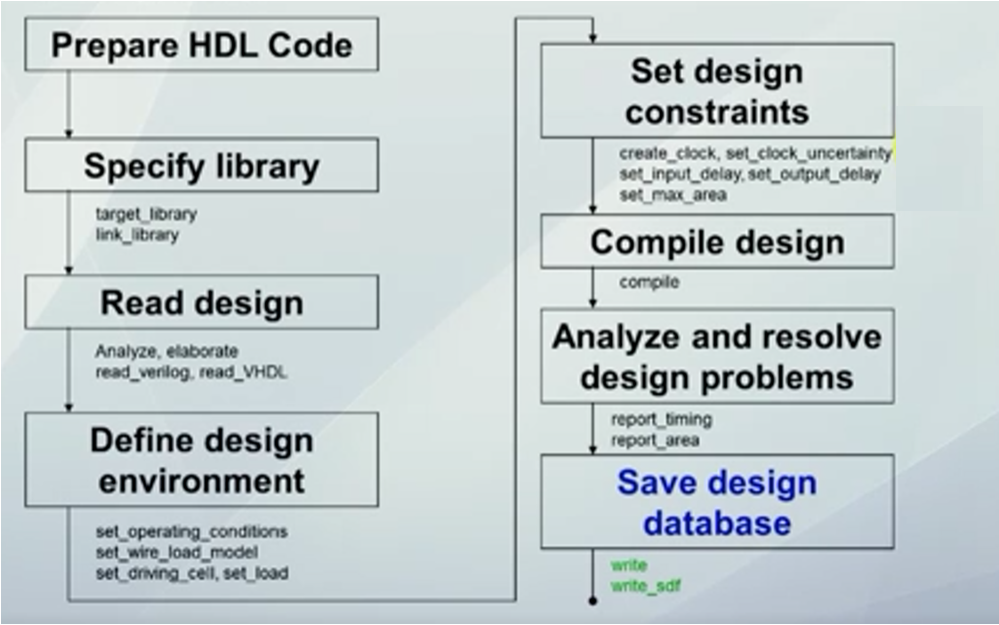

基本逻辑综合过程如下:

(1)完成代码编写(Prepare HDL Code)。

(2)描述库(Specify library),如标准单元(由其他设计人员完成的功能模块,可直接在新的芯片设计中使用)的描述。

(3)读取设计(Read design),读取设计可以检测代码是否可以转化成电路和转化电路过程中是否有问题。

(4)定义设计环境(Define design environment),需定义芯片工作的环境,芯片外部信号由哪些其他芯片提供,芯片为哪些其他芯片提供信号。

(5)设置约束(Set design constraints),包括对芯片时钟频率的描述、输入接口信号时序的描述、输出接口时序的描述、对面积的要求、对功耗的要求等。

(6)逻辑综合操作(Compile design),根据芯片的复杂程度,逻辑综合操作的时间可能是几秒,也可能是半个月。如果设计环境和约束设置不当,逻辑综合操作的时间会被延长。

(7)分析结果(Analyze and resolve design problems),逻辑综合操作结束后,计算机会输出门级网单(电路)及门级网单的时序、功耗等参数。如果输出结果与设计要求偏差在20%以内,可以通过修改设计环境(4)和约束(5),做进一步优化。如果偏差较大,需要返回过程(1)代码编写,重新修改芯片设计代码。

(8)保存结果(Save design database)当门级网单符合设计要求,可以将结果保存。所设计的门级网单和设计相关的时序信息都需要保存。

图片来源:学堂在线《IC设计与方法》

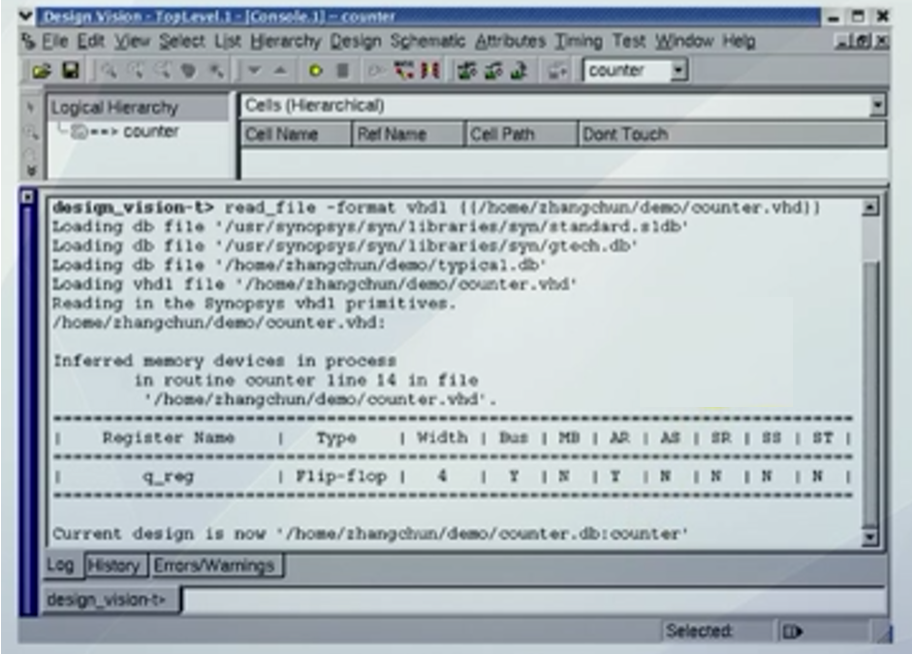

过程(3)读取设计,工程师需要详细检查软件给出的报告,检查代码是否有疏漏。

图片来源:学堂在线《IC设计与方法》

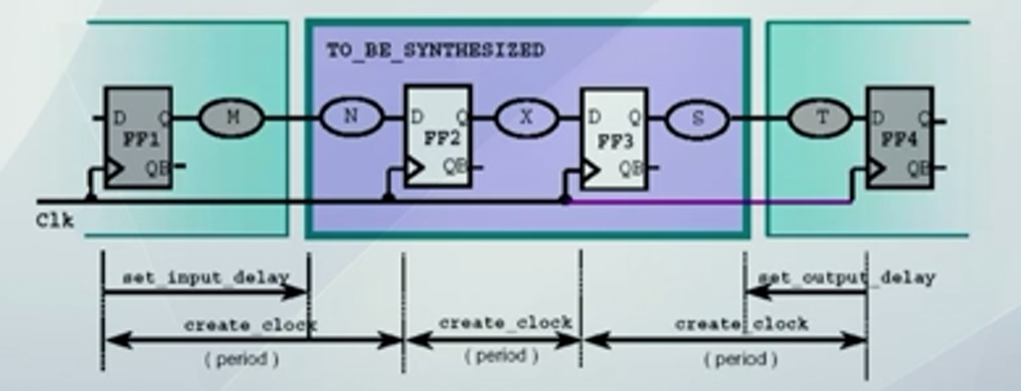

过程(5)设置约束包含时序和面积的约束,通常时序约束的优先级更高。

对于下图X路径(只涉及内特性)的约束,设计人员可以通过约束两个触发器(FF2、FF3)的时钟周期令软件计算出X路径的延时,完成对X的约束。因为软件可以提取Clock to Q和Set up的时间,根据时钟周期>Clock to Q+穿越组合逻辑电路的最长延时+Set up公式,可计算X路径的延时。

对于下图N、S路径(涉及电路外特性),设计人员可以通过约束外部信号输入和外部电路稳定装载输出信号的延时分别对N和S(S在紫色的框右侧的椭圆中,有些模糊)约束。

图片来源:学堂在线《IC设计与方法》

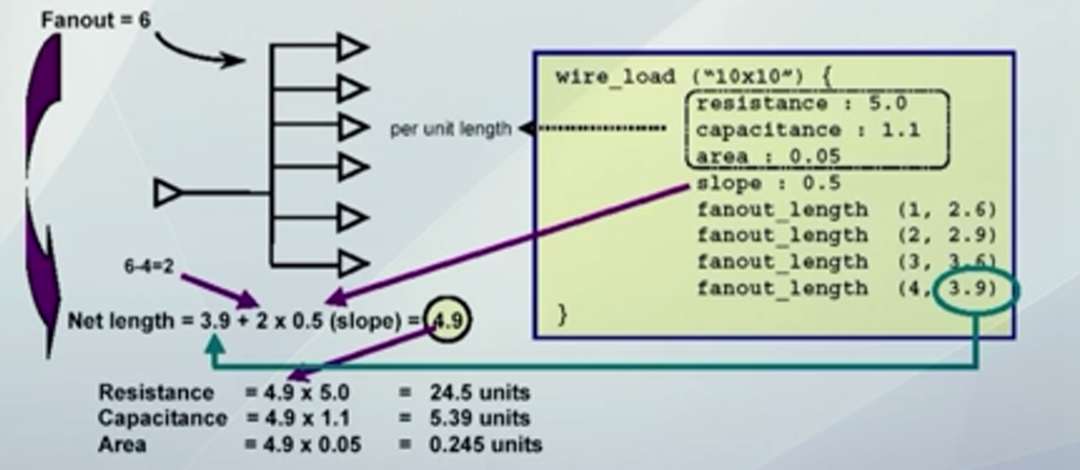

描述时序约束还需关注电路中的连线描述,因为在逻辑综合阶段,连线未确定,因此采用估计的方式得出连线电阻、电容、面积。

假设一个元器件有6个负载(Fanout=6),下图中黄框内fanout length表示负载个数对应的连线长度(Net lenght)。

对于6个负载(超过4个负载)的情况,采用公式:

Net lenght=3.9+2*0.5

上式中“2”表示超过4个负载的数量,“0.5”从黄框中显示的slope等效长度得出。

估算出连线长度后,乘以黄框中电阻(resistance)、电容(capacitance)、面积(area)对应的参数,估算出芯片连线的电阻、电容、面积。

图片来源:学堂在线《IC设计与方法》

审核编辑 :李倩

-

逻辑综合的流程和命令简析2023-08-09 2043

-

【「龙芯之光 自主可控处理器设计解析」阅读体验】--LoongArch逻辑综合、芯片设计2026-01-18 831

-

浅谈IC设计中逻辑综合2013-05-16 5995

-

求一套手工逻辑综合的方法和综合步骤?2021-04-08 1284

-

DC逻辑综合详解2021-07-29 1188

-

什么是逻辑综合?2021-11-02 3389

-

DC逻辑综合2011-12-29 903

-

逻辑漏洞之越权详解2017-09-07 1009

-

ASIC逻辑综合及Synopsys Design Compiler 的使用资料说明2019-10-23 1049

-

芯片设计之ASIC设计流程和逻辑综合2022-08-12 6491

-

芯片设计之逻辑综合过程(下)2022-08-15 2667

-

逻辑综合与物理综合2022-11-28 3954

-

EDA逻辑综合概念 逻辑综合三个步骤2023-06-19 4470

-

eda综合有哪些类型 逻辑综合的原理2023-06-26 3228

-

什么是逻辑综合?逻辑综合的流程有哪些?2023-09-15 8286

全部0条评论

快来发表一下你的评论吧 !