PLD的设计流程

电子说

描述

课程中运用Quarus Ⅱ工具讲解可编程器件PLD的设计流程,Quarus Ⅱ工具是Altera公司的产品。同时课程说明了针对Xilinx公司的ISE工具的PLD设计流程也是相似的。

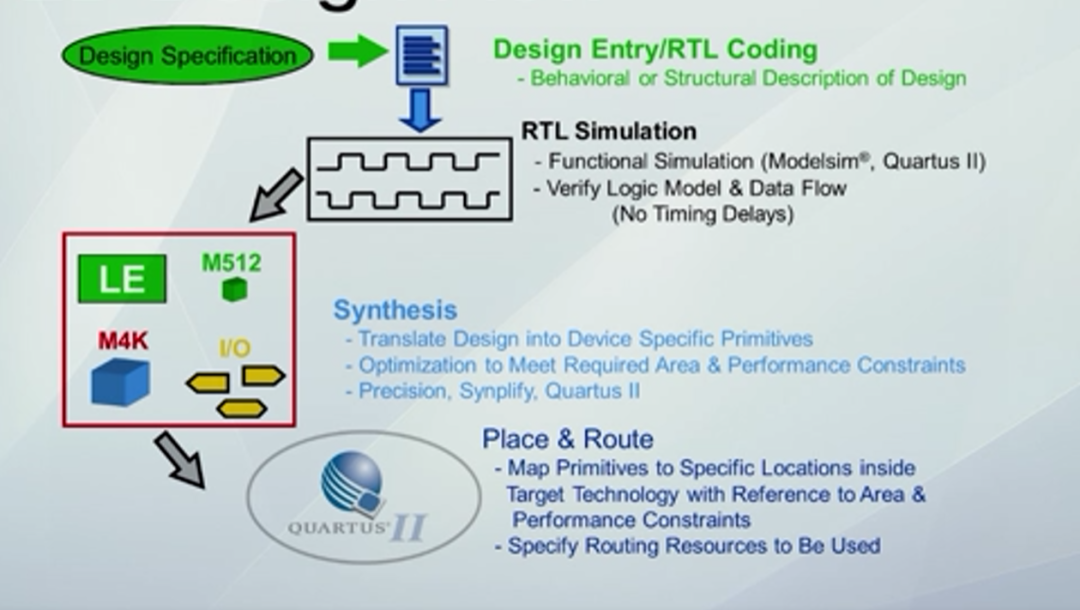

PLD的设计流程与ASIC(专用集成电路)的设计流程类似,具体设计流程如下:

(1)明确设计需求(Design Entry)。根据设计需求,在RTL的结构层次(运用Verilog代码设计芯片的一种方式)完成电路设计(RTL Coding),完成初始Verilog代码。

(2)RTL级的电路仿真(RTL Simulation)。进行仿真的工具既可以运用Altera公司的Quarus Ⅱ内嵌仿真工具,也可以运用Modelsim仿真工具(课程中讲解的仿真工具)。验证代码是否满足设计要求,这一阶段的验证没有时序相关信息,即未考虑器件延时。

(3)逻辑综合(Synthesis),将RTL级代码映射成具体的器件实现电路设计,生成对应的门级网单(芯片设计中间阶段的电路图)。

(4)布局和布线(Place&Route),将逻辑综合过程中使用的元器件替换成Altera公司提供的元器件,并在电路内布线,完成电路连接。

PLD的逻辑综合与布局和布线两个步骤可以运用Altera公司提供Quarus Ⅱ工具一步完成,其他公司提供的PLD设计工具也可以一步完成上述两个步骤。

图片来源:学堂在线《IC设计与方法》

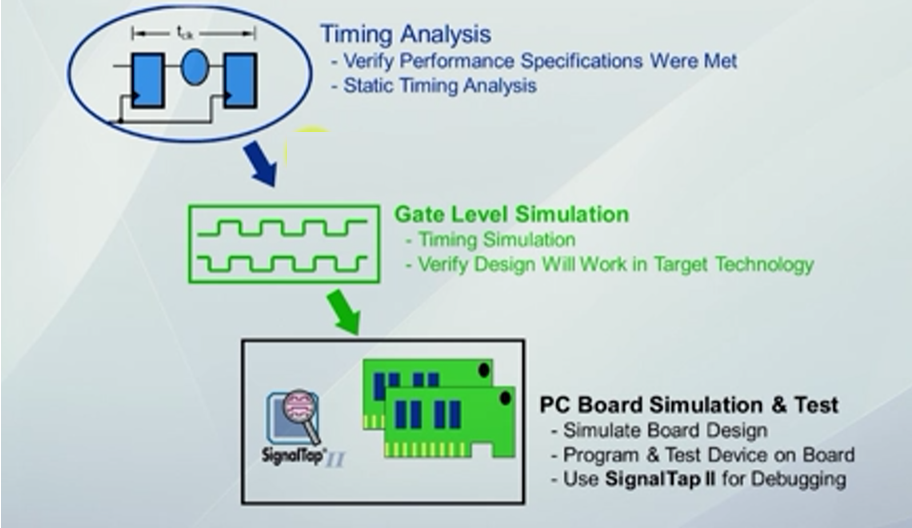

(5)时序分析(Time Analysis),证明电路性能满足时序要求。

ASIC的设计流程中时序分析步骤在门级仿真步骤后进行,这是因为ASIC设计工具功能限制的原因,门级仿真中的时序只能采用估算的方式得出。

Quarus Ⅱ工具集成了时序分析功能,时序分析可以方便地进行,所以PLD设计流程的时序分析步骤先于门级仿真步骤。

在芯片设计中,如果时序不能满足要求,如计数器的要求是100MHz,但设计出的计数器只能满足10MHz的要求,即使门级仿真的结果正确,也不能满足设计需求。所以在条件允许的情况下,时序分析步骤先于门级仿真步骤。

(6)门级仿真(Gate Level Simulation),门级仿真结果满足要求,说明电路满足设计的功能需求。

(7)电路板仿真和测试(PC Board Simulation&Test)。将经过以上步骤得出的数据流文件下载到可编程芯片中,再将可编程芯片安装到PC板(个人理解:PCB板,印刷电路板,芯片实现对应功能所需安装的电路板)中,进行测试。

图片来源:学堂在线《IC设计与方法》

PLD设计芯片需要进行编译,与一般编程软件的编译目的不同,PLD设计芯片的编译的目的是将RTL级代码转化成物理器件上可以实现的电路。

具体的编译过程有以下几个方面:

(1)前端设计的逻辑综合。

(2)后端设计的布局布线。

(3)后端设计产生的相关输出。相关输出包括:用于时序分析的门级网单、用于仿真的门级网单、对器件编程的配置文件。对器件编程的配置文件可以将没有功能的可编程器件改变为可以实现设计需求的专用器件。

审核编辑 :李倩

-

什么是PLD的定义和应用 PLD与FPGA的区别和联系2025-02-01 7642

-

PLD的优势与劣势分析2025-01-20 2024

-

用VHDL/VerilogHD语言开发PLD/FPGA的完整流程2012-05-21 1753

-

PLD设计方法及步骤2010-09-18 5203

全部0条评论

快来发表一下你的评论吧 !