HPC系统的电源控制器,RISC-V也来插一脚?

HPC系统的电源控制器,RISC-V也来插一脚?

描述

电子发烧友网报道(文/周凯扬)对于近几年推出的HPC系统来说,高能效已经成了大家无法规避的话题,就连TOP500上的超算,比如排名第一的超级计算机,美国能源部下属国家实验室的Frontier系统,也凭借单机柜原型机在GREEN500能效榜上拿下第一,整个系统拿下了第二的成绩。与十多年前的那些HPC系统相比,现在的设计不仅是在性能上不可同日而语,连能效比也提升了百倍以上。

能做到如此高的能效,除了CPU、GPU本身的设计外,也要归功于先进的冷却系统和电源管理。对于已经走向多核异构时代的HPC系统而言,系统级别的电源与热管理尤为重要,而且还得做到精心调校、针对负载进行智能调整的动态电源管理。

已有的电源控制器方案

针对不同的CPU系统,市面上已经有了不少商用电源控制器,比如英特尔的CPU有用于C-States管理的电源控制单元(PCU),ARM有帮助应用处理器卸载电源与系统管理任务的系统控制处理器(SCP)和可管理控制处理器(MCP),AMD有采集传感数据进行快速调整的系统管理单元(SMU),IBM的Power处理器有片上控制器(OCC)等。

然而,不少已有的方案都是基于单核心的MCU打造的,在面对单片核心数越来越多以及逐渐普及的Chiplet设计时,这些方案就因为缺乏扩展性而显得力不从心了。除此之外,主办的尺寸、布局和成本的因素,进一步限制了HPC处理器本身的片上电源管理。正因如此,在拥有庞大核心数量的HPC系统上,我们需要一个可扩展的控制器方案。

在这些要求下,瑞士苏黎世联邦理工学院(ETH)的集成系统实验室就基于开源的RISC-V架构,打造了这样一个拥有并行控制规则计算加速的电源控制器IP——ControlPULP。

可扩展的电源控制器

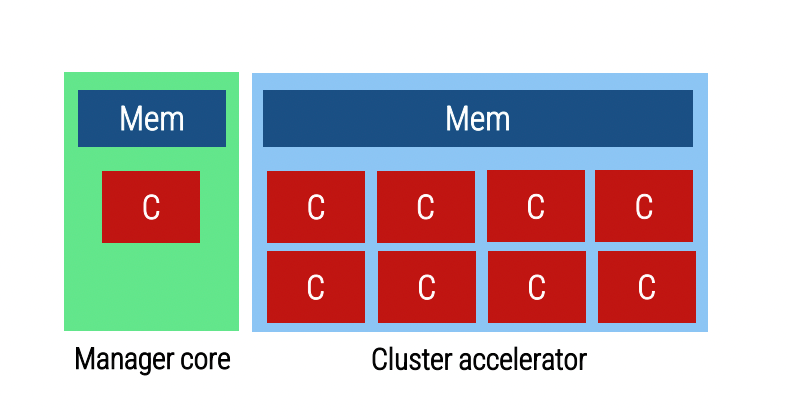

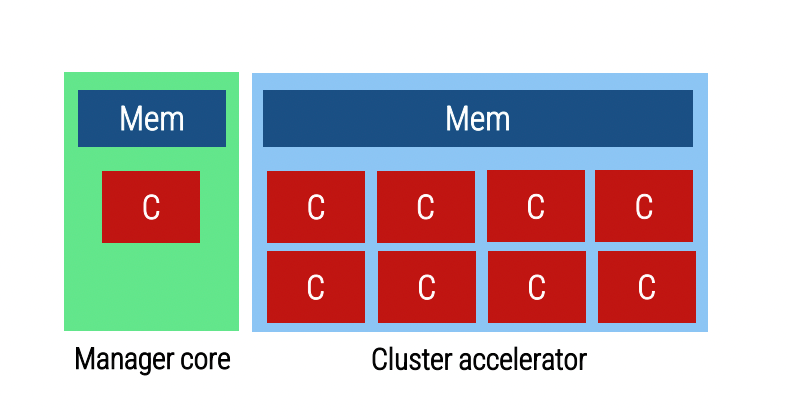

ControlPULP采用了九核的设计,一个单核管理器核心,和8核的加速器簇来加速电源控制固件的工作负载,而这九个核心全部基于CV32E40P,这是一个32位4级流水线的RISC-V开源核心,由瑞士苏黎世联邦理工学院和意大利博罗尼亚大学合作的PULP平台维护,他们也将CV32E40P捐献给了开放硬件联盟OpenHW。

ControlPULP架构 / 瑞士苏黎世联邦理工学院

此外,ControlPULP集成了一个直接内存访问引擎,用于获取片上传感器的数据,还有一个uDMA引擎,用于支持基于标准电源管理接口(比如电压调节总线AVSBUS/PMBUS)的片外外围设备以及通过I2C或MTCP协议的BMC通信。至于底层控制策略的调度,则靠PULP平台自己开发的开源FreeRTOS来实现。

在其电源控制策略中,ControlPULP主要负责两大主要控制任务,一个是定期控制任务,一个是电源控制任务。定期控制任务结合温度传感器、功耗传感器内的数据,以及目标频率、预期负载和总功耗预算等数据,来进行电源调度和热管理。电源控制任务则是通过PMBUS/AVSBUS获得的电压轨功耗和BMC通信来完成快速电源控制。

根据他们测试的结果,这种多核加速器簇的结构相较过去的单核方案来说,在控制策略的执行速度上快了5倍,而且集成在HPC处理器中并不会占用多大的面积。他们在格芯的GF22FDX工艺下得到的综合结果中,ControlPULP所占处理器面积甚至不到百分之一。

开源电源控制器的未来

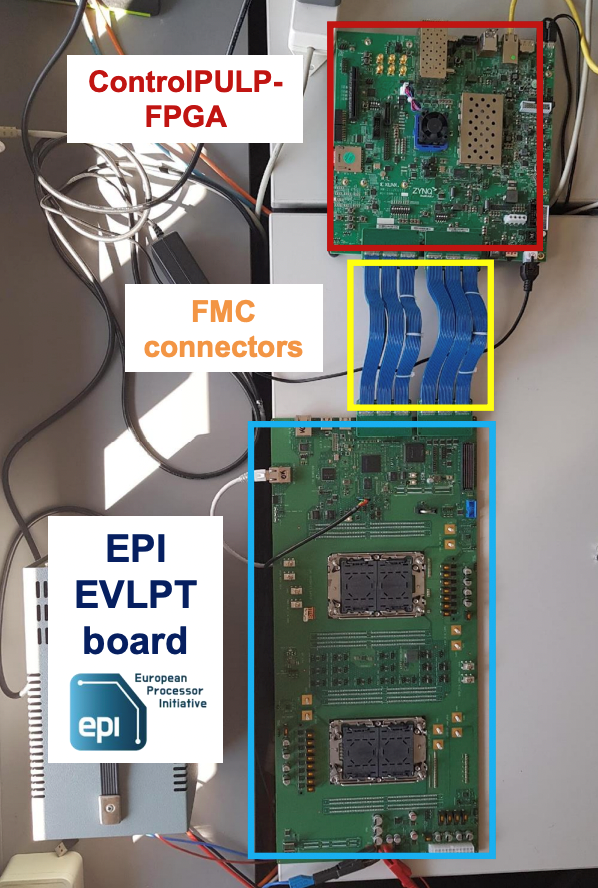

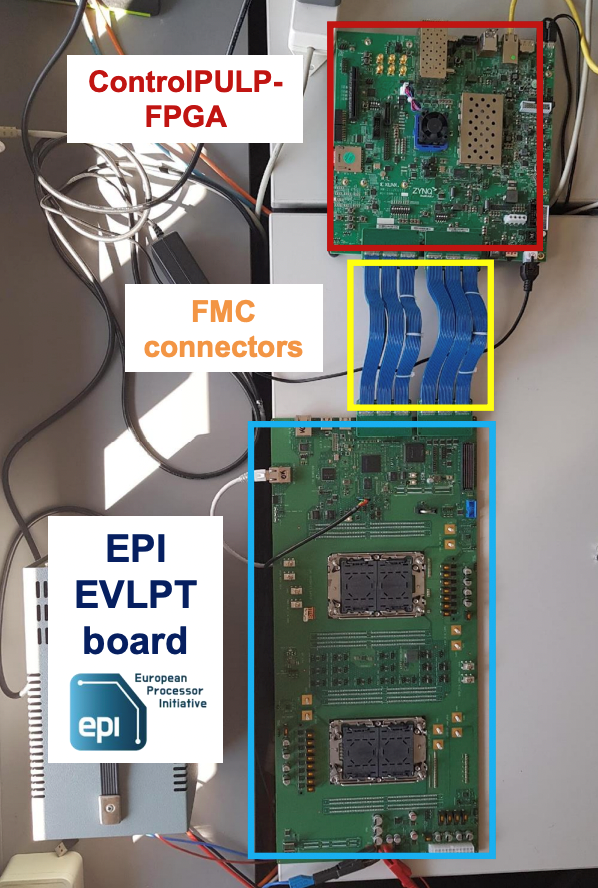

ControlPULP作为一个软硬件完全开源的集成IP方案,不少人担心是否真的会有人将其投入商用,事实上,这样的案例已经快要面世了。根据ETH透露,欧洲处理器计划(EPI)的先行者,法国企业SiPearl的E级HPC芯片,72核的Rhea处理器就将集成ControlPULP。

在Rhea原型主板上进行FPGA仿真验证 / 瑞士苏黎世联邦理工学院

不过,这还只是ControlPULP迈出的第一步,未来PULP团队还计算完成65nm的流片来进一步开展硬件验证,并探索更先进的预测性电源控制策略。但不管怎么说,这都是首个RISC-V的HPC电源控制器方案,RISC-V在HPC市场也需要更多的亮相,而不仅仅只是作为加速器。

打开APP阅读更多精彩内容

能做到如此高的能效,除了CPU、GPU本身的设计外,也要归功于先进的冷却系统和电源管理。对于已经走向多核异构时代的HPC系统而言,系统级别的电源与热管理尤为重要,而且还得做到精心调校、针对负载进行智能调整的动态电源管理。

已有的电源控制器方案

针对不同的CPU系统,市面上已经有了不少商用电源控制器,比如英特尔的CPU有用于C-States管理的电源控制单元(PCU),ARM有帮助应用处理器卸载电源与系统管理任务的系统控制处理器(SCP)和可管理控制处理器(MCP),AMD有采集传感数据进行快速调整的系统管理单元(SMU),IBM的Power处理器有片上控制器(OCC)等。

然而,不少已有的方案都是基于单核心的MCU打造的,在面对单片核心数越来越多以及逐渐普及的Chiplet设计时,这些方案就因为缺乏扩展性而显得力不从心了。除此之外,主办的尺寸、布局和成本的因素,进一步限制了HPC处理器本身的片上电源管理。正因如此,在拥有庞大核心数量的HPC系统上,我们需要一个可扩展的控制器方案。

在这些要求下,瑞士苏黎世联邦理工学院(ETH)的集成系统实验室就基于开源的RISC-V架构,打造了这样一个拥有并行控制规则计算加速的电源控制器IP——ControlPULP。

可扩展的电源控制器

ControlPULP采用了九核的设计,一个单核管理器核心,和8核的加速器簇来加速电源控制固件的工作负载,而这九个核心全部基于CV32E40P,这是一个32位4级流水线的RISC-V开源核心,由瑞士苏黎世联邦理工学院和意大利博罗尼亚大学合作的PULP平台维护,他们也将CV32E40P捐献给了开放硬件联盟OpenHW。

ControlPULP架构 / 瑞士苏黎世联邦理工学院

此外,ControlPULP集成了一个直接内存访问引擎,用于获取片上传感器的数据,还有一个uDMA引擎,用于支持基于标准电源管理接口(比如电压调节总线AVSBUS/PMBUS)的片外外围设备以及通过I2C或MTCP协议的BMC通信。至于底层控制策略的调度,则靠PULP平台自己开发的开源FreeRTOS来实现。

在其电源控制策略中,ControlPULP主要负责两大主要控制任务,一个是定期控制任务,一个是电源控制任务。定期控制任务结合温度传感器、功耗传感器内的数据,以及目标频率、预期负载和总功耗预算等数据,来进行电源调度和热管理。电源控制任务则是通过PMBUS/AVSBUS获得的电压轨功耗和BMC通信来完成快速电源控制。

根据他们测试的结果,这种多核加速器簇的结构相较过去的单核方案来说,在控制策略的执行速度上快了5倍,而且集成在HPC处理器中并不会占用多大的面积。他们在格芯的GF22FDX工艺下得到的综合结果中,ControlPULP所占处理器面积甚至不到百分之一。

开源电源控制器的未来

ControlPULP作为一个软硬件完全开源的集成IP方案,不少人担心是否真的会有人将其投入商用,事实上,这样的案例已经快要面世了。根据ETH透露,欧洲处理器计划(EPI)的先行者,法国企业SiPearl的E级HPC芯片,72核的Rhea处理器就将集成ControlPULP。

在Rhea原型主板上进行FPGA仿真验证 / 瑞士苏黎世联邦理工学院

不过,这还只是ControlPULP迈出的第一步,未来PULP团队还计算完成65nm的流片来进一步开展硬件验证,并探索更先进的预测性电源控制策略。但不管怎么说,这都是首个RISC-V的HPC电源控制器方案,RISC-V在HPC市场也需要更多的亮相,而不仅仅只是作为加速器。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

x86和Arm高性能之争刚起,RISC-V横插一脚2021-10-26 7461

-

国产RISC-V MCU推荐2024-04-17 2263

-

《RISC-V能否复制Linux 的成功?》2024-11-26 925

-

关于RISC-V芯片的应用学习总结2025-01-29 1870

-

基于 RISC-V 的微控制器入门指南2020-08-21 2396

-

RISC-V指令集架构微控制器相关知识2021-12-16 1451

-

【RISC-V专题】国产首创RISC-V安全微控制器CF3310开发板免费试用2022-04-14 3737

-

我了解的RISC-V2023-03-19 1218

-

RISC-V 发展2023-04-14 1074

-

RISC-V,正在摆脱低端2023-05-30 2103

-

RISC-V是什么?如何基于此设计微控制器2020-10-30 1200

-

x86和Arm高性能之争刚起,RISC-V也来横插一脚2021-10-29 3480

-

英特尔与谷歌开始为RISC-V进军数据中心铺路2022-10-09 5467

-

芯来科技正式发布基于RISC-V处理器的HSM子系统解决方案2024-03-11 3069

-

RISC-V迈入HPC市场,性能与生态缺一不可2024-03-23 5333

全部0条评论

快来发表一下你的评论吧 !