MCU—IO口的噪声串扰

MCU—IO口的噪声串扰

描述

内核到 I/O 口的躁声串扰

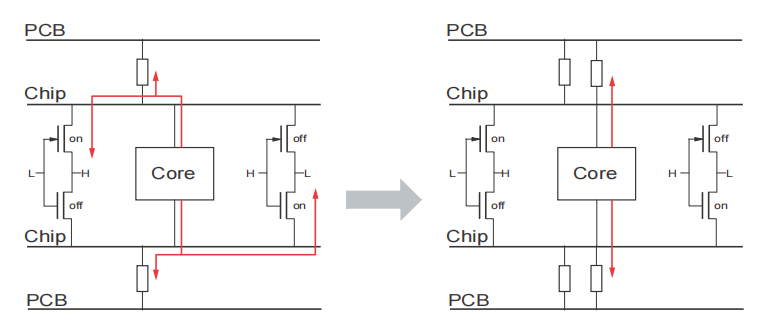

任何两个电路在它们的供电时共用同一阻抗,彼此之间将会产生串扰。下例图左边部分说明了核和

I/O 利用同一电源的情况下的核噪声。 这个噪声是由与压降相关的核电流引起的,这里的压降是通过粘

合线和引脚自感引起的,在图 3-3 中,以电阻的形式表示。即使 PCB 的电源电压系统是远离各种纹波电

压,但片内电源也是有躁声的。因为端口缓冲区和内核是同一种内部电源,噪声通过激活的晶体管传递到

每个输出接脚,这不仅影响输出管脚,还影响输入引脚,输入引脚被影响取决于芯片内部的寄生电容(例

如保护电路)。 在对 EME 敏感的情况下,可能需要对每一个引脚滤波,至少对于多引脚的微控制器,这是

基于成本和空间的原因。

共用与隔离电源的串扰

审核编辑 黄昊宇

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

MCU中的IO口输入输出状态详解2022-02-08 1414

-

使用电感降低噪声的注意点:串扰、GND线反弹噪声2023-02-15 2132

-

MCU IO口的作用和特点2024-09-30 4224

全部0条评论

快来发表一下你的评论吧 !