NEC微控制器的片上EMC措施——片上电容

NEC微控制器的片上EMC措施——片上电容

描述

多年来,NEC CMOS 微控制器集成了各种 EMC 技术,虽然片上电容和倍频时钟发生器是有效的,但对PCB 的设计方面却没有任何措施,这里是首次阐述。进一步讲,应用笔记仅着重于 PCB 设计技术,只有少数 NEC EMC 的片上措施在这里列出,但这些都是有效 EMC 措施,并且都应该在选择阶段考虑的。

EME 优化退耦目标是通过一个或更多的去耦电容提供一个最高所需高频电流。高频电流存放在片上的开关电路中环路越多和电容越低对其它供电电路影响较大。为优化连接线路的阻抗,通常电容尽可能接近微控制器的供电引脚。 为减少电流环路辐射,应当减少环路面积。仅用 PCB 设计技术难以实现最大程度的改善。因此,我们的一贯对策是将部分去耦电容放到芯片内部从而减少连接阻抗,并且适当的考虑电流回路面积,这些片上电容太小以至不能提供整个芯片去耦,所以 PCB 上的电容仍是必要的,然而,对于较高的频率范围,它们可以很好地减少辐射。

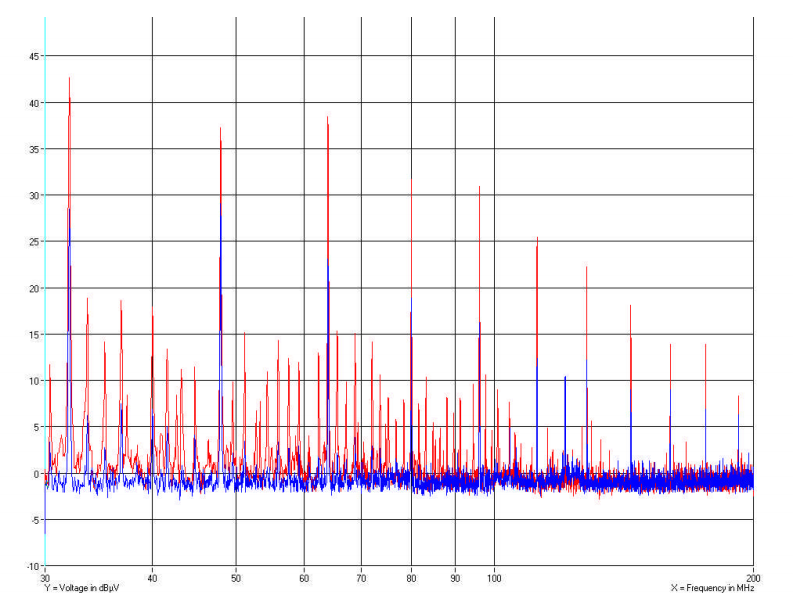

测量结果如图 4-1,对"同一"微控制器有无片上电容的结果作一下对比。红色曲线呈现无电容情况下的辐射效果,而蓝色曲线是带有片上电容情况下的辐射效果,有电容时,在很宽的频率范围内改善了约 15dB,不仅没有增加芯片尺寸,而且也没有增加额外的费用。

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

片上系统微控制器推动便携式医疗设备创新2010-12-21 3050

-

片上系统如何简化风扇控制器设计?2021-05-13 1543

-

HPM6000系列微控制器的片上各类SRAM使用指南2023-06-01 809

-

ADI 新款精密模拟微控制器集成了片上数据转换器,可简化光模2010-02-01 707

-

恩智浦推出首款内嵌易用型片上CANopen驱动微控制器2011-01-19 1244

-

EE-127:ADSP-21065L片上SDRAM控制器2021-04-16 870

-

EE-163:ADSP-21161N SHARC片上SDRAM控制器2021-04-17 870

-

EE-178:ADSP-TS101S TigerSHARC®片上SDRAM控制器2021-05-27 1018

-

基于硬件损耗均衡算法的片上norflash控制器设计2021-07-30 900

-

【微控制器基础】——从历史切入,了解微控制器的五个要素(上)2023-12-07 1535

全部0条评论

快来发表一下你的评论吧 !