时钟树的设计原则

描述

时钟领域及其未来技术发展是半导体行业的热门研发方向之一。

在高性能应用中,例如通信、无线基础设施、服务器、广播视频以及测试和测量装置,当系统集成更多功能并需要提高性能水平时,硬件设计就变得日益复杂,为系统提供参考时序的板级时钟树也走向这种趋势。在进行时钟树设计时,“一成不变”的策略并不适用,优化时钟树以满足性能和成本的要求取决于多种因素,包括系统架构、集成电路(IC)时序需求(频率、信号格式等)和终端应用的抖动需求。

多年来,Skyworks投资于时钟领域的研发创新,研发出集频率灵活与低抖动于一身的专利技术,并基于此向世界提供的广泛的时钟产品组合,包括时钟发生器、时钟缓冲器、抖动清除时钟和XO/VCXO等,及高性能和集成度的定制化时钟树解决方案。在技术研发与产品更新中,我们在时钟树的设计方面不断探索,也积累了相关专业经验,希望与行业专家探讨与分享。

本文将从技术角度解析设计时钟树的设计原则,来帮助大家了解重要的设计步骤、更周全的考虑各种影响因素对于设计带来的影响,以做出更加高效的设计决策。

第一章

参考时序-何时使用晶体或时钟

第一个设计原则是理清硬件设计的参考时钟需求,并选择用于系统中处理器、FPGA、ASIC、PHY、DSP和其它组件的参考时钟类型。如果IC已集成振荡器和片上锁相环(PLL)用于片内时序,那么通常可以使用石英晶体。石英晶体具有成本效益,因其优异的相位噪声特性而被广泛使用,他们放在靠近IC的地方,以简化电路板布局。然而,晶体的缺点之一是在整个温度范围内频率有显著变化,超出许多串行器/解串器(SerDes)应用中高精度ppm等级的稳定性需求。在许多要求高稳定性的高速SerDes应用中,推荐使用晶体振荡器(XO),因其可以确保比无源晶体更可靠的稳定性。

当需要多个参考频率时,通常使用时钟发生器和时钟缓冲器。在某些应用中,FPGA/ASIC有多个时钟域用于数据通路、控制平面和存储控制器接口,需要多个特定参考频率。如果IC不提供晶体输入接口,或者当IC需要与外部参考(同步源应用)同步时,又或者当所需高频参考值很难由晶体生成时,时钟发生器和缓冲器也是优先选择。

第二章

自由运行对比同步时钟树

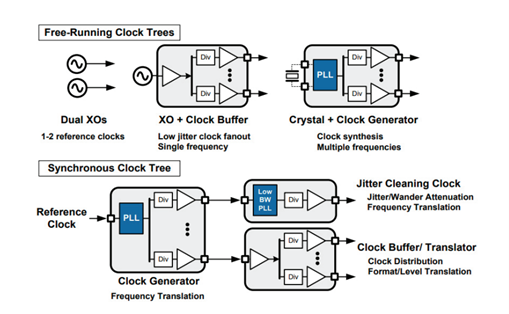

一旦硬件设计确定下来,并且为部分器件选择了晶体,接下来的步骤就是为剩下的时钟选择时序架构:自由运行或同步。对于需要一个或多个独立参考时钟,且没有任何特殊锁相环或同步需求的应用来说,XO、时钟发生器和时钟缓冲器是理想选择。处理器、存储控制器、SoC 和外围组件(例如,USB和PCI Express转换器)通常使用 XO、时钟发生器和时钟缓冲器组合,为自由运行和异步的应用提供参考时序。如果应用需要一到两个定时源,XO 是最好的选择;而时钟发生器和缓冲器更适合同时需要多个独立时钟的应用。时钟发生器能够合成多个不同频率的时钟,但与由时钟缓冲器加上XO组成的时钟树相比,牺牲部分抖动性能。时钟缓冲器可以与XO联合分配多个相同频率的时钟,并且为多输出时钟树实现最低抖动。

同步时钟用于需要连续通信和网络级同步的应用,例如光传输网络(OTN)、SONET/SDH、移动回程、同步以太网和 HD SDI 视频传输。以上应用需要发射器和接收器在相同频率操作。同步所有的SerDes参考时钟到一个高精度网络参考时钟(例如,Stratum 3或GPS),保证所有节点同步。在这些应用中,基于低带宽PLL 时钟提供漂移和抖动滤波(抖动清除),以确保网络级同步。在网络线路卡PLL应用中,带有压控振荡器(VCO)的专用抖动衰减时钟或分立PLL是SerDes定时首选的时钟解决方案。为了获得最佳性能,抖动衰减时钟应放置在时钟树末端,直接驱动SerDes器件,时钟发生器和缓冲器可为其他系统提供参考。

<时钟树示例>

第三章

时钟抖动

时钟抖动是时序器件的一个关键指标,因为过多的时钟抖动会影响系统性能。有三种常见的时钟抖动类型,并且在不同的应用中,某种抖动类型可能比另外两种更重要。

相邻周期间抖动是指任意两个相邻时钟周期之间,时钟周期的最大差异,通常测量1000个时钟周期以上。

周期抖动是指在大量周期(通常为10000个时钟周期)中,实际周期与理想周期的最大偏差。相邻周期间抖动和周期抖动在计算数字系统的建立和保持定时余量时有一定作用,而且是CPU和SoC器件常见的性能系数。

相位抖动是高速SerDes应用的性能参数。它是噪声功率对信号总功率的比值,是通过对时钟信号单边带相位噪声所在的偏离载波信号的频带范围进行积分计算而得。相位抖动在FPGA和高速SerDes定时应用中非常关键,过度的相位抖动会增加高速串行接口的位错误率。

在时钟树设计和器件选择期间,基于最大抖动性能来评估器件非常重要。一般的抖动规格并不能确保在所有情况下(包括工艺、电压、温度和频率变化)皆能符合性能。除了额外因素,最大抖动还包括更全面的规格。

此外,要特别注意确认时序器件数据手册上的抖动测试条件。时钟抖动性能在很多情况下都会变化,包括器件配置、工作频率、信号格式、输入时钟转换速率、供电电源和电源噪声。要尽可能寻求完全符合指定抖动测试条件的器件,才能确保在更广的操作范围内工作。

第四章

时钟和振荡器器件选择标准

一旦基本的时钟树架构确定,下一个步骤是选择器件。表1汇总了在自由运行和同步时钟树设计中时钟和振荡器器件的选择标准。为了降低物料清单(BOM)成本和设计复杂度,要寻求简化时钟树设计的特性。

<时钟器件选择标准>

第五章

消除时钟树抖动

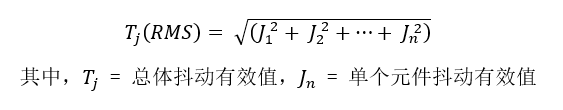

时钟树设计完成之前,要评估总的时钟树抖动,以保证有足够的系统级设计余量。需要特别注意的是,总的时钟树抖动有效值远低于数据手册中多个组件规格的简单相加。时钟树的抖动定义如下图。

器件抖动可通过数据手册中的抖动规格进行估算,或从相位噪声数据中计算。Skyworks提供简便的工具,把时钟相位噪声转换成抖动。详细信息,请浏览网站:https://tools.skyworksinc.com/jittercalculator/phase-noise-jitter-calculator.aspx。请注意用最大抖动规格来生成总时钟树抖动的保守估计值。

注意:如果抖动分布是高斯类型和非相干的,这个方程可应用于计算总的周期抖动和相位抖动;方程不适用于相邻周期间抖动,那表示是抖动峰值,而不是有效值。

第六章

简化时钟树设计

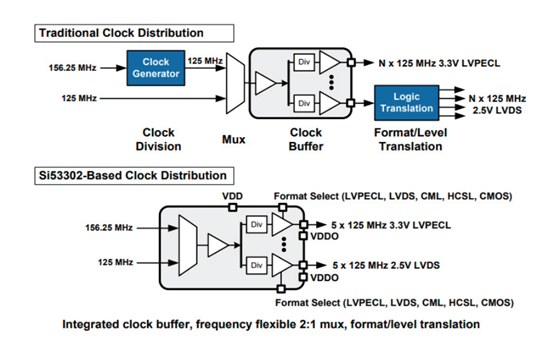

除了基本的时钟生成和分配之外,许多时钟还要具备特殊功能。例如,格式/电平转换(例如3.3V LVPECL到2.5V LVDS)、不同频率的时钟切换、时钟分频、引脚选择的输出启动控制和为降低电磁干扰(EMI)的CMOS驱动强度(输出阻抗)控制。如果采用离散方式设计,实现这些功能将为时钟树设计增加大量成本和复杂性。Skyworks推出的Si5330x通用缓冲器/转换器系列产品,集成格式/电平转换、时钟多路复用、时钟分频和其它关键的时钟树功能块。上述器件可以用单个时钟缓冲器IC取代多个LVPECL、LVDS、CML、HCSL和LVCMOS缓冲器。除了简化时钟树设计(见图2),Si5330x芯片最大限度地降低BOM成本和设计复杂度,简化采购过程,并提高系统性能。

一直以来,Skyworks投资于研发,在时钟领域获得多项技术专利,并为行业提供广泛的时钟产品组合以及低功耗、小尺寸、模拟密集型混合信号的定制化解决方案。未来,Skyworks将继续坚持创新,继续致力于推动时钟领域的技术进步及产品研发。

审核编辑:汤梓红

-

时钟树是什么?介绍两种时钟树结构2023-12-06 3717

-

数字IC设计中的分段时钟树综合2023-12-04 4371

-

时钟树设计师的 5 个问题2023-01-04 1859

-

评价时钟树质量的方法2022-09-05 2951

-

STM32时钟树2021-12-06 1293

-

STM32F10X-时钟树详细介绍2021-12-01 883

-

STM32F429--RCC时钟树2021-11-29 875

-

为什么要了解时钟树2021-08-12 1247

-

时钟树的使用方法简介2020-03-08 9590

-

STM32时钟系统时钟树和时钟配置函数介绍及系统时钟设置步骤资料2018-10-11 1465

-

基于STM32Cube的时钟树配置2017-11-28 1511

-

时钟网格与时钟树设计方法对比研究2012-05-07 2338

-

时钟树优化与有用时钟延迟2011-10-26 5067

全部0条评论

快来发表一下你的评论吧 !