OKIMX6Q开发板的片外内存地址和片外存储器

存储技术

描述

1、片外内存地址

IMX6Q中MMDC-DDR控制器的地址空间为:0x1000_0000~0xFFFF_FFFF共3840MB,即MMDC-DDR控制器允许配置的最大片外内存为3.75GB。

OKIMX6Q开发板采用4片镁光公司的MT41K128M16JT型DDR3内存组成1GB的内存。该内存采用16Meg×16×8banks的内存结构。其地址线为:A0~A13,块地址线为:BA0~BA2,片选线为:CS0,4颗内存组成64位数据总线,占用MMDC-DDR控制器1GB地址空间:0x1000_0000~0x4FFF_FFFF。MMDC-DDR控制器剩余2.75GB地址空间为:0x5000_0000~0xFFFF_FFFF。

在u-boot2009-08代码./board/freescale/mx6qsabresd/config.mk文件中定义u-boot代码载入内存的基址为:0x2780_0000。

2、片外存储器

OKIMX6Q开发板采用1片SanDisk公司的SDIN8DE2-8G-Q型EMMC H200 4.5.1接口的iNAND Ultra 存储器。该存储器容量为8GB。

注:eMMC (Embedded Multi Media Card) 为MMC协会所订立的、主要是针对手机或平板电脑等产品的内嵌式存储器标准规格。eMMC的一个明显优势是在封装中集成了一个控制器,它提供标准接口并管理闪存,使得手机厂商就能专注于产品开发的其它部分,并缩短向市场推出产品的时间。这些特点对于希望通过缩小光刻尺寸和降低成本的NAND供应商来说,同样的重要。eMMC = NAND flash + 控制器 + 标准封装接口。

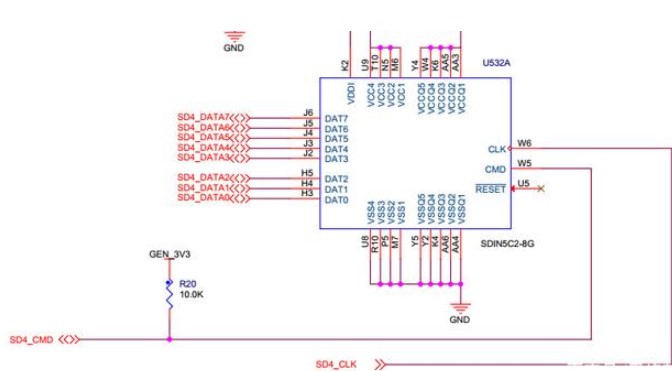

通过图1和IMX6DQRM文件5595和5596页表67-3可知:EMMC接口采用IMX6Q片内USHDC4外部信号接口。其包括:

(1)数据总线:SD4_DATA0~SD4_DATA7,共8位并行接口。

(2)时钟线:SD4_CLK。

(3)命令线:SD4_CMD。

图1

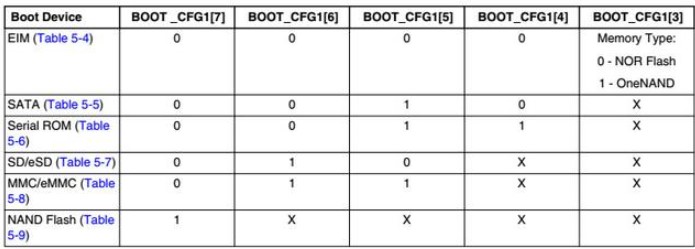

EMMC的eFuse启动配置根据图2所示进行设计。上电是从MMC/eMMC存储器启动时,要求BOOT_CFG1[7]-BOOT_CFG1[6]-BOOT_CFG1[5]=0-1-1。

图2

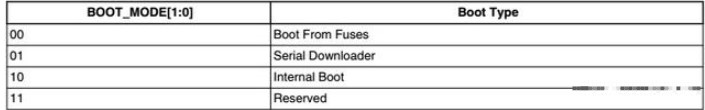

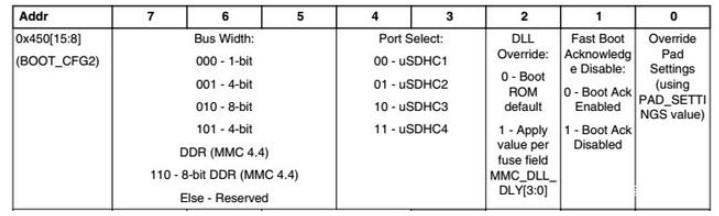

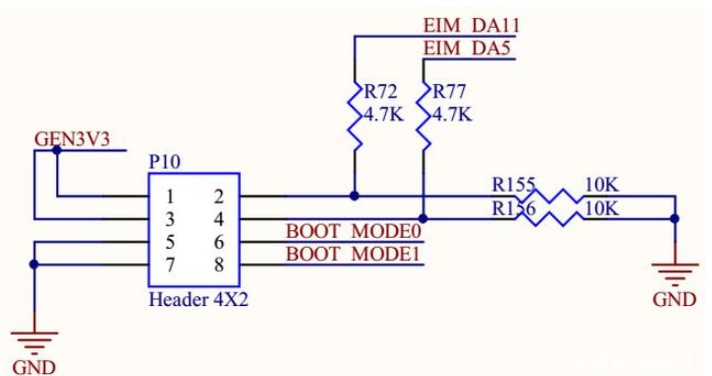

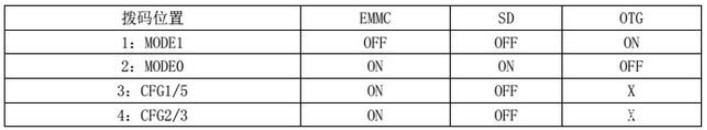

图3、图4和图5是启动模式配置表和设置电路。OKMX6X-C底板支持:OTG、EMMC和SD卡3种上电启动模式。图5中的EIM_DA5接IMX6Q的BOOT_CFG1[5],EIM_DA11接IMX6Q的BOOT_CFG2[3],其对应拨码开关OFF代表对应位为0,ON代表为1。BOOT_MODE0和BOOT_MODE1对应拨码开关OFF代表1,ON代表0。核心板配置BOOT_CFG1[7:6]=0b01。

图3

图4

图5

图6

图7

通过以上分析可知:

(1)设置eMMC启动:MODE[1:0]=0b10,代表从片内启动。BOOT_CFG1[5]=0b1,即:BOOT_CFG1[7:5]=0b011,代表从MMC/eMMC启动。BOOT_CFG2[3]=0b1,核心板设置BOOT_CFG2[4]=0b1,则BOOT_CFG2[4:3]=0b11,代表eMMC接口为USDHC4,和图2.2-1相符。

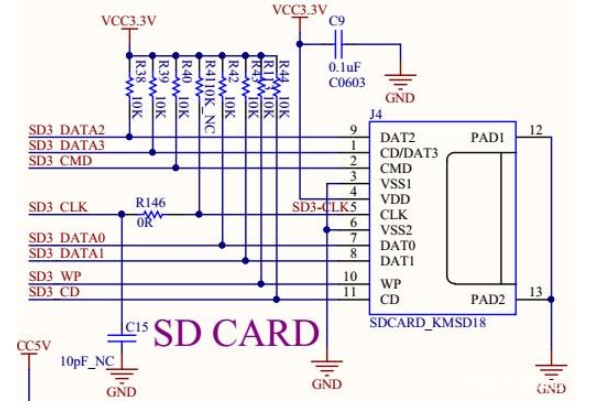

(2)设置SD卡启动:MODE[1:0]=0b10,代表从片内启动。BOOT_CFG1[5]=0b0,即:BOOT_CFG1[7:5]=0b010,代表从SD卡启动。BOOT_CFG2[3]=0b0,核心板设置BOOT_CFG2[4]=0b1,则BOOT_CFG2[4:3]=0b10,代表SD接口为USDHC3,和图2.2-7相符。

(3)设置OTG启动:MODE[1:0]=0b01,代表从OTG接口启动。拨码开关其他配置无效。

-

ARM片外FIash存储器IAP解决方案2011-11-30 2469

-

51单片机片内外存储器统一编址是什么意思?2011-10-08 6104

-

为什么4KB的存储器高位地址线需要4根?2018-12-18 9033

-

关于外存储器的简单介绍2019-06-05 2441

-

MCS-51的存储器分类2021-12-07 1857

-

怎么解决51单片机内存不足加片外存储后程序烧录的问题呢?2023-03-20 1587

-

求助,内存地址空间是否一定大于所有物理存储器的容量?2023-10-17 548

-

详解单片机片外程序存储器操作命令2017-10-17 2526

-

单片机的片内存储器跟片外存储器的内和外是相对于什么啊?2017-11-23 18772

-

外存储器有哪些2018-11-24 65363

-

单片机的片内存储器和片外存储器到底有什么区别2019-08-15 11410

-

内存储器和外存储器的分类与区别2019-05-26 43369

-

MCS-51的存储器结构——单片机原理学习笔记(三)2021-11-24 1254

-

内存储器与外存储器的主要区别2024-05-22 10287

全部0条评论

快来发表一下你的评论吧 !