讨论讨论PCB中的去耦设计

PCB设计

描述

本节主要讨论PCB中的去耦设计,主要包括以下三部分内容

1.去耦的两种解释

2.去耦电容的选择方法

3.耦电容的安装方式与PCB设计

去耦(Decoupling):当器件高速开关时,高速器件需要从电源分配网络吸收瞬态能量。去耦电容也为器件和元件提供一个局部的直流源,这对减小由于电流在板上传播而产生的尖峰很有用。去耦电容通过在信号线和电源平面间提供一个低阻抗的电源来实现,在频率升高到自谐振点之前,随着频率升高,去耦电容的阻抗会越来越低。

这样,高频噪声会有效地从信号线上泄放,这时余下的低频能量的影响就比较小了。

1.去耦的两种解释:

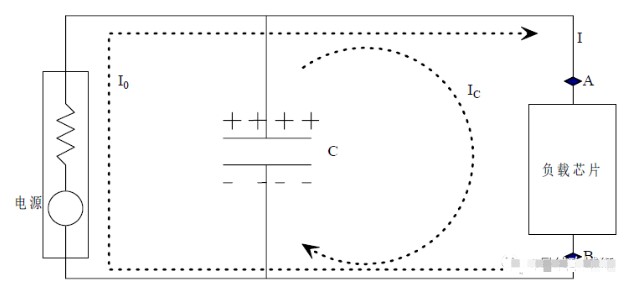

a.从储能的角度来说明电容退耦原理:在制作电路板时,通常会在负载芯片周围放置很多电容,这些电容就起到电源退耦作用。其原理可用图 1 说明。

图 1 去耦电路

当负载电流不变时,其电流由稳压电源部分提供,即图中的 I0,方向如图所示。此时电容两端电压与负载两端电压一致,电流 Ic 为 0,电容两端存储相当数量的电荷,其电荷数量和电容量有关。当负载瞬态电流发生变化时,由于负载芯片内部晶体管电平转换速度极快,必须在极短的时间内为负载芯片提供足够的电流。但是稳压电源无法很快响应负载电流的变化,因此,电流 I0 不会马上满足负载瞬态电流要求,因此负载芯片电压会降低。但是由于电容电压与负载电压相同,因此电容两端存在电压变化。对于电容来说电压变化必然产生电流,此时电容对负载放电,电流 Ic 不再为 0,为负载芯片提供电流。根据电容等式:

I=C*dV/dt 公式 1

只要电容量 C 足够大,只需很小的电压变化,电容就可以提供足够大的电流,满足负载瞬态电流的要求。这样就保证了负载芯片电压的变化在容许的范围内。这里,相当于电容预先存储了一部分电能,在负载需要的时候释放出来,即电容是储能元件。储能电容的存在使负载消耗的能量得到快速补充,因此保证了负载两端电压不至于有太大变化,此时电容担负的是局部电源的角色。

从储能的角度来理解电源退耦,非常直观易懂,但是对电路设计帮助不大。从阻抗的角度理解电容退耦,能让我们设计电路时有章可循。实际上,在决定电源分配系统的去耦电容量的时候,用的就是阻抗的概念。

b.从阻抗的角度来理解退耦原理

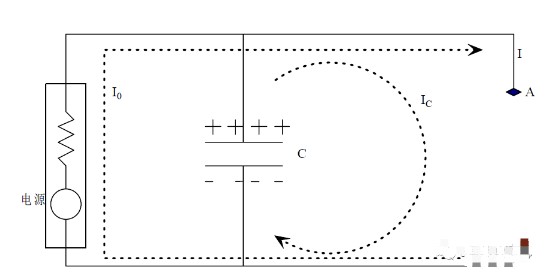

将图 1 中的负载芯片拿掉,如图 2 所示。从 AB 两点向左看过去,稳压电源以及电容退耦系统一起,可以看成一个复合的电源系统。这个电源系统的特点是:不论 AB 两点间负载瞬态电流如何变化,都能保证 AB 两点间的电压保持稳定,即 AB 两点间电压变化很小。

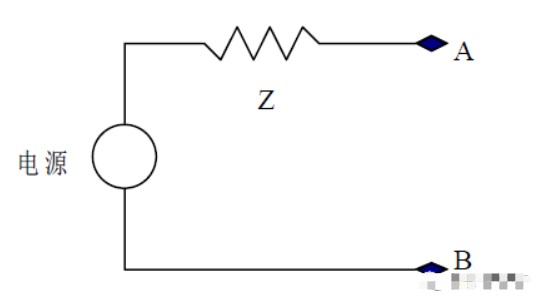

图2电源部分我们可以用一个等效电源模型表示上面这个复合的电源系统,如图 3

图 3 等效电路对于这个电路可写出如下等式:∆

V=Z*∆I 公式 2

我们的最终设计目标是,不论 AB 两点间负载瞬态电流如何变化,都要保持 AB 两点间电压变化范围很小,根据公式 2,这个要求等效于电源系统的阻抗 Z 要足够低。在图 2 中,我们是通过去耦电容来达到这一要求的,因此从等效的角度出发,可以说去耦电容降低了电源系统的阻抗。另一方面,从电路原理的角度来说,可得到同样结论。电容对于交流信号呈现低阻抗特性,因此加入电容,实际上也确实降低了电源系统的交流阻抗。

从阻抗的角度理解电容退耦,可以给我们设计电源分配系统带来极大的方便。实际上,电源分配系统设计的最根本的原则就是使阻抗最小。最有效的设计方法就是在这个原则指导下产生的。

2.方法一:利用电源驱动的负载计算电容量

设负载(容性)为 30pF,要在 2ns 内从 0V 驱动到 3.3V,瞬态电流为:I=C*dV/dt=30pF*3.3V/2.2ns=49.5mA如果共有 36 个这样的负载需要驱动,则瞬态电流为:36*49.5mA=1.782A。假设容许电压波动为:3.3*2.5%=82.5 mV,所需电容量为

C=I*dt/dv=1.782A*2ns/0.0825V=43.2nF

说明:所加的电容实际上作为抑制电压波纹的储能元件,该电容必须在 2ns 内为负载提供1.782A 的电流,同时电压下降不能超过 82.5 mV,因此电容值应根据 82.5 mV 来计算。记住:电容放电给负载提供电流,其本身电压也会下降,但是电压下降的量不能超过 82.5 mV(容许的电压波纹)。这种计算没什么实际意义,之所以放在这里说一下,是为了让大家对去耦原理认识更深。

方法二:利用目标阻抗计算电容量(设计思想很严谨,要吃透)

为了清楚的说明电容量的计算方法,我们用一个例子。要去耦的电源为 1.2V,容许电压波动为 2.5%,最大瞬态电流 600mA,

第一步:计算目标阻抗XMAX=VDD*Ripple/∆IMAX=1.2 0.025/0.6=50mΩ

第二步:确定稳压电源频率响应范围。和具体使用的电源片子有关,通常在 DC 到几百 kHz 之间。这里设为 DC 到 100kHz。在 100kHz 以下时,电源芯片能很好的对瞬态电流做出反应,高于 100kHz 时,表现为很高的阻抗,如果没有外加电容,电源波动将超过允许的 2.5%。为了在高于 100kHz 时仍满足电压波动小于 2.5%要求,应该加多大的电容?

第三步:计算电容量

当频率处于电容自谐振点以下时,电容的阻抗可近似表示为:

ZC=1/2*π*f*c

频率 f 越高,阻抗越小,频率越低,阻抗越大。在感兴趣的频率范围内,电容的最大阻抗不能超过目标阻抗,因此使用 100kHz 计算(电容起作用的频率范围的最低频率,对应电容最高阻抗)。

C=1/2*π*f*XMAX=31.831uF

第四步:计算 bulk 电容的最高有效频率

当频率处于电容自谐振点以上时,电容的阻抗可近似表示为:ZC=2*π*f*ESL频率 f 越高,阻抗越大,但阻抗不能超过目标阻抗。假设 ESL 为 5nH,则最高有效频率为:fmax=XMAX/2*π*ESL=1.6MHz。这样一个大的电容能够让我们把电源阻抗在 100kHz 到1.6MHz 之间控制在目标阻抗之下。当频率高于 1.6MHz 时,还需要额外的电容来控制电源系统阻抗。第五步:计算频率高于 1.6MHz 时所需电容

如果希望电源系统在 500MHz 以下时都能满足电压波动要求,就必须控制电容的寄生电感量。必须满足2*π*f*LMAX×≤XMAX ,所以有:

LMAX≤XMAX/(2*π*500MHz)=0.016nH

假设使用 AVX 公司的 0402 封装陶瓷电容,寄生电感约为 0.4nH,加上安装到电路板上后过孔的寄生电感(本文后面有计算方法)假设为 0.6nH,则总的寄生电感为 1 nH。为了满足总电感不大于 0.16 nH 的要求,我们需要并联的电容个数为:1/0.016=62.5 个,因此需要63 个 0402 电容。

为了在 1.6MHz 时阻抗小于目标阻抗,需要电容量为:C=1/(2*π*1.6MHz*XMAX)=1.9894uF

因此每个电容的电容量为 1.9894/63=0.0316 uF。

综上所述,对于这个系统,我们选择 1 个31.831 uF 的大电容和 63 个 0.0316 uF 的小电容即可满足要求。

注意:以上基于目标阻抗的计算,只是为了说明这种方法的基本原理,实际中不能这样简单的计算就了事,因为还有很多问题需要考虑。学习的重点是这种方法的核心思想。

3.去耦电容的安装方式与PCB设计

安装去耦电容时,一般都知道使电容的引线尽可能短。但是,实践中往往受到安装条件的限制,电容的引线不可能取得很短。况且,电容自身的寄生电感只是影响自谐振频率的因素之一,自谐振频率还与过孔的寄生电感、相关印制板导线的寄生电感等因素有关。一味地追求引线短,不仅困难,而且可能根本达不到目的。当去耦电容在PCB上的位置不可能实现使用很短的印制导线时,就必须加粗印制线。实践证明,一根长宽比小于3的印制线具有非常低的阻抗,能满足去耦电容引线的要求。当然,还需要尽量减少过孔的数量,设计过孔的时候应尽可能减小过孔的寄生电感。

审核编辑:刘清

-

详解去耦电容:去耦电容的PCB布局布线2024-03-27 7772

-

分享PCB中的去耦电容设计2024-01-10 1057

-

PCB去耦电容怎么放置?怎么选择去耦电容?2023-11-29 2588

-

去耦电容PCB设计和布局详解2023-07-05 2425

-

什么是PCB中的板级去耦2022-02-10 2009

-

PCB的板级去耦设计方法2021-03-14 1431

-

PCB的板级去耦设计方法和实例讲解2021-02-19 1393

-

什么是PCB中的板级去耦?2021-01-25 2595

-

浅谈PCB中的去耦电容设计2021-01-07 3565

-

PCB布线技巧之去耦电容的摆放2016-10-26 1434

-

讨论PCB板设计2012-09-29 1592

-

去耦电容在PCB板设计中的应用2009-12-09 44834

-

PCB设计中的过孔问题讨论2009-11-11 1590

-

高速PCB电源去耦设计指南2007-10-16 977

全部0条评论

快来发表一下你的评论吧 !