Vivado DDR4仿真操作

描述

首先新建ddr的IP,具体每个参数的含义,可以参考之前写的

Virtex7 Microblaze下DDR3测试

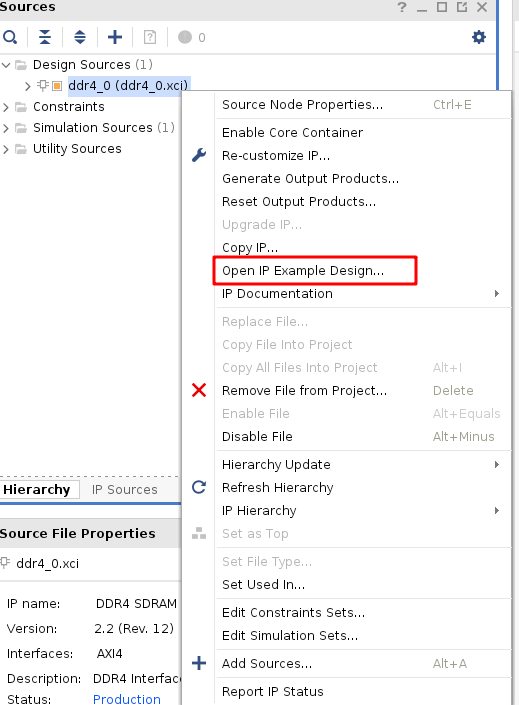

再右键,打开IP的Example Design,这样才能生成ddr对应的model。

image-20220730160832768

image-20220730160832768

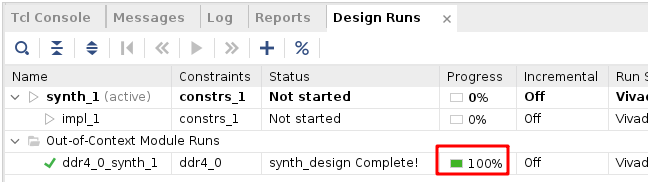

如果右键发现这个按钮是不可用的,那就多等等,IP建好后需要等synth_design Complete后,很多文件才生成完毕。

image-20220730160950335

image-20220730160950335

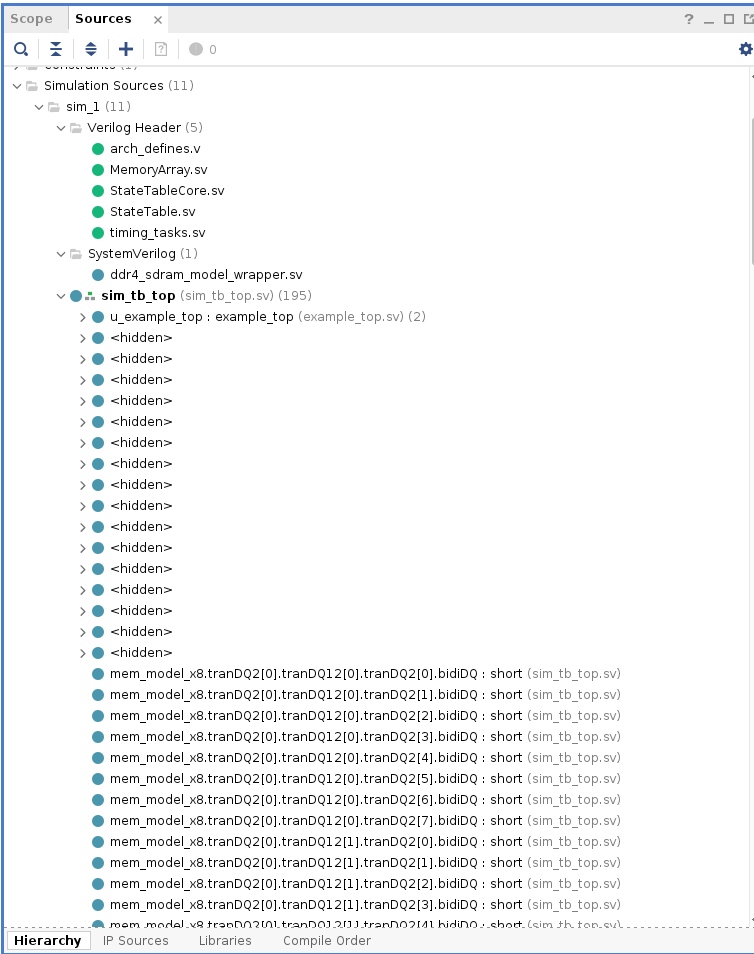

在sim目录下,可以看到很多的hidden的文件,这是因为生成的Model被加密了,我们只能使用,但看不到源码

image-20220730163207785

image-20220730163207785

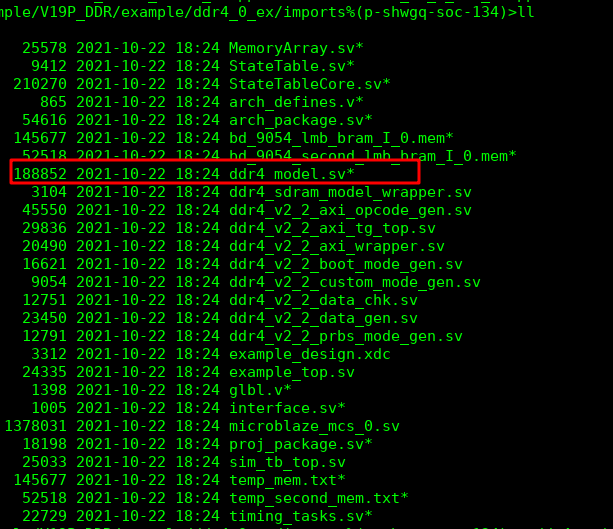

我们可以看下工程下面有个ddr4_model.sv的文件。

image-20220730214033783

image-20220730214033783

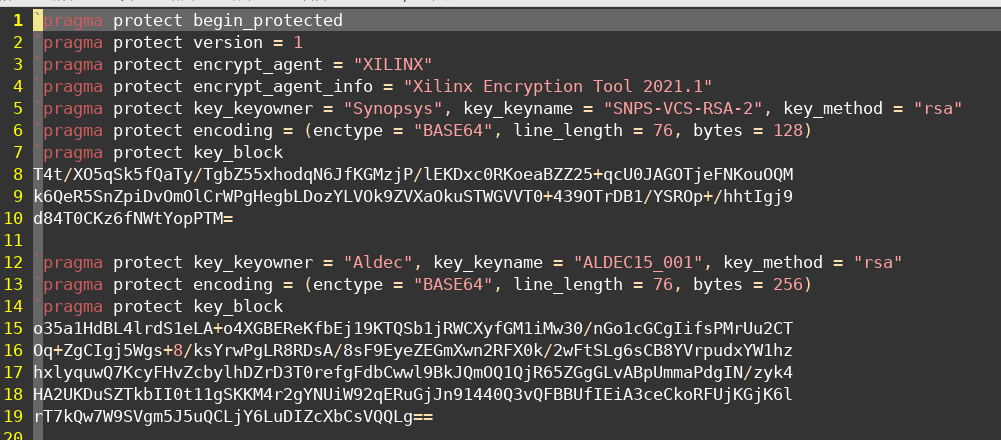

该文件是加密的:

image-20220730214120586

image-20220730214120586

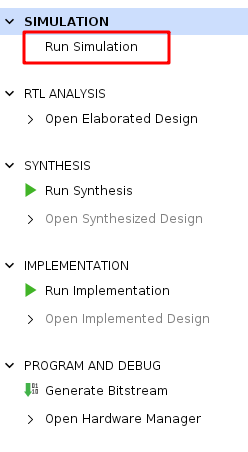

我们直接进行仿真即可:

image-20220730214321561

image-20220730214321561

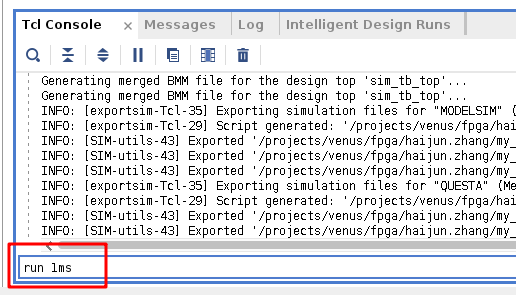

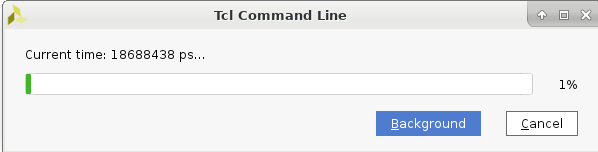

进入到仿真页面,直接通过tcl仿真1ms,但其实仿真不到1ms就会结束:

image-20220730162028789

image-20220730162028789  image-20220730161928489

image-20220730161928489

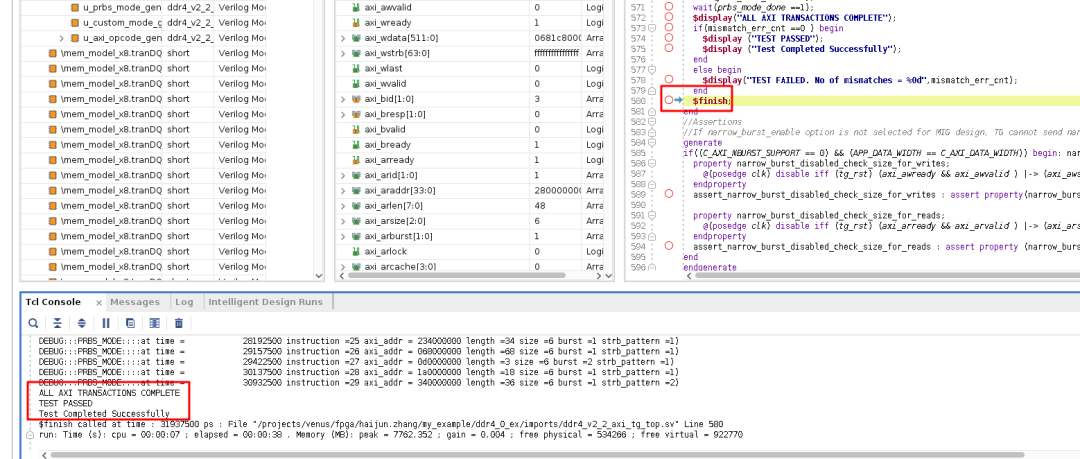

在仿真结束时,会提示下面的信息:

image-20220730161957651

image-20220730161957651

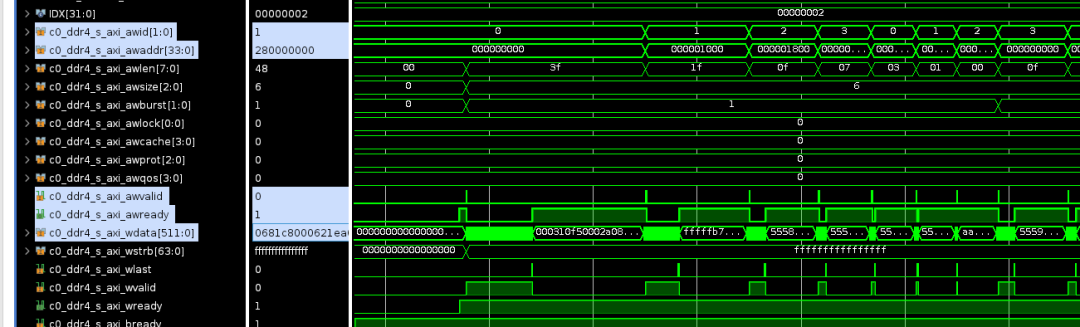

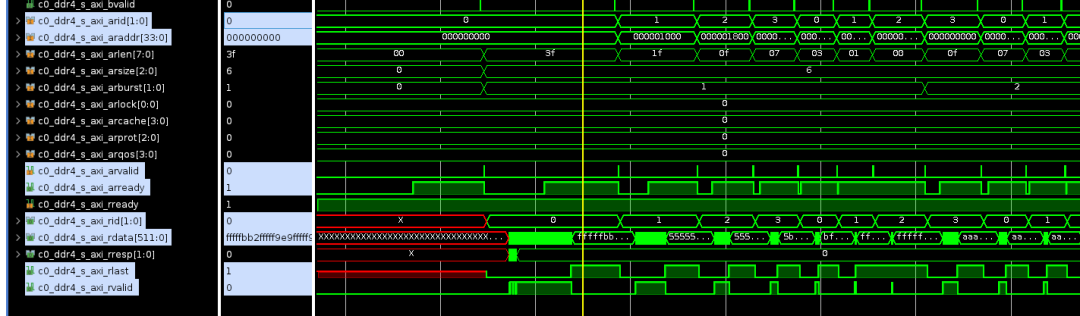

我们可以把ddr ip的AXI总线拉出来,看一下axi写操作和读操作的数据。

image-20220730162217675

image-20220730162217675  image-20220730162250341

image-20220730162250341

审核编辑:彭静

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

什么是DDR4内存的工作频率2024-09-04 7973

-

DDR4的单、双DIE兼容,不做仿真行不行?2024-08-05 1618

-

DDR4和DDR3内存都有哪些区别?2023-10-30 14904

-

DDR4与DDR3的不同之处 DDR4设计与仿真案例2023-09-19 6641

-

高速设计:用于DDR3/DDR4的xSignalAltium 2023-06-25

-

教大家对DDR4做仿真小凡 2022-09-13

-

佛山回收DDR4 高价回收DDR42021-07-15 942

-

VIVADO 2016.1怎样才能实现DDR4内存?2020-04-26 3370

-

DDR4设计规则及DDR4的PCB布线指南2019-07-26 52598

-

DDR4技术有什么特点?如何采用ANSYS进行DDR4仿真?2018-10-14 28354

-

ddr4和ddr3内存的区别,可以通用吗2017-11-08 32657

-

ddr3及ddr4的差异对比2017-11-07 56514

-

DDR4,什么是DDR42010-03-24 4255

全部0条评论

快来发表一下你的评论吧 !