在线学习SystemVerilog-Problem 7-9

描述

HDLBits 是一组小型电路设计习题集,使用 Verilog/SystemVerilog 硬件描述语言 (HDL) 练习数字硬件设计~

网址如下:

https://hdlbits.01xz.net/

关于HDLBits的Verilog实现可以查看下面专栏:

https://www.zhihu.com/column/c_1131528588117385216

缩略词索引:

- SV:SystemVerilog

Problem 7-Xnorgate

题目说明

创建一个 XNOR 门的模块。

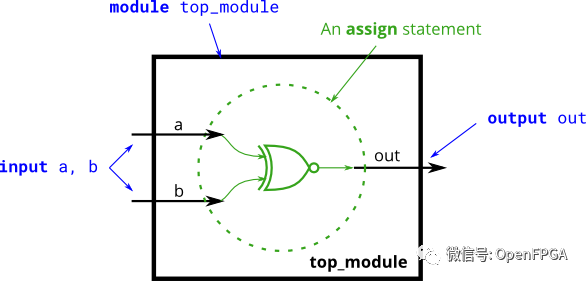

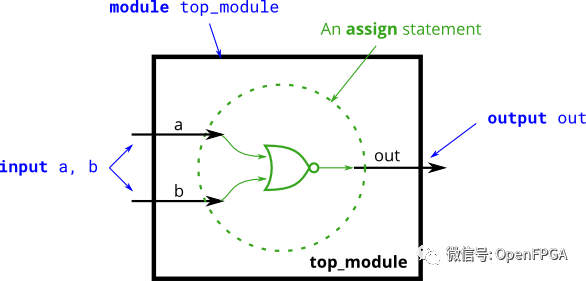

这个题目的核心就是上面的图片,模块和端口已经被定义好了,黑色的框图以及箭头代表模块和端口。我们需要做的工作是完成图中绿色的部分,即完成一个XNOR 门。

模块端口声明

module top_module(

input a,

input b,

output out );

题目解析

这个题目重点还是看懂题目的图片,还是复习一下:

题目中的绿色部分就是上图的同或门,主要由

这里也可以利用数电逻辑来写代码,同或门的逻辑就是同或门 (XNor Gate) 是异或门 (Nor Gate) 的取反输出。异或门的输入输出可以概括为:(输入)相同(输出)为 0 ,不同为 1

module top_module(

input logic a,

input logic b,

output logic out );

assign out = ~( a ^ b) ;

endmodule

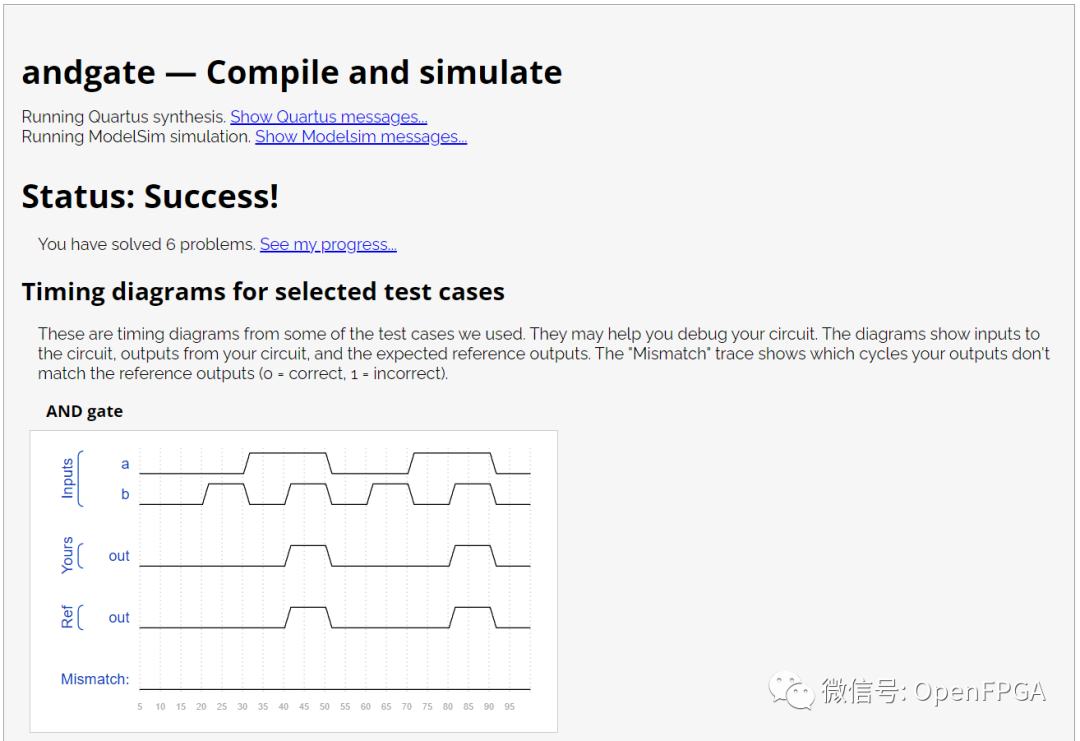

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红(后面会展示)。

这一题就结束了。

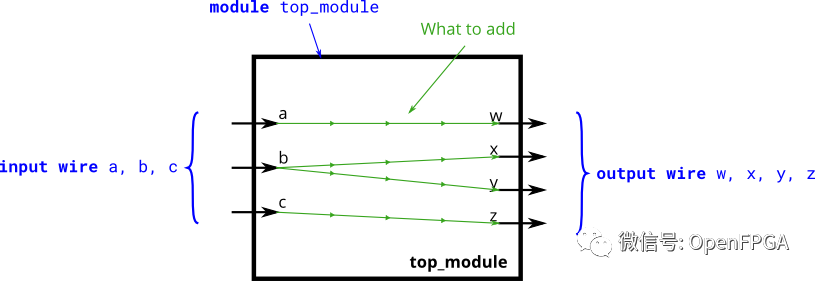

Problem 3-Wire4

题目说明

创建一个具有 3 个输入和 4 个输出的模块,其行为类似于下面演示的这些连线:

a -> w

b -> x

b -> y

c -> z

这个题目的核心就是上面的图片,模块和端口已经被定义好了,黑色的框图以及箭头代表模块和端口。我们需要做的工作是完成图中绿色的部分,即完成这条连线。

模块端口声明

module top_module(

input a,b,c,

output w,x,y,z );

题目解析

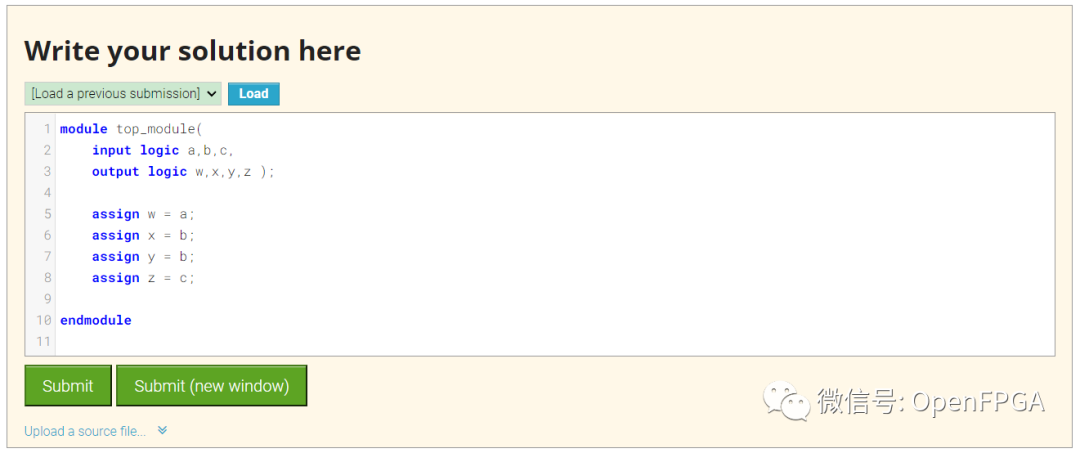

主要使用assign语句实现上面的连线,难度较低。

module top_module(

input logic a,b,c,

output logic w,x,y,z

);

assign w = a;

assign x = b;

assign y = b;

assign z = c;

endmodule

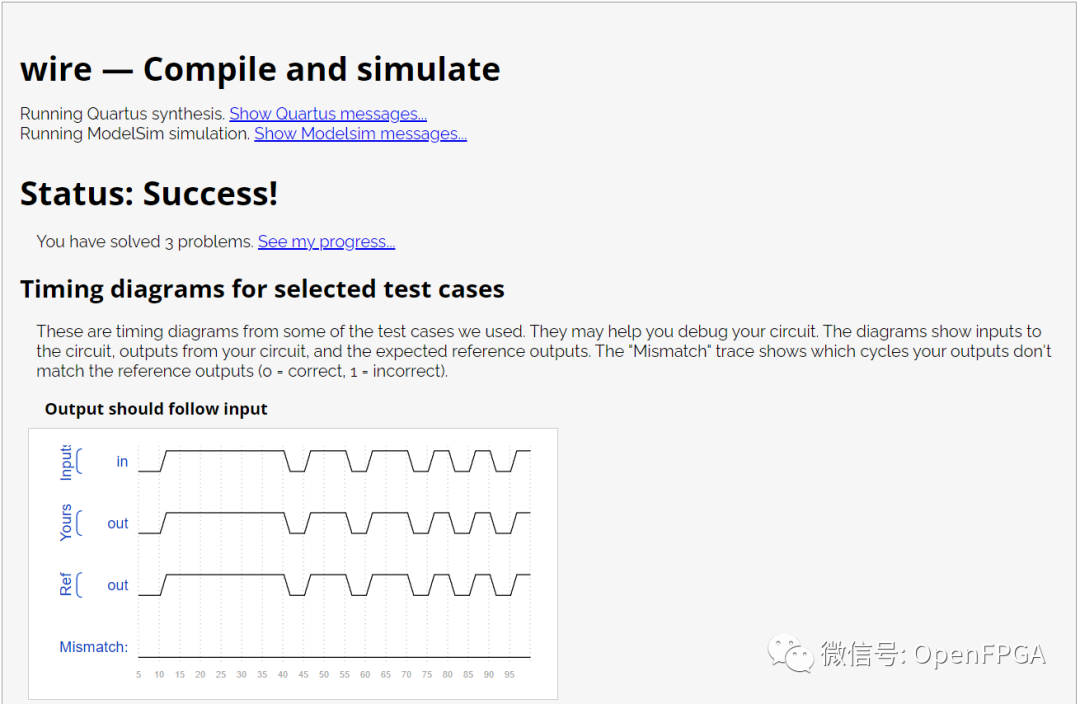

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红(后面会展示)。

这一题就结束了。

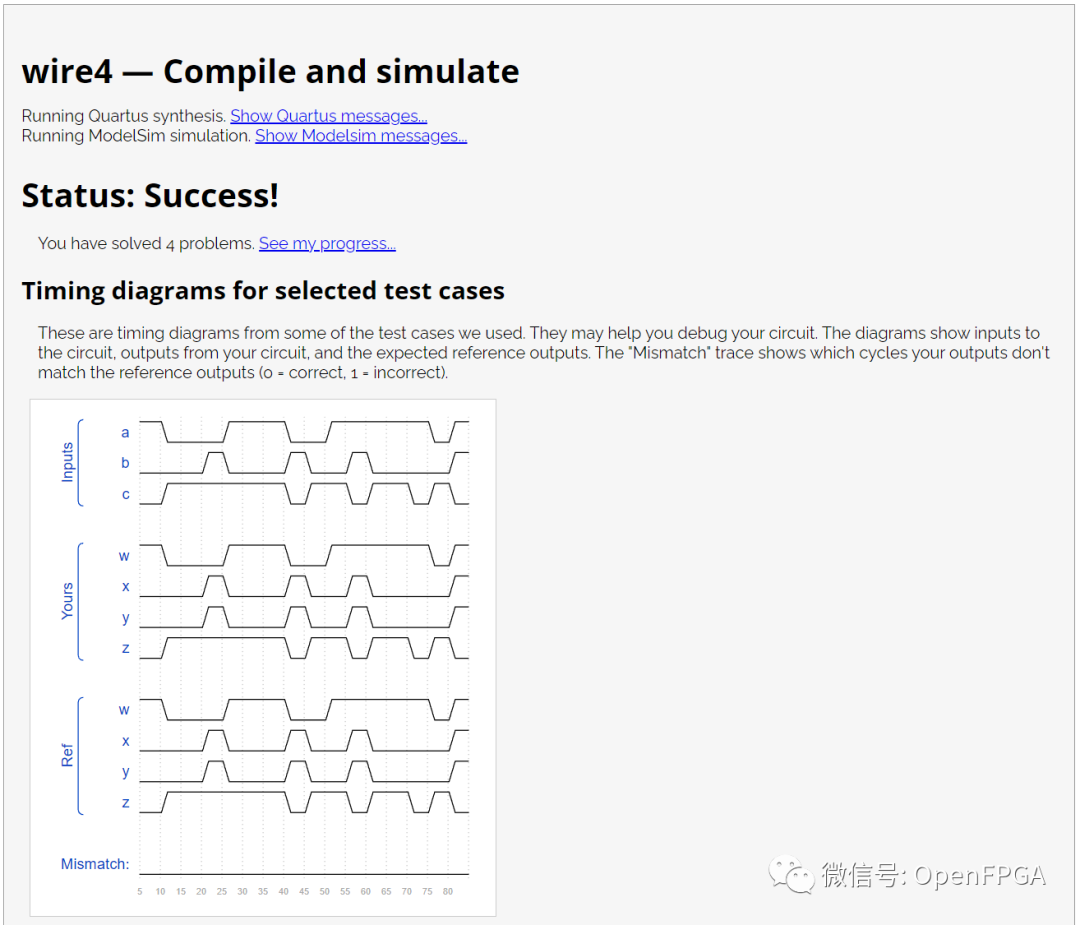

Problem 4-Notgate

题目说明

创建一个实现非门(Notgate)的模块。

从这个题目开始实现几个经典组合电路,非门的的核心就是上面的图片,模块和端口已经被定义好了,黑色的框图以及箭头代表模块和端口。我们需要做的工作是完成图中绿色的部分,实现一个非门。

模块端口声明

module top_module( input in, output out );

题目解析

主要使用assign语句实现非门,也很简单就一个语句“assign out = ~in;”。这里注意一个逻辑取反和逐位取反的区别。

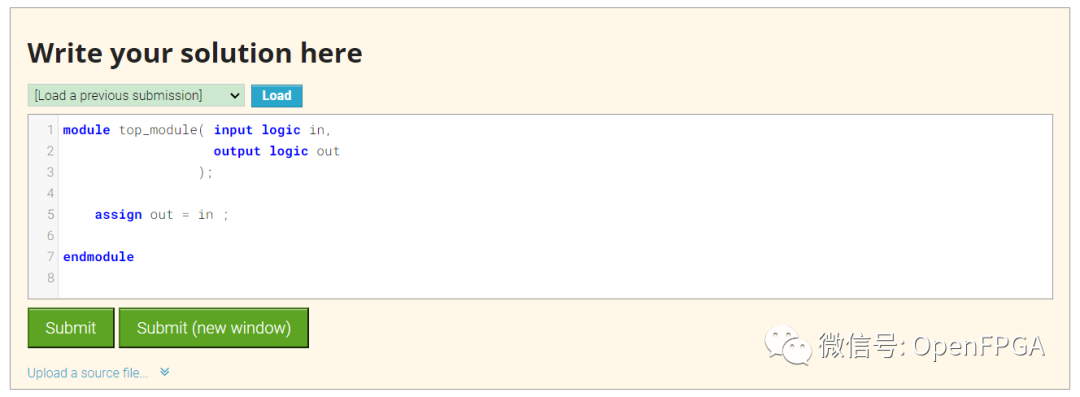

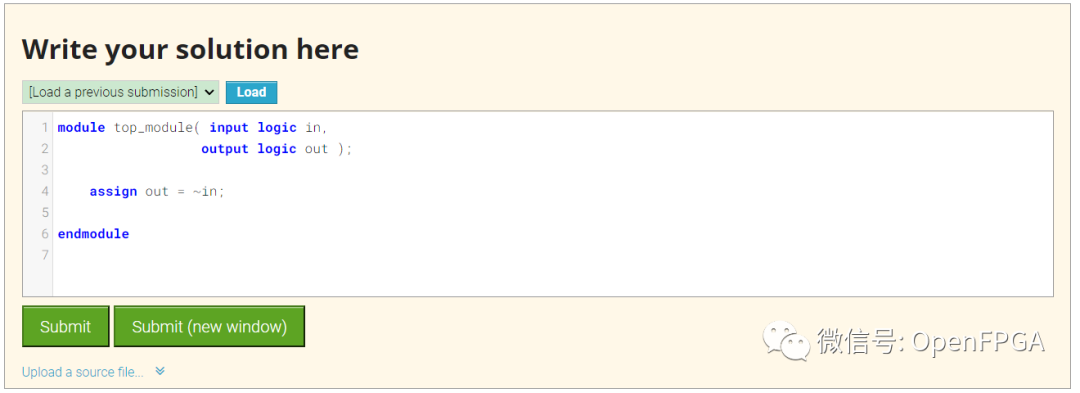

module top_module( input logic in,

output logic out

);

assign out = ~in ;

endmodule

上面使用“assign out = ~in ;”和“assign out = !in ;”无区别,因为只有一位变量。

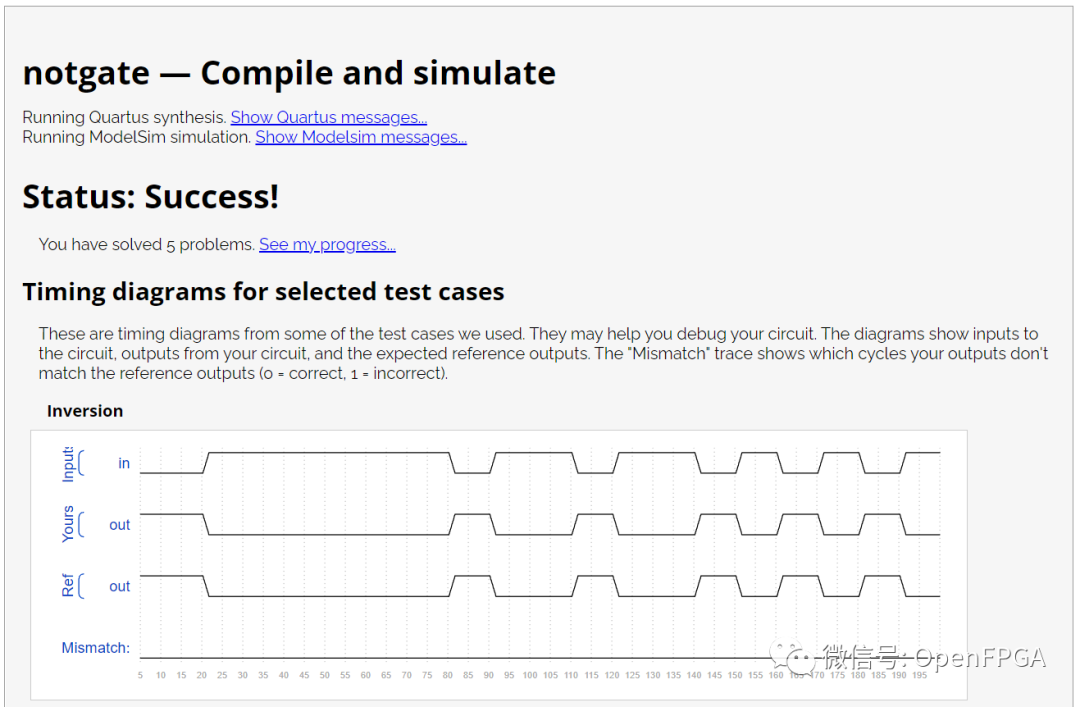

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红(后面会展示)。

这一题就结束了。

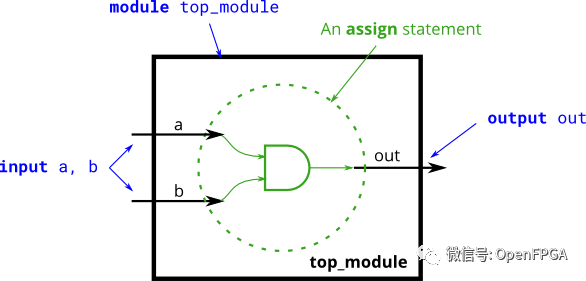

Problem 5-Andgate

题目说明

创建一个与门(Andgate)模块。。

与门的的核心就是上面的图片,模块和端口已经被定义好了,黑色的框图以及箭头代表模块和端口。我们需要做的工作是完成图中绿色的部分,实现一个与门。

模块端口声明

module top_module(

input a,

input b,

output out );

题目解析

主要使用assign语句实现与门,也很简单就一个语句“assign out = a & b;”。值得注意的是 & 和 && 的区别。

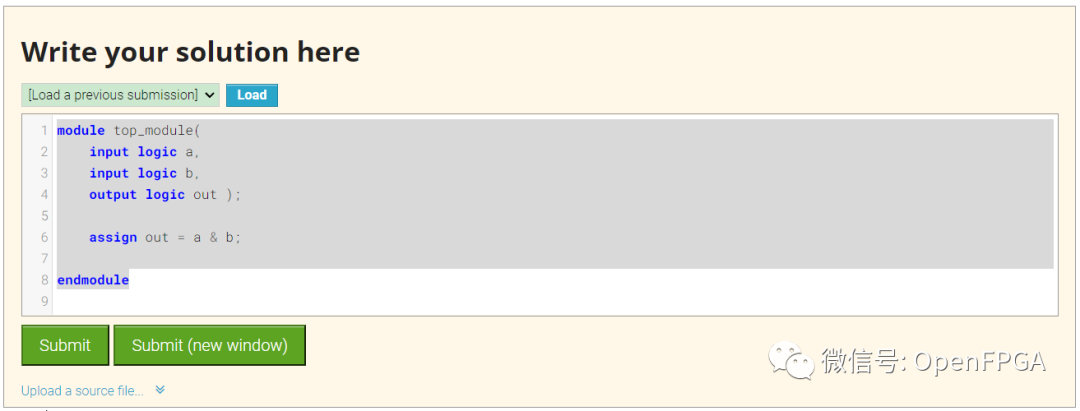

module top_module(

input logic a,

input logic b,

output logic out );

assign out = a & b;

endmodule

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红(后面会展示)。

这一题就结束了。

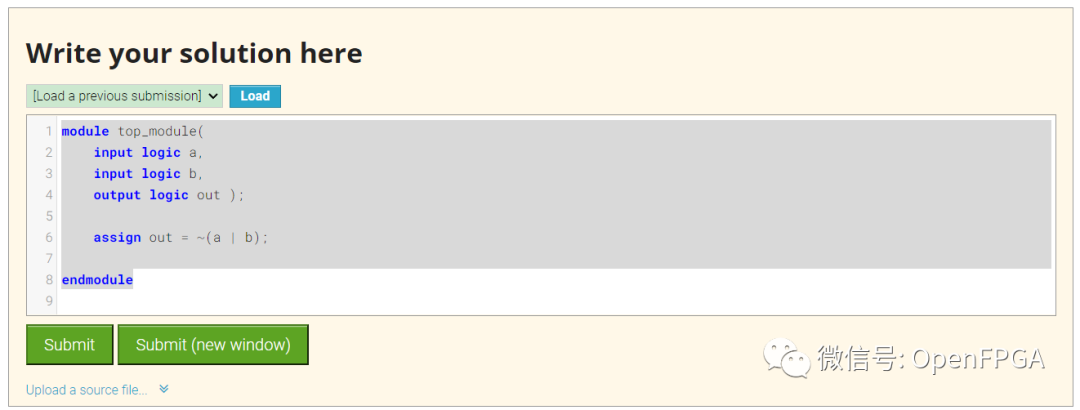

Problem 6-Norgate

题目说明

创建一个实现 NOR 门的模块。或非门(Norgate)是一个输出反相的或门。用 Verilog 编写的 NOR 门需要两个运算符。

或非门的的核心就是上面的图片,模块和端口已经被定义好了,黑色的框图以及箭头代表模块和端口。我们需要做的工作是完成图中绿色的部分,实现一个或非门。从图中可以看出就是一个或门输出取反,核心就是先实现一个或门,之后再输出端取反即可,可以使用两个assign语句或者一个assign语句实现。

模块端口声明

module top_module(

input a,

input b,

output out );

题目解析

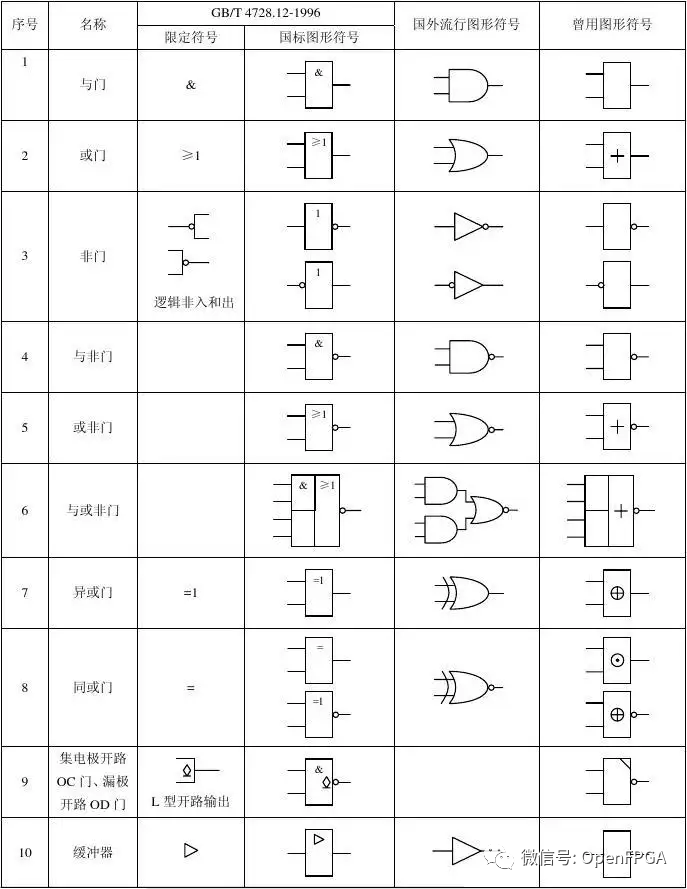

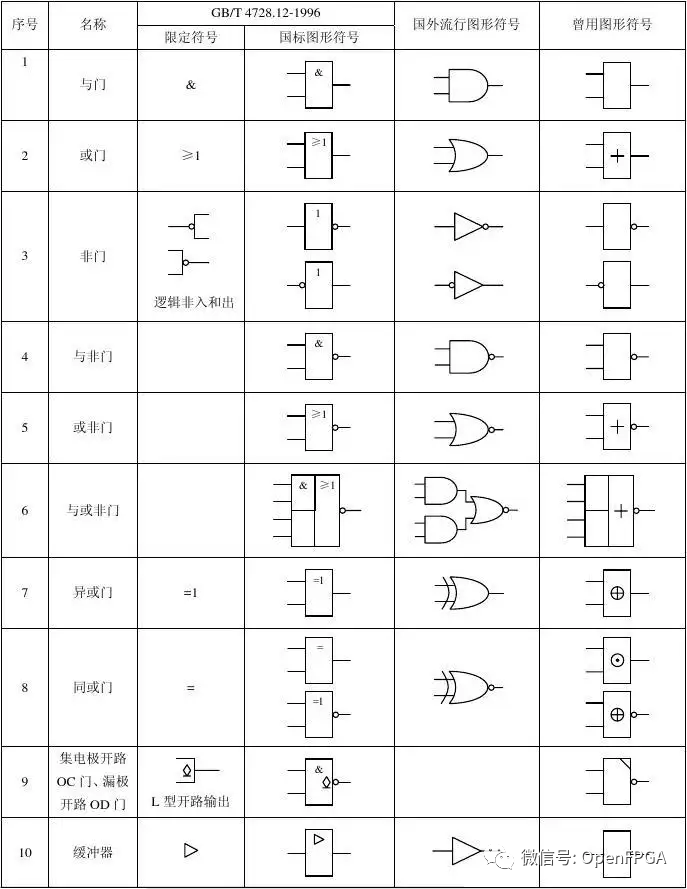

这一题的关键是看懂题目给的符号,给大家一个常用的门电路示意图:

HDLbits网站上的使用的是国外流行图形符号一栏,从题目给定的符号,对比上一图就是典型的或非门,由或门和非门组合实现。

module top_module(

input logic a,

input logic b,

output logic out );

assign out = ~(a | b);

endmodule

代码中(a|b)实现一个或门,然后取反即可~(a | b)。

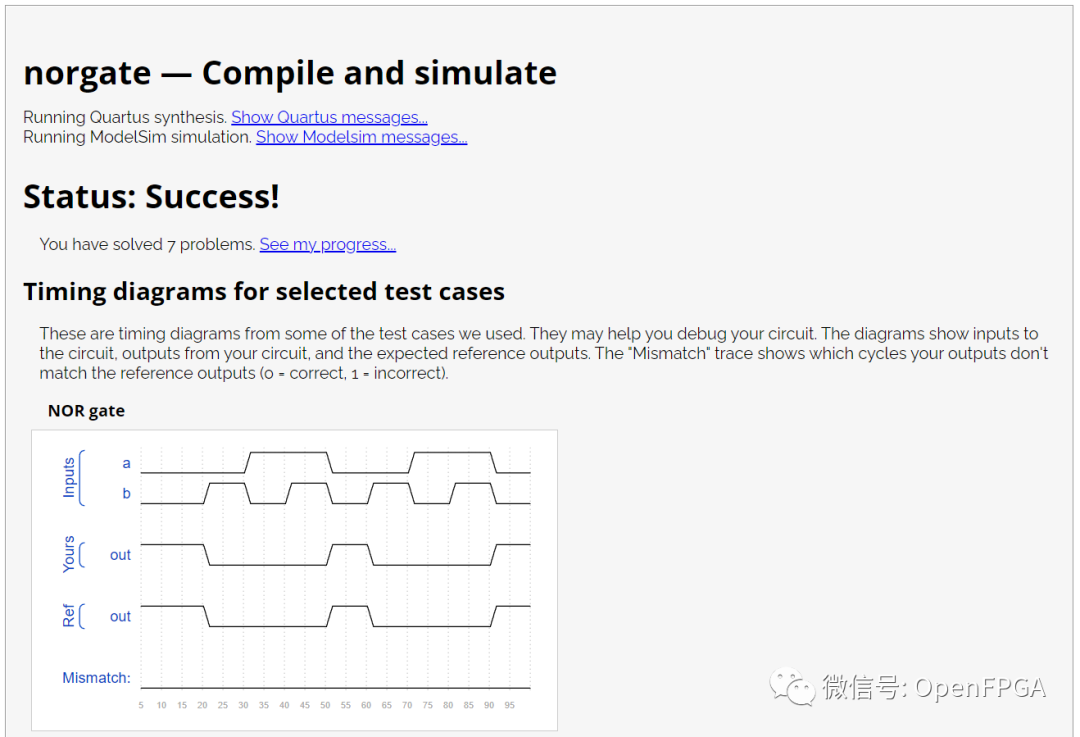

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

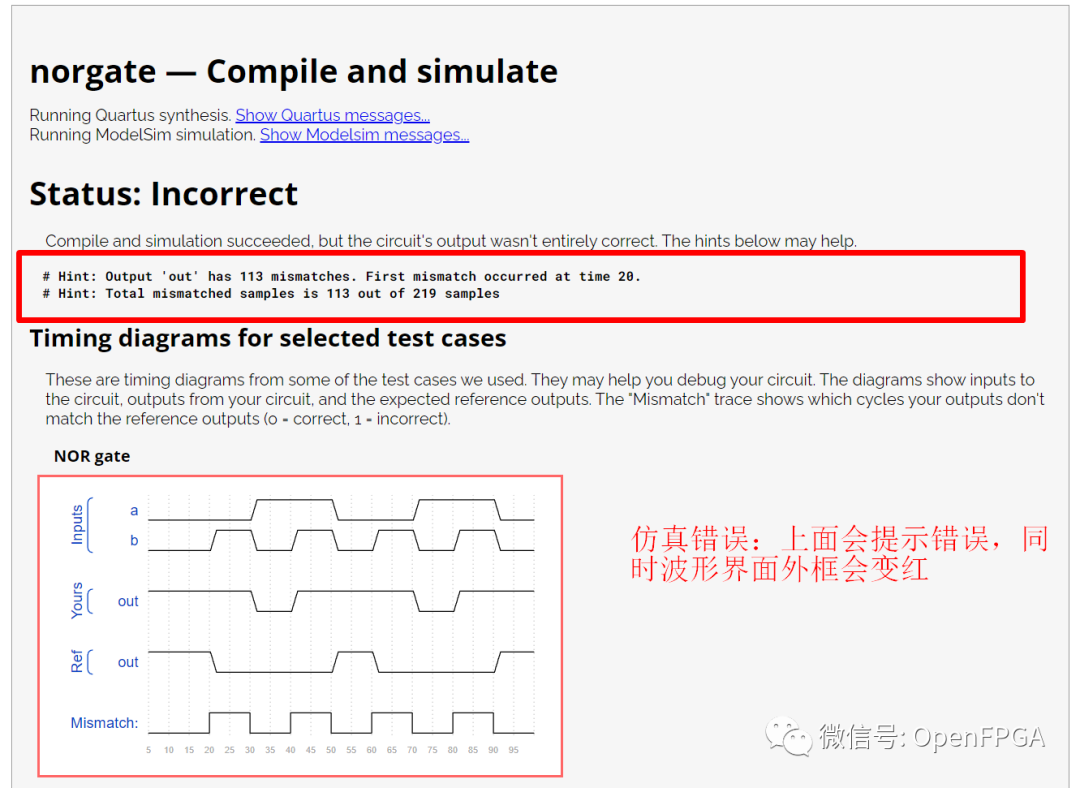

错误示范

一开始代码写错了,写成:

module top_module(

input logic a,

input logic b,

output logic out );

assign out = ~a | b;

endmodule

仿真结果如下:

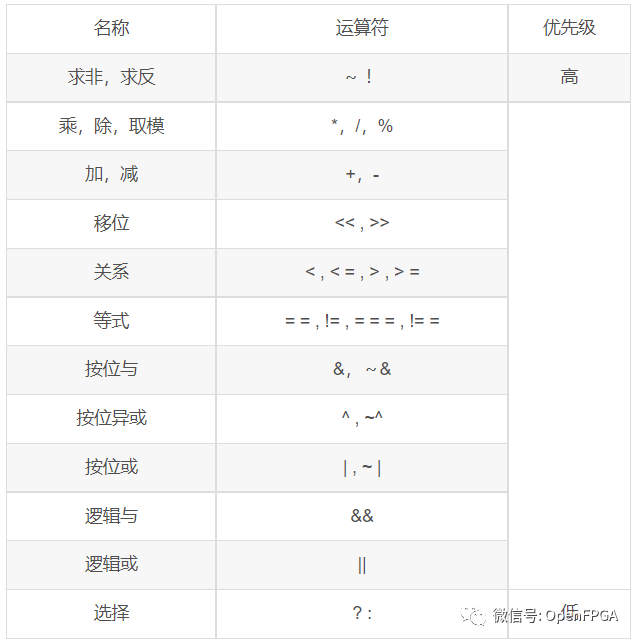

造成上面结果的主要原因还是因为Verilog/SV中逻辑操作,运算符等有优先级(和数学里的加减乘除乘除一样),具体优先级如下:

所以上面的代码会优先做~a然后在和b或,加上括号解决。

总结

今天的5道题就结束了,整体难度不大,后面的题目难度会越来越大~

最后我这边做题的代码也是个人理解使用,有错误欢迎大家批评指正,祝大家学习愉快~

代码链接:

https://github.com/suisuisi/SystemVerilog/tree/main/SystemVerilogHDLBit

-

官宣:7月7-9日,华为开发者大会2023(Cloud)2023-05-29 1392

-

在线学习SystemVerilog:移位寄存器2022-12-09 3125

-

FPGA学习-SystemVerilog语言简介2022-12-08 2997

-

HDLBits: 在线学习SystemVerilog-Problem2022-10-20 2433

-

SystemVerilog3.1a语言参考手册2022-10-19 492

-

12月7-9日!更好的相聚,CIOE中国光博会新展期定档!2022-10-08 476

-

HDLBits: 在线学习SystemVerilog(三)-Problem 10-142022-08-24 2079

-

杭州7月7-9日《硬件电路可靠性设计、测试与案例分析》开课啦!2022-06-15 1144

-

HDLBits:在线学习 Verilog (二十八 · Problem 135-139)2021-11-24 578

-

systemverilog学习教程2015-04-01 8482

-

SystemVerilog学习一 —— 计数器2012-02-21 4411

-

SystemVerilog 的VMM验证方法学教程教材2012-01-11 56813

-

Is there a problem updating fi2010-03-03 546

-

SystemVerilog Assertion Handbo2009-07-22 1014

全部0条评论

快来发表一下你的评论吧 !