一种用于3D TLC NAND的弹性纠错方案

描述

在 NAND 工艺开发中,2D NAND 在 10 nm 左右已达到极限。由于平面 NAND 技术的浮栅内部的电子较少,因此 3D NAND 结构正在成为大容量存储系统的主流。

3D NAND 结构将平面浮动栅极旋转 90 度,并在彼此顶部堆叠许多层以增加容量。3D NAND 市场的大多数厂商——包括三星、东芝/WD、美光、海力士和英特尔——现在都在批量生产 256 Gb 芯片容量的 64 层三层单元 (TLC) NAND。96 层、512 Gb 选项应该会在今年某个时候推出。

使用 ECC 克服 3D NAND 的复杂性

由于 3D 结构的复杂性,可能会出现多种错误。这些包括层间读取干扰、写入干扰和数据保留问题。尤其是在大容量系统中,所有这些问题至少需要 NAND 闪存控制器,更具体地说,需要高级纠错算法。

不幸的是,多级单元 (MLC) NAND 技术中使用的传统 Bose-Chaudhuri-Hocquenghem (BCH) 纠错码 (ECC) 算法不足以用于 3D TLC NAND。需要更强大的低密度奇偶校验 (LPDC) ECC 算法。

LPDC ECC 使用硬件和软件机制来纠正位错误。硬件机制每 1 KB 可以纠正超过 120 位错误,而软件机制使用更复杂的错误纠正方法来解决几乎两倍的错误。但是虽然它们更强大,但基于软件的 ECC 操作需要更长的时间才能执行。

除了硬件和软件校正机制之外,3D NAND 还需要一种防止大量数据丢失的方法。这意味着必须在 NAND 控制器内部实施 RAID 功能,以解决无法通过 LPDC ECC 算法纠正的错误,例如整页错误或多个数据页的损坏。这个 RAID 功能当然需要一些额外的内存来进行奇偶校验和额外的计算资源,但确保 SSD 上的数据安全是非常值得的。

3D TLC NAND 设备的安全数据序列

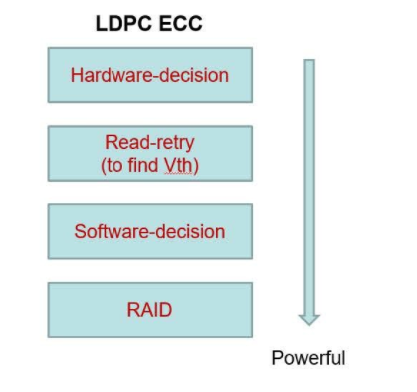

图 1 显示了 SSD 控制器的 LDPC ECC 序列,包括上述 RAID 功能。在步骤中,SSD控制器必须实现的ECC序列如下:

首先使用硬件机制(hardware-decision)

如果步骤 1 失败,请尝试实施不同的 Vth(NAND 状态的电压电平)以获得最低的误码率,也称为读取移位或读取重试

接下来,实现软件机制(software-decision)来纠正错误

如果一切都失败了,请使用内部 RAID 功能

图 1. 在 3D TLC NAND 控制器上实施此 ECC 方案提供了一种纠正位错误的过程,该过程从资源密集度最低变为最强大。

更可靠的 3D TLC NAND

3D TLC NAND 代表了存储介质的转折点,提供了更低的每比特成本和更小的占用空间。然而,为了使市场扩展到嵌入式行业,该技术需要提供一套可持续的、可扩展的比特纠错解决方案。

通过实施上述 LPDC ECC 序列,在 NAND 控制器上终止强大的 RAID 功能,UDInfo相信,未来基于 3D TLC NAND 的设备可以保证 SSD 质量和数据完整性。

审核编辑:郭婷

-

求一种3D视觉技术方案2021-11-09 2538

-

用SD NAND转TF卡可以解决3D打印机常读写错误,坏死的问题2022-07-12 1894

-

干货!一文看懂3D NAND Flash2016-08-11 44972

-

3D NAND对比2D NAND的优势2017-10-13 1816

-

英特尔与美光64层3D NAND备受关注,或将激化原厂争夺96层3D NAND技术2018-08-22 2682

-

半导体行业3D NAND Flash2018-10-08 872

-

联芸科技对外发布支持96层镁光B27A的 3D TLC NAND闪存颗粒2018-11-19 8598

-

宜鼎推出针对高阶市场应用的储存方案3TS5-P 采用全新的3D NAND TLC2019-11-18 1129

-

美光发布176层3D NAND闪存2020-11-12 4029

-

未来的3D NAND将如何发展?如何正确判断一款3D NAND的总体效率?2020-11-20 4582

-

用于3D TLC NAND的弹性纠错方案2022-06-10 2479

-

一种用于3D TLC NAND的弹性纠错方案2022-10-24 1388

-

什么是3D NAND闪存?2023-03-30 4686

-

有了2D NAND,为什么要升级到3D呢?2024-03-17 2925

-

iSUN3D即将推出单组分弹性树脂3D打印解决方案!2025-11-17 842

全部0条评论

快来发表一下你的评论吧 !