电源噪声对于高速DAC相位噪声的影响

模拟技术

描述

在所有器件特性中,噪声可能是一个特别具有挑战性、难以掌握的设计课题。本文主要介绍电源噪声对于高速DAC相位噪声的影响。

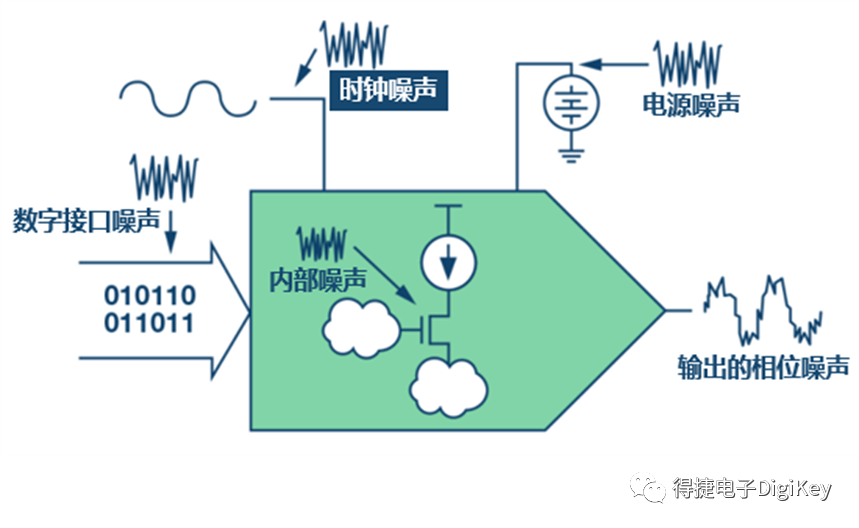

DAC相位噪声来源

对于高速DAC来说,相位噪声主要来自以下几个方面:时钟噪声、电源噪声,以及内部噪声与接口噪声。

图1:DAC相位噪声来源 (图片来源:ADI)

其中最重要的两个来源是时钟噪声与电源噪声。本文将主要介绍电源噪声对于DAC相位噪声的影响。

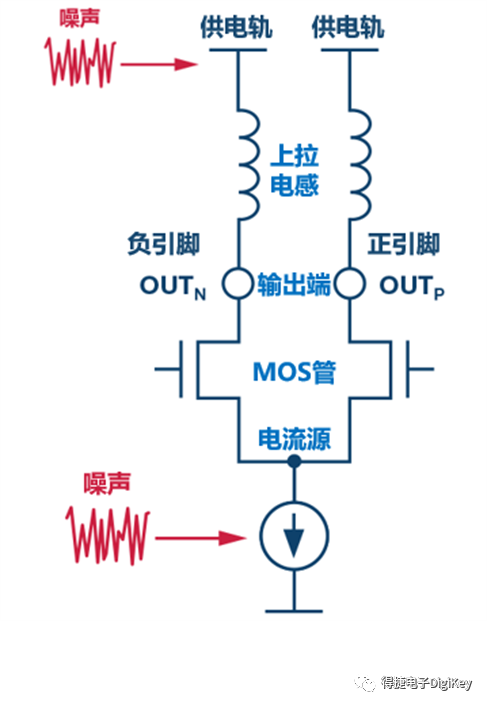

DAC电源相位噪声传播路径

芯片上的所有电路都必须通过某种方式供电,这就给噪声传播到输出提供了很多机会。不同电路电源噪声的传播路径也不一样,下面着重指出了几种常见的DAC电源噪声传播路径。

如下图,DAC输出端通常由电流源和MOS管组成,MOS管引导电流通过正引脚或负引脚供电。电流源从外部电源获得功率,任何噪声都会反映为电流波动。

图2:DAC电源噪声来源(图片来源:ADI)

MOS管

电流源的噪声可以经过MOS管到达输出端,但这仅解释了噪声的耦合现象。

图 3 : DAC电源噪声传播路径——MOS管(图片来源于ADI)

要“贡献”相位噪声,此噪声还需要通过MOS管混频到载波频率。这里的MOS管,相当于一个平衡混频器。

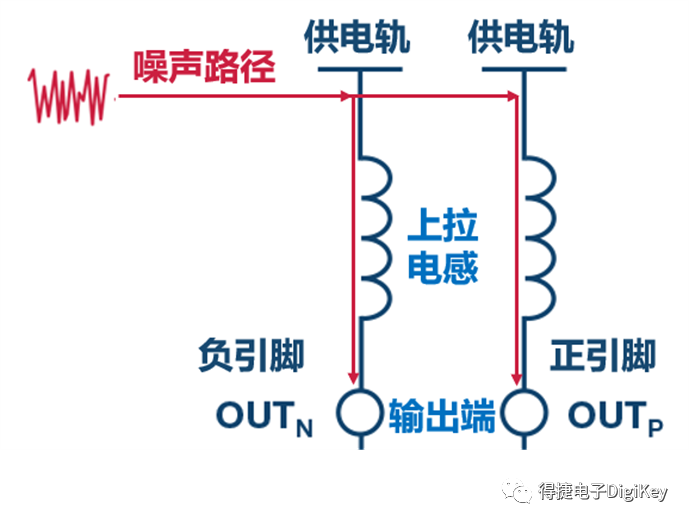

上拉电感

上拉电感是另一条噪声路径,噪声从供电轨流至输出端。

图4:DAC电源噪声传播路径——上拉电感(图片来源:ADI)

这里任何供电轨和负载的变化,都会引起电流变化,从而又一次把噪声混频到载波频率。

更多噪声传导路径

一般来说,如果开关切换能够把噪声混频到载波频率, 这些开关电路都是电源相位噪声的贡献者。

分析相位噪声

对于上面提到的混频现象,要快速模拟所有这些行为并且去改善是相当困难的。相反,通过测量电源抑制比的做法,快速了解哪些电源对噪声敏感,然后针对性地选择一些高精度低噪声的电源,才能事半功倍。

其他模拟模块也会有类似的电源抑制比的分析,比如稳压器、运算放大器和其他IC,一般都会规定电源抑制比。

电源抑制性能衡量负载对电源变化的灵敏度,可用于这里的相位噪声分析。然而,这里使用的不是抑制比,而是调制比:电源调制比(PSMR)。当然,传统的电源抑制比(PSMR) 依旧有参考意义。

我们专门调制一个噪声去测试。下一步是获得具体数据。

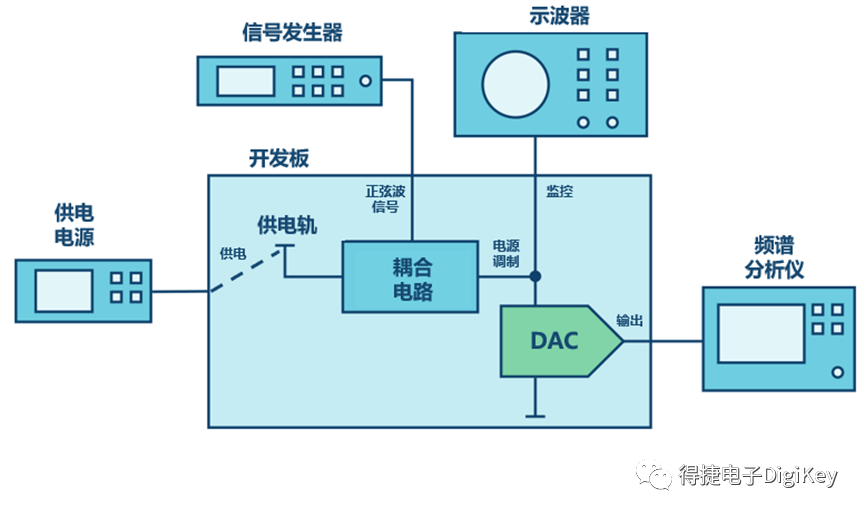

测量PSMR

分析相位噪声的很重要的一个方法便是测量PSMR。

典型测量PSMR测试原理图:

图5:PSMR测量(图片来源:ADI)

PSMR测量可以分成三步:调制供电轨,获取数据,分析数据。

调制供电轨

电源调制通过一个插在供电电源与负载之间的耦合电路获得,叠加上一个由信号发生器产生的正弦波信号。

获取数据

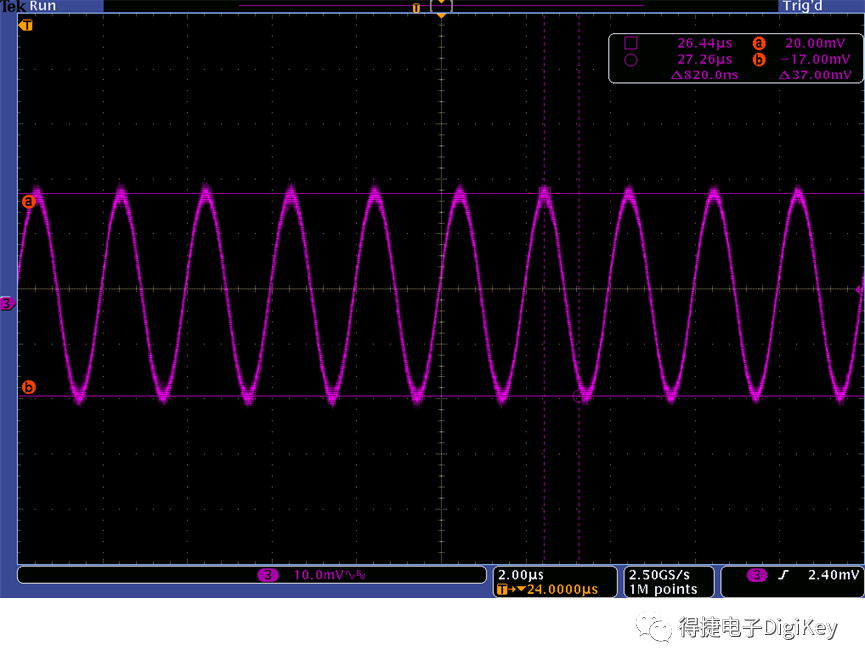

耦合电路的输出通过一个示波器监控,以监控实际电源调制。最终得到的DAC输出,由频谱分析仪检测得出。

分析数据

PSMR等于从示波器显示的电源交流分量与载波周围的调制边带电压之比。 以下是PSMR测量的几个要点:

耦合电路:耦合电路存在多种不同的耦合机制,耦合电路可以选择LC电路,电源运算放大器、变压器或专用调制电源。这里使用的方法是1:100匝数比的电流检测变压器和函数发生器。建议使用高匝数比以降低信号发生器的源阻抗。

电源调制:1.2V直流电源上叠加一个500kHz峰峰值电压38 mV信号调制所得。

图6:时钟电源调制 (图片来源:ADI)

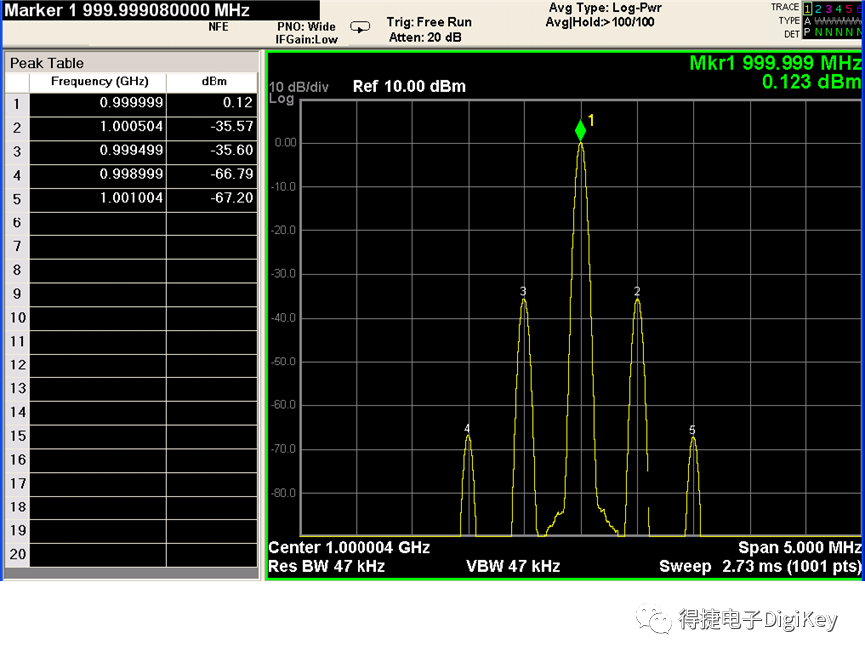

DAC: 采用的是ADI的AD9164 。DAC时钟速度为5GSPS。所得输出在一个满量程1GHz、–35dBm载波上引起边带。

图7:调制边带(图片来源:ADI)

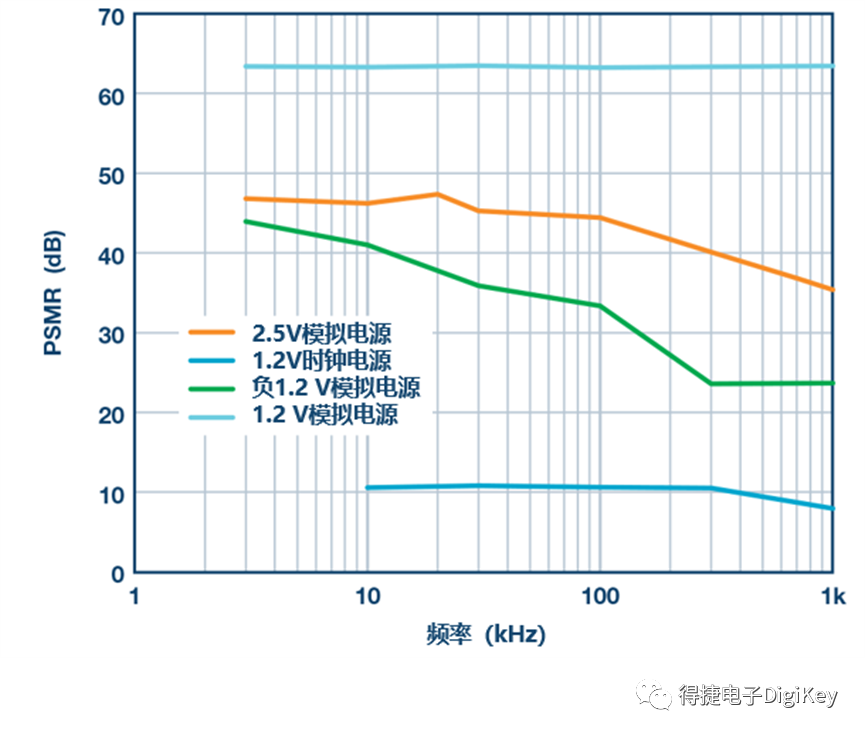

将功率转换为电压,然后利用调制电源电压求比值,所得PSMR为–11 dB。AD9164有八个电源,我们选择重点,关键扫描以下四个电源:1.2V时钟电源,负1.2 V和2.5V模拟电源,1.2 V模拟电源。结果图下图所示:

图8:扫描频率测得的电源PSMR(图片来源:ADI)

时钟电源是最为敏感的供电轨,然后是负1.2V和2.5V模拟电源,1.2V模拟电源则不是很敏感。加以适当考虑的话,1.2V模拟电源可由开关稳压器供电,但时钟电源完全相反:它需要由超低噪声LDO供电,以获得优质性能。

选择超低噪声的电源

LDO的选择

LDO是久经考验的稳压器,尤其适合用来实现优质噪声性能。对于敏感的电源轨道,也不是所有的LDO都可以胜任,依旧需要根据整体系统要求去选择与测试。

测试的方法是:利用此LDO的频谱噪声密度曲线和DAC PSMR测量结果去比对。

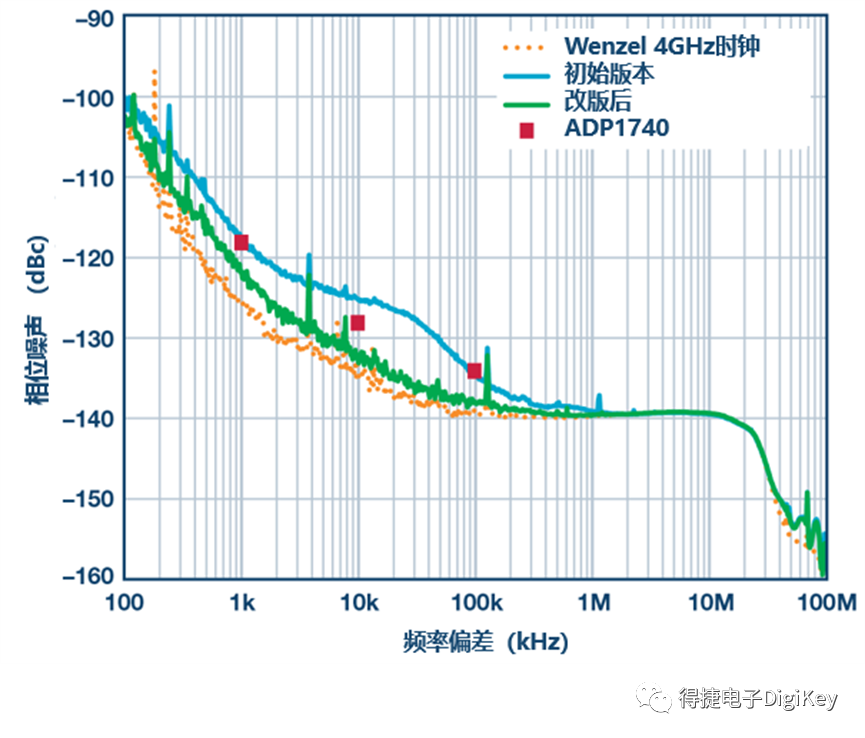

举例,某一电路,在初始的版本的时候,使用LDO ADP1740,对比LDO的频谱噪声密度曲线和DAC PSMR测量结果,如下图所示:

图9:AD9162评估板相位噪声(图片来源:ADI)

这证实了时钟电源(上图红色的点)对噪声的影响。改版后,更换使用ADP1761,某些特定频率处噪声降低多达10dB。

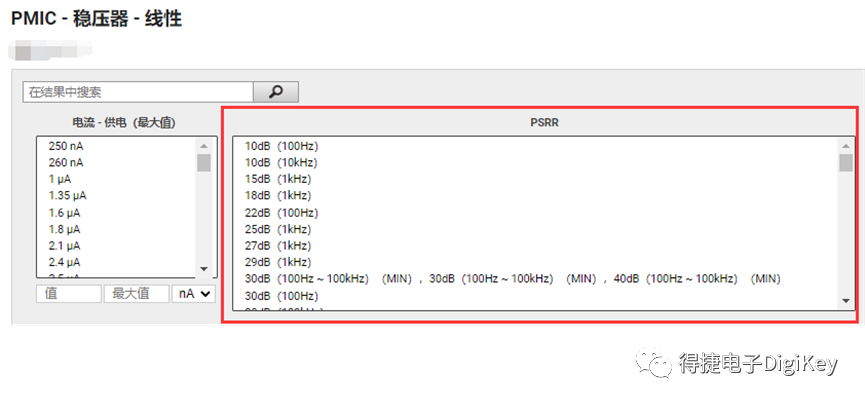

在Digi-Key网站,可以根据参数来筛选合适的Digi-KeyLDO,其中包括直接通过PSRR (电源抑制比) 来筛选的功能。

图10:通过PSRR (电源抑制比) 筛选LDO

其他方案

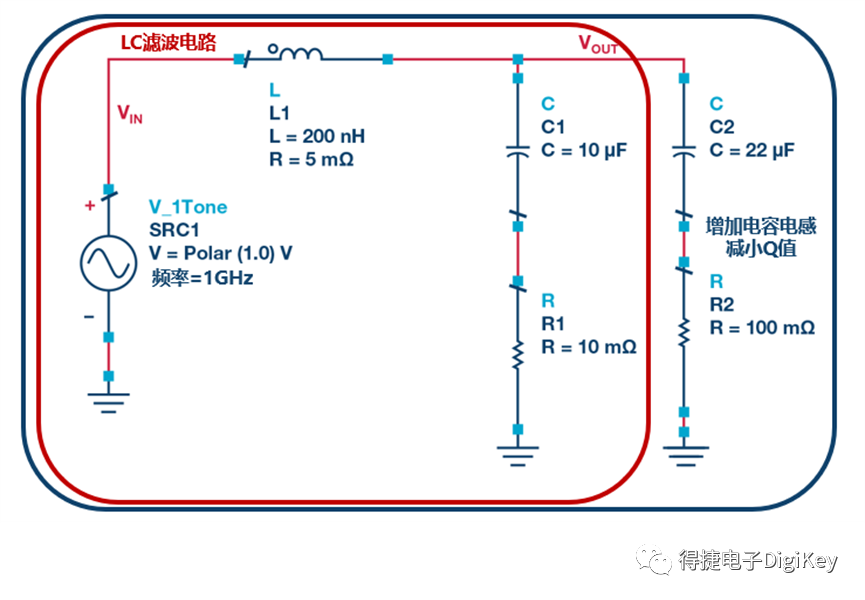

但也不意味着除了LDO, 别的电源不可以用,根据整体系统要求,通过适当的LC滤波,开关稳压器也可提供电源,从而简化电源解决方案。但由于采用LC滤波器,所以应注意串联谐振,否则噪声可能变得更糟。对于谐振可通过对电路降低Q值——如给电路增加损耗性元件——加以控制。

下图显示了来自另一个设计的例子,其采用AD9162 DAC。时钟电源也是由ADP1740 LDO提供,但其后接一个LC滤波器。

图11:LC滤波器和去Q网络 (图片来源:ADI)

原理图中显示了所考虑的滤波器,RL模型表示电感,RC模型表示主滤波电容 (C1+R1)。

红圈里是原始的LC滤波电路,蓝圈是为了减小Q值额外增加的损耗性元件。

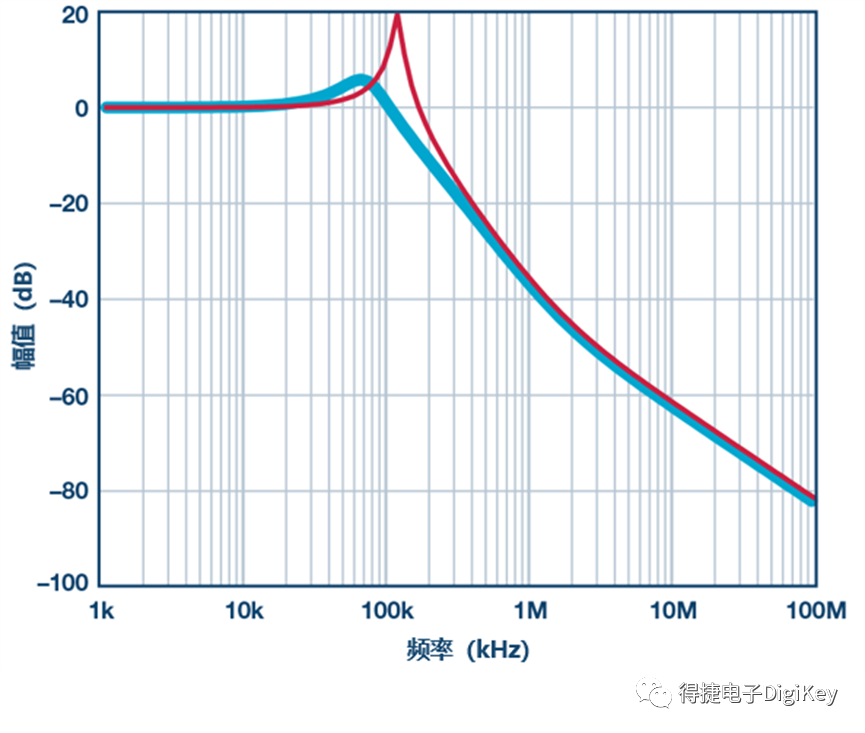

图12:LC滤波器响应(图片来源:ADI)

滤波器响应如下图所示,红线是原始的LC电路响应曲线,蓝线是改进后的响应曲线。我们看到Q值减小了。

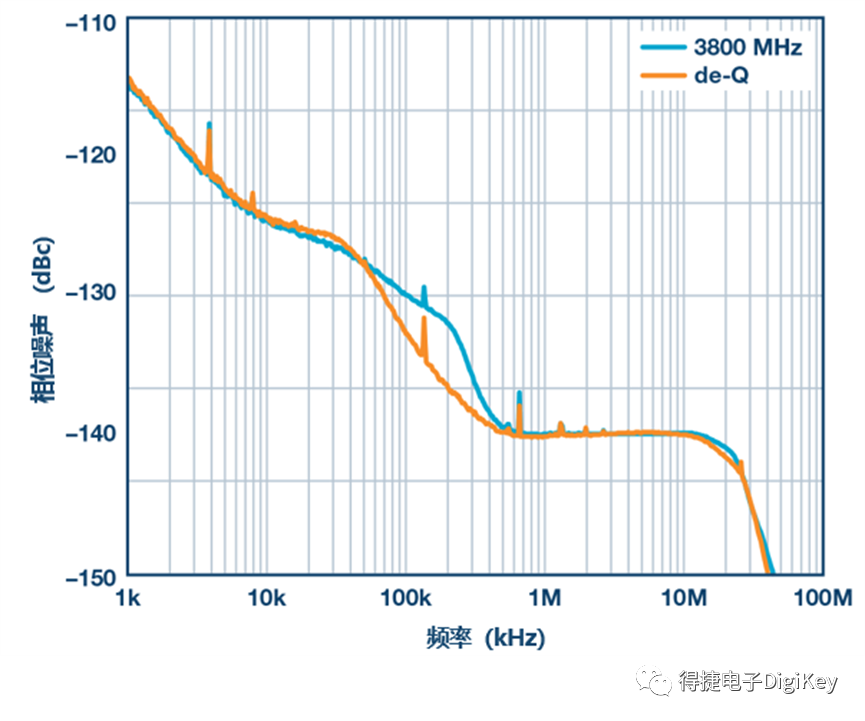

图13:相位噪声响应(图片来源:ADI)

我们再来看看,对于相位噪声响应,蓝线是原始的LC电路响应曲线,橙线是改进后的响应曲线。相位噪声得到改进。

本文小结

噪声不仅会因为电源选择的不同而大不相同,而且可能受到输出电容、输出电压和负载影响。应当仔细考虑这些因素,尤其是对于敏感的供电轨。

审核编辑:汤梓红

-

高速DAC相位噪声从何而来?首要的原因原来是它……2023-11-29 1175

-

分析和管理电源噪声和时钟抖动对高速DAC相位噪声的影响2023-01-04 4731

-

巧用LC滤波器额,改善高速DAC电源相位噪声2022-11-21 1967

-

高速DAC相位噪声从何而来?2022-11-10 1302

-

时钟噪声对于高速DAC相位噪声的影响2022-07-28 1856

-

电源噪声和时钟抖动对高速DAC相位噪声有什么样的影响2020-11-19 1154

-

电源噪声和高速DAC的相位噪声有什么影响应该如何解决2020-10-06 2387

-

电源噪声和时钟抖动对高速DAC相位噪声有什么影响2019-07-24 1509

-

DAC相位噪声性能改进包含残余相位噪声测量方法和最佳稳压器选择2019-03-19 3622

-

电源噪声和时钟抖动对高速DAC相位噪声的影响分析及管理2018-10-17 4448

-

电源噪声和时钟抖动对高速DAC相位噪声的影响2018-03-08 1125

-

改进的DAC相位噪声测量2018-03-07 1025

-

电源噪声和时钟抖动对高速DAC相位噪声的影响的分析及管理2017-05-10 6885

全部0条评论

快来发表一下你的评论吧 !