LVDS差分接口信号输入输出的处理简析

接口/总线/驱动

描述

最近调试芯片遇到一个选择题,需要决定数据接口的接口标准,是选用LVDS差分接口还是CMOS单端接口。说实话,之前接触多的还是CMOS单端接口,只是看到过很多资料介绍过LVDS差分接口。

官方说法里,它的主要优点有:

抗干扰能力强,具有更高的数据传输速率

更好的信号完整性

降低了电平幅度和电路功耗

既然有这么多优点,这次我们就选用LVDS差分接口,看看我们能不能感受到LVDS的优势。

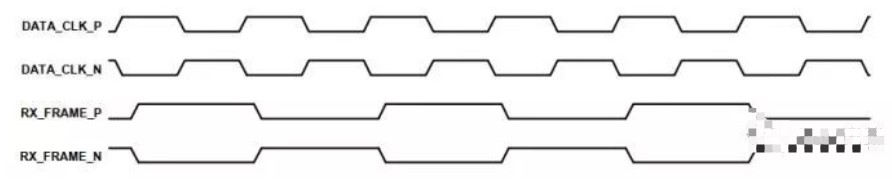

每对LVDS信号是一个差分信号对,一个信号用两个相反的p,n信号线表示,通过差值 |Vp - Vn|传输数据,这样可以有效减小共模噪声的干扰,信号线传输如下图:

图中含有DATA_CLK, RX_FRAME两个LVDS信号对

而FPGA内部处理信号肯定还是需要使用单端信号,这时就需要经过一个差分转单端的“工具”,将差分信号转换为FPGA更方便处理的单端信号。

在Xilinx中,我们可以用IBUFDS原语,可以在Language Template中找到这个原语的示例,经过修改一番后,可以将差分的data_clk转换为单端的data_clk, 原语如下:

IBUFDS #(

.DIFF_TERM("FALSE"), // Differential Termination

.IBUF_LOW_PWR("TRUE"), // Low power="TRUE", Highest performance="FALSE"

.IOSTANDARD("DEFAULT") // Specify the input I/O standard

) IBUFDS_inst (

.O(data_clk_tmp), // Buffer output

.I(data_clk_p), // Diff_p buffer input (connect directly to top-level port)

.IB(data_clk_n) // Diff_n buffer input (connect directly to top-level port)

);

将需要转换的data_clk P端和N端接入IBUFDS的I和IB端口,就可以在O端口得到转换的单端信号。

除了CLK时钟信号,其他信号的输入转换基本结束了;而CLK时钟信号还需要接入BUFG,因为CLK时钟只有接入BUFG才能接入全局时钟网络,这对于减小时序问题有帮助。

同样在Language Template中找到这个原语的示例,修改后如下:

BUFG BUFG_i0 (

.O(data_clk), // 1-bit output: Clock output, 36MHz.

.I(data_clk_tmp) // 1-bit input: Clock input, 36MHz.

);

一个输入一个输出,非常简单的原语调用!

另一边,有输入就会有输出,输出的问题也好解决,同样使用一个OBUFDS原语实现单端转差分,在Language Template中找到原语,修改后如下:

OBUFDS #(

.IOSTANDARD("LVDS18"), // Specify the output I/O standard

.SLEW("SLOW") // Specify the output slew rate

) OBUFDS_inst (

.O(tx_frame_p), // Diff_p output (connect directly to top-level port)

.OB(tx_frame_n), // Diff_n output (connect directly to top-level port)

.I(tx_frame) // Buffer input

);

设置好相应的参数之后,将单端信号接入OBUFDS的I端口,O端口输出差分信号的P端,OB端口输出差分信号的N端。

最后一个小问题就是在XDC设置中,因为一个信号对有两个管脚,比单端信号多了一倍的管脚绑定工作量;但其实我们可以只需要绑定P端的管脚,软件会自动帮我们绑定N端的管脚。

在设置输入输出端口的“IOSTANDARD”中,遇到了些许问题,这里写出来记录一下,也让后面遇到这个问题的人有个参考;最初设置差分信号的“IOSTANDARD”时,我想当然的使用了“LVDS”,“LVDS18”等参数,但是这些参数都不能最终生成比特流;

在查了一些资料以及Vivado本身的I/O Port界面里参数后发现,差分信号的IOSTANDARD需要这样设置:

set_property IOSTANDARD DIFF_HSTL_II_18 [get_ports tx_frame_p]

因为我的IO电压是1.8V,所以最终使用了“DIFF_HSTL_II_18”,如果有更好的方案,可以一起探讨探讨。

总结:

输入信号需要用到IBUFDS实现差分转单端,输入时钟还需要加BUFG

输出信号使用OBUFDS实现单端转差分

差分信号只需要绑P端管脚,“IOSTANDARD”设置需要注意

输入输出端口的简单处理之后,这些信号为了提高传输数据的效率,还使用了DDR(Double Data Rate)技术传输数据,如何解决DDR问题,下一篇文章再来探讨。

审核编辑:刘清

-

PGA5807差分输入差分输出,可否改成单端输入输出?2024-08-21 782

-

Z-turn底部的DIP扩展接口支持LVDS差分输入输出吗?2015-04-03 3635

-

请问超高速比较的是否有差分输入,LVDS输出的?2018-08-07 1946

-

Input接口信号的比较2019-09-23 2867

-

以太网的接口信号在PCB走线的时候差分可以不等长么?2023-04-07 2950

-

输入输出总线接口技术2006-06-29 670

-

DVD视频刻录机的输入输出接口2009-12-23 2340

-

MCS-51 数字信号输入输出接口电路2016-12-11 776

-

数字信号输入输出接口电路2016-12-16 1094

-

LTC6362LT5400演示电路-采用匹配电阻的差分输入输出ADC驱动器2021-06-05 950

-

龙迅HDMI接口信号转换的应用案例2022-06-14 5926

-

LVDS差分信号输入输出的处理方法2023-06-16 4245

-

输入输出电压差与效率的关系2024-01-05 1868

-

差分输入至差分输出电路设计2024-11-30 1459

-

IGBT的原理,输入输出和控制信号2025-12-06 3168

全部0条评论

快来发表一下你的评论吧 !