介绍一种OSERDES级联使用的方法

描述

使用ISERDES接收高速串行数据 已经讲完了ISERDES,那么这一篇继续讲解OSERDES相关内容;

OSERDES实现并串转换,只需要管发送并不需要管接收到的数据如何,所以它的操作相对于ISERDES来说简单;

本文将介绍OSERDES的IP核生成,OSERDES原语介绍,OSERDES级联使用以及ISERDES,Idelay接收串行数据的几种方法。

与上一篇文章的结构对应,这篇也将从可视化的SelectIO的设置讲起,从简单到复杂;

在IP Catalog里面找到"SelectIO",接下来跟着这般操作:

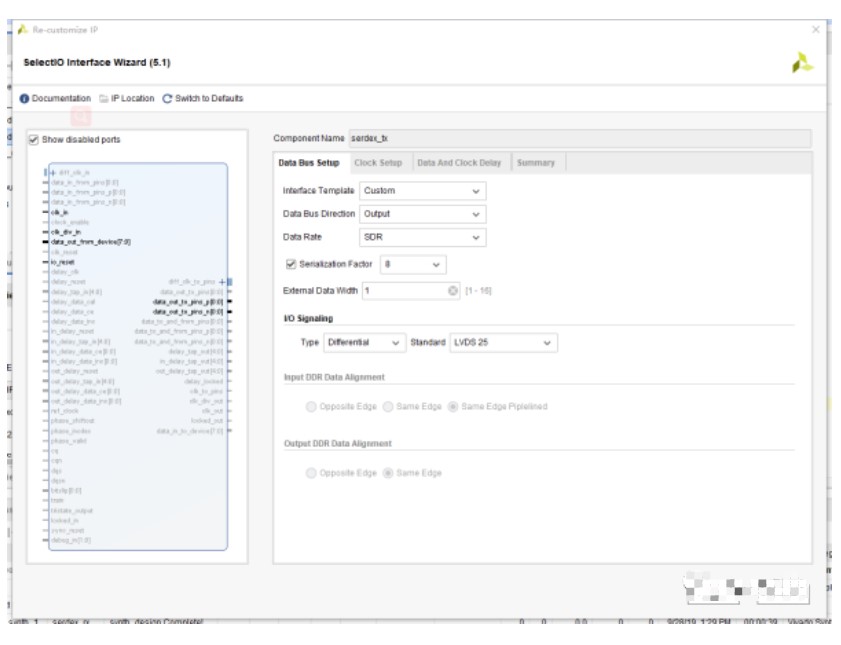

数据总线设置

参数的意义如下:

Interface Template:接口模板,本次数据传输并不符合预设的协议,所以选择Custom

Data BUS Direction:这一次需要发送数据,选择Output

Data Rate: 数据总线是SDR还是DDR,DDR内容可以看(LVDS差分信号简单处理)2. DDR信号的处理

Serialization Factor: 串化因子,也就是IP核的输入并行数据位宽;SDR Rate:可设为2,3,4,5,6,7,8;DDR Rate:可设为4,6,8,10,14;

External Data Width: 外部输出数据的位宽,默认设1

I/O signaling:设置差分还是单端以及IO电压标准

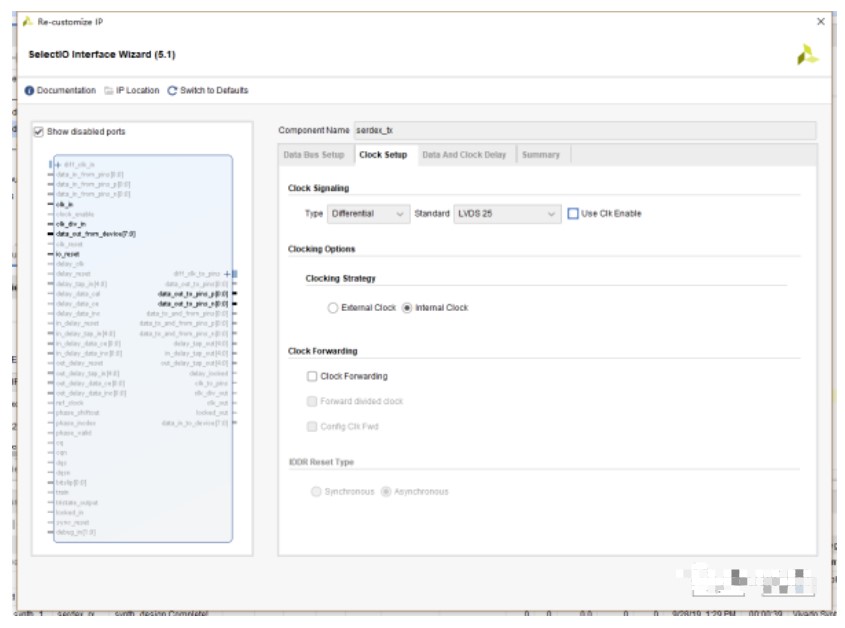

时钟设置

这一部分的内容可以参考使用ISERDES接收高速串行数据,内容一样;

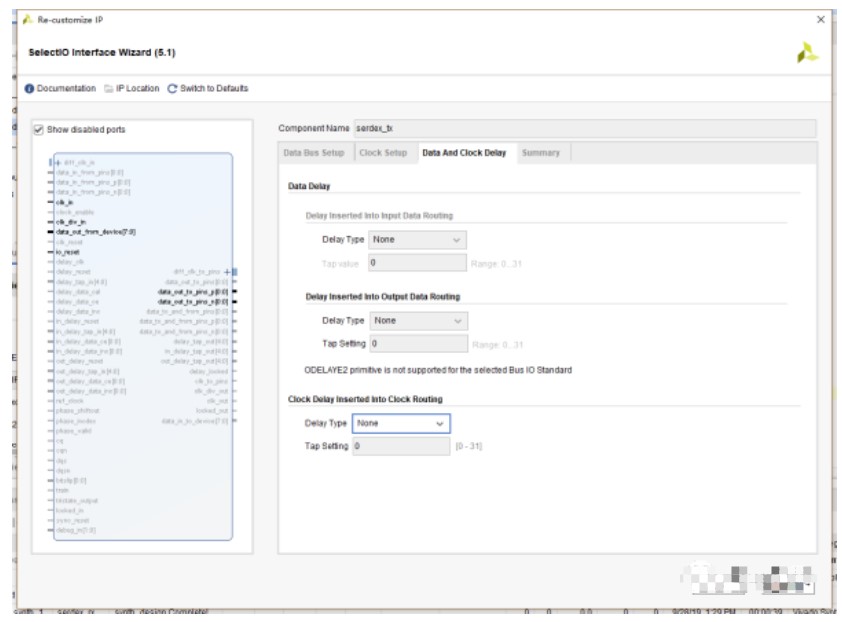

数据和延时设置

这个地方不做设置的原因是因为,我们在测试ISERDES和OSERDES,需要排除使用Idelay的影响,因此这个地方不做任何延时;

最后一键OK,OSERDES的相关IP核就生成好了。从IP核最底层的verilog文件可以看到,它的实现跟OSERDES2原语有关,从UG471我们可以知道OSERDES2的相关内容;

首先关注OSEDES2的属性内容,它的重要属性决定的因素如下:

DATA_RATE_OQ:决定OQ端口输出的数据速率,可选SDR或DDR;

DATA_RATE_TQ:决定TQ端口输出的数据速率,可选BUF, SDR或DDR;

DATA_WIDTH: 根据"DATA_RATE_OQ"确定具体数值;SDR Rate:可设为2,3,4,5,6,7,8;DDR Rate:可设为4,6,8,10,14;

SERDES_MODE:确定OSERDES是主模块还是从模块,这跟OSERDES级联使用有关,具体内容请看下面的内容;

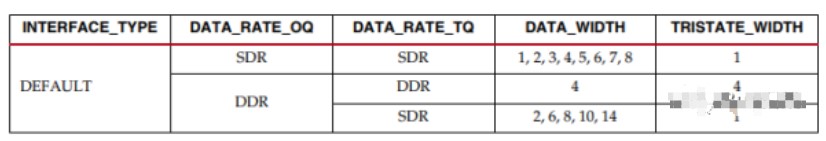

TRISTATE_WIDTH:这跟"DATA_RATE_TQ"有关,大多情况都设为1,它的具体设置关系如下:

TRISTATE_WIDTH设置参数表 UG471 Table 3-8

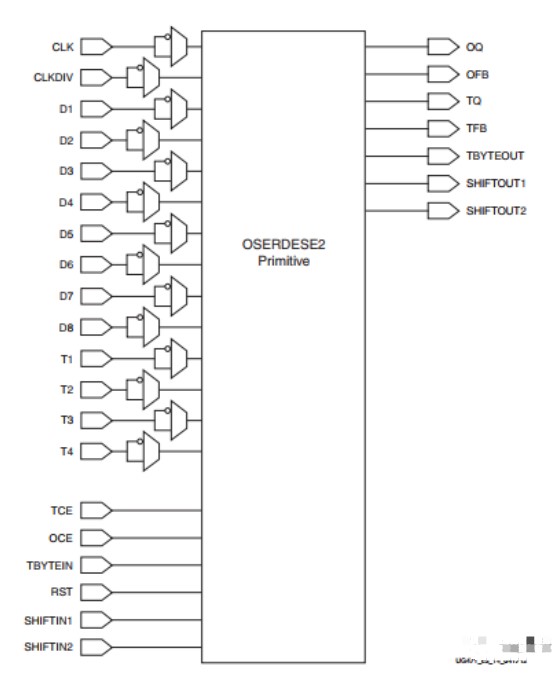

OSERDES原语图 UG471 Figure 3-14

OSERDES原语的端口定义如上图所示,其中重要的端口设置如下:

OQ:串行数据输出,直接到IOB,也就是直接连接到IOBUF,ODELAY等特殊结构

SHIFTOUT1/2:级联时使用,详见下文

CLK:高速时钟,串行数据时钟输入

CLKDIV:慢速时钟,并行数据时钟输入

D1 to D8:并行数据输入,当并行数据多于8bit不超过14bit,可以使用OSERDES级联,级联的使用方法详见下文

OCE:串行数据时钟使能信号输出

RST:高复位信号输入

SHIFTIN1/2: 级联时使用,详见下文

其他没有提到的输入信号可以设为0,输出信号可以不用连接;

CLKDIV与CLK的联系:

假设接收的串行数据时钟为256MHz,串化因子为8,则CLKDIV为32MHz;

SDR:CLKDIV = CLK/DATA_WIDTH

DDR: CLKDIV = 2 * CLK/DATA_WIDTH

注意CLK和CLKDIV不一定是相位对齐的;

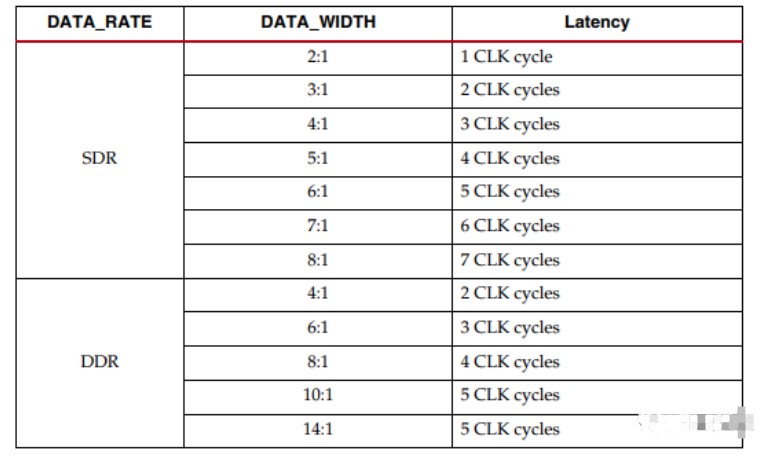

OSERDES2数据时延:

虽然与ISERDES2相比,没有"Mode"属性设置,但CLK和CLKDIV不一定是相位对齐的,它的输出数据相对于输入数据也有相应的时延,具体的延时与DATA_WIDTH,DATA_RATE_OQ,DATA_RATE_TQ有关;关系如下:

OSERDES时延参数对照表 UG471 Table 3-11

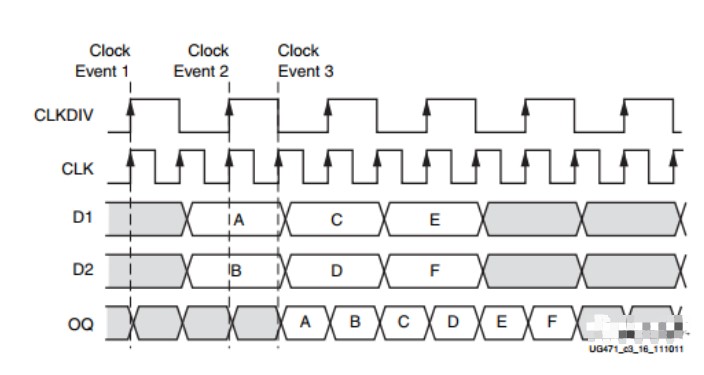

以最简单的2:1 SDR串化为例:

2:1 SDR UG471 Figure 3-16

Event1时,数据从FPGA其他部分逻辑传到OSERDES2的D1-2端口

Event2时,数据在CLKDIV上升沿被OSERDES2采样

Event3时,OQ端口产生相应的输出串行数据

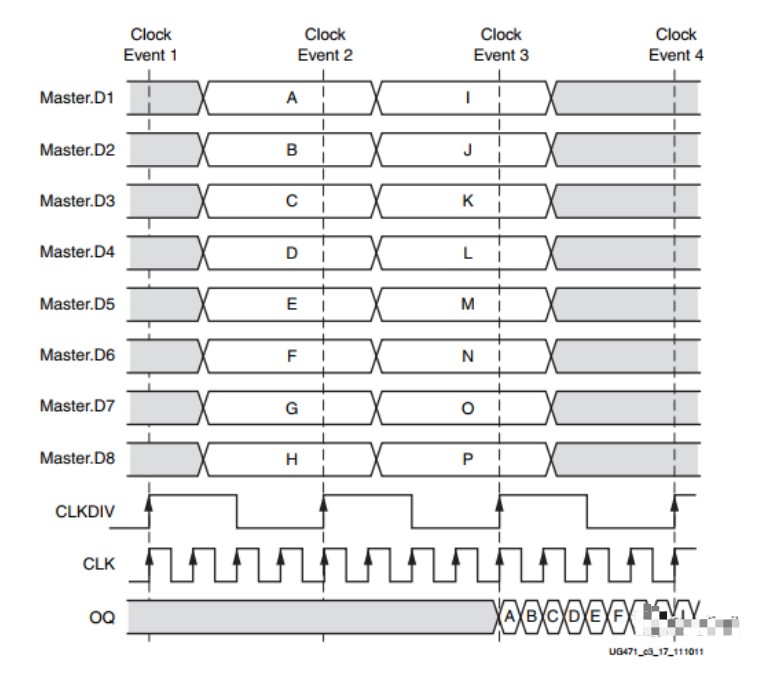

所以,是不是也可以推出下图Event所发生的事情呢?条件为8:1 DDR。

8:1 DDR UG471 Figure 3-17

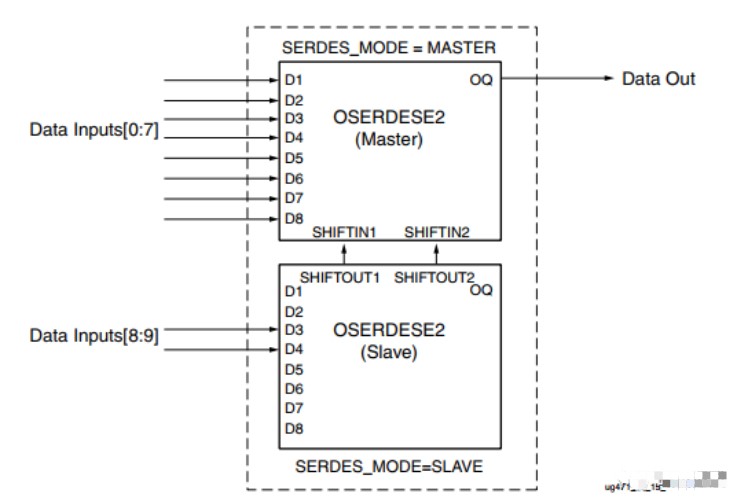

OSERDES级联使用:

当并行数据多于8bit不超过14bit时,可以采用两个OSERDES2级联的使用方法,示意图如下,

扩展并行输入数据位宽 UG471 Figure 3-15

上图已经示意的比较清楚,操作步骤可分为三步。

两个OSERDES2的"SERDES_MODE"设置,一个需要设为"MASTER",另一个设为"SLAVE";

将"SLAVE"的"SHIFTOUT1/2"连接至"MASTER"的"SHIFTIN1/2";

"MASTER"的D1-D8输入并行数据的低8位,"SLAVE"的D3-D8可以连接输入并行数据的高6位;

我在调试一款AD的过程中接触到了SelectIO中的相关知识,由表及里,看过一些I/OSERDES接收数据的调节方法:

首先让发送方发送特殊字符,接收方接收数据转为并行数据,调节Idelay的参数,直到出现稳定的结果(不一定是发送的特殊字符),Idelay参数记为C1;

继续调节Idelay的参数,直到结果不再稳定,Idelay参数记为C2;

Idelay参数设为(C1+C2)/2 ,此时接收的并行数据稳定为一个定值;

如果稳定的输出结果不是约定的特殊字符,调节Bitslip移动字符的边界,直至输出结果为约定的特殊字符;

利用其他的通信方式或方法,告知发送方可以正常发送数据;

更有甚者直接使用ISERDES,Idelay调节CLK,

将CLK作为串行数据,使用ISERDES转为并行数据后,调节Idelay;

记录最后一次并行数据全为0的时候的Idelay参数C1;

继续调节,记录第一次并行数据全为1的时候的Idelay参数C2;

Idelay参数设为(C1+C2)/2 ,此时CLK的时钟对应数据的位置裕量充足;

仿真结果可以参看使用ISERDES接收高速串行数据

总结:

OSERDES2可以使用SelectIO IP核设置简化原语设置流程;但OSERDES2原语设置会更加精细。

OSERDES的数据时延以及级联使用方面见上面的内容。

补充了ISERDES,Idelay调节接收的串行数据的方法,详细内容以后有机会再展开。

审核编辑:刘清

-

请问怎么设计一种级联型多电平变流器?2021-04-14 2253

-

介绍一种防止相位假信号的具体算法2021-04-30 1027

-

给大家介绍一种PCB设计复用方法2021-05-06 2049

-

给大家介绍一种软件修正方法2021-05-07 2417

-

介绍一种可以高精度的测量电阻的方法2021-05-10 2088

-

分享一种数字秒表设计方法2021-05-11 1963

-

介绍一种基于分级的RFID隐私保护方法2021-05-26 2100

-

介绍一种嵌入式系统仿真方法2021-11-08 1622

-

介绍一种使用WSL来编译nodemcu固件的方法2022-02-15 1040

-

一种小样本支持的多级最小模级联相消器2010-03-05 2560

-

一种新型的级联型多电平逆变器研究2006-03-11 5702

-

一种改进的级联型多电平变换器拓扑2006-04-21 1658

-

一种实用级联式多电平逆变器SVPWM方法研究2016-03-30 525

-

一种直流侧电容电压检测与控制方法2018-03-15 1211

-

AN27A--级联二阶段设计阶数全极点带通滤波器的一种简单方法2021-04-29 984

全部0条评论

快来发表一下你的评论吧 !