分享两种Comparator动态噪声的仿真方法

描述

高速ADC一直是个特别火的课题,无论是科研还是实际项目。与此同时,高速动态comparator的设计也就随之非常普遍。在这里,作者君想跟大家分享一下自己所采用的两种对comparator input referred noise的仿真方法。大家有什么疑问或者经验分享,请在评论区留言。

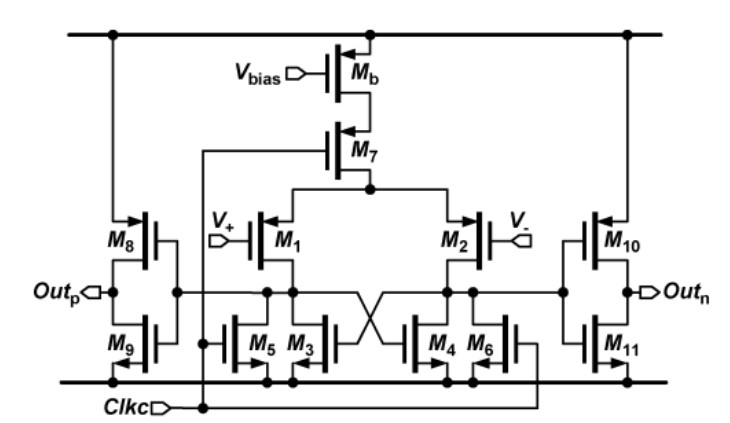

一个典型的dynamic comparator,如图所示:

这篇来自CC.Liu的SAR ADC 设计,目前citations已经过千,想必很多读者都看过了。没看过的建议去看看,确实是经典。

对于一个这样的comparator,没有传统的模拟pre-amp,整个电路都是dynamic的。因此,如何对input referred noise进行仿真呢?作者君有如下两种方法:

Transient noise

大致的思路是这样的:

加一个快于实际工作的时钟频率;

在输入端加一个DC的差(比如一端是0.5VDD,另外一端加0.5VDD+0.2mV);

计算仿真时间内的counting number,和correct counting number(比如时钟频率是1GHz,仿真时间是1us,那么应该是1000个counts;用viva的calculator计算正确的counts);

扫描不同的输入DC差之下,正确的counts的数量(比如输入差是0.1mV,0.2mV,0.3mV,etc.);

当正确的counts数量大约是84%的时候,我们认为此时的input差就是一个sigma(50%+0.5*68%=84%);

当PVT改变的时候,可以不断重复上面的步骤,来求得对应的sigma;

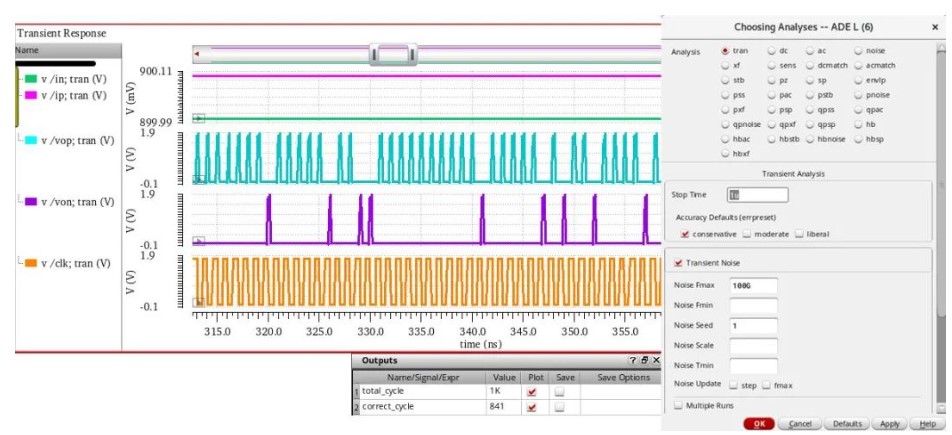

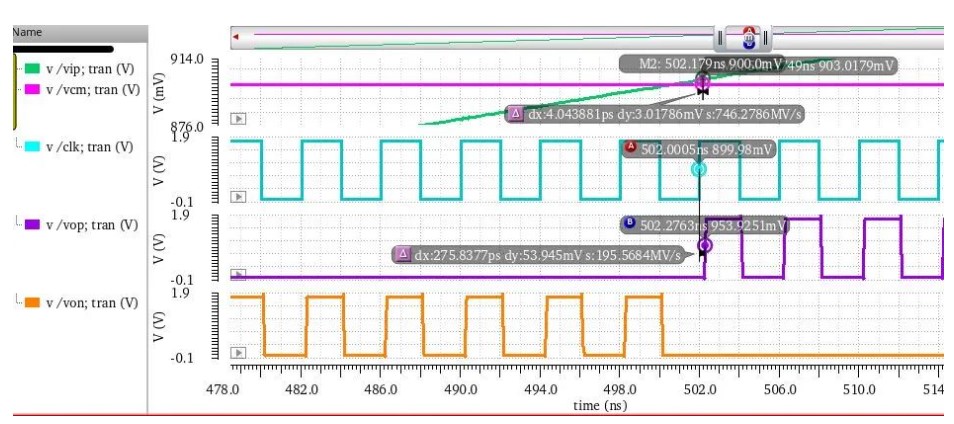

Transient Noise settings and simulation results (Input difference is 0.1mV)

作者君的transient noise设置和仿真结果如上图。可以看到,当input的差别很小的时候(Vip大于Vin),本来应该是只有Vop出现pulse,Von全部应该是0。但是由于noise的存在,导致某些错误的输出。

按照前面的方法,用calculator计算出全部和正确的counts数量。可以看到,目前的正确counts大概是84%,也就是对于一个input referred noise sigma.

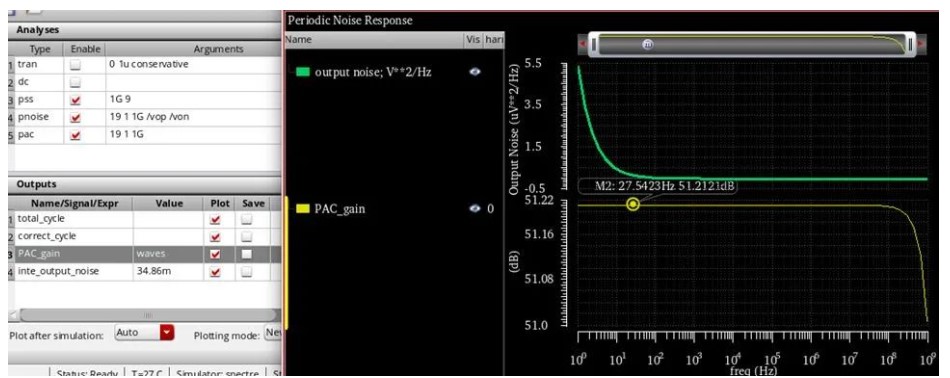

PSS+Pnoise

大致的思路是这样的:

加一个快于实际工作的时钟频率;

在输入端加一个DC的差;

采用PSS,PAC, Pnoise的仿真;

Pnoise计算出integrated output noise(用V^2/Hz作积分然后sqrt做开方);

PAC计算出comparator的gain;

第四步得到的noise除以第五步得到的gain,就是input referred noise;

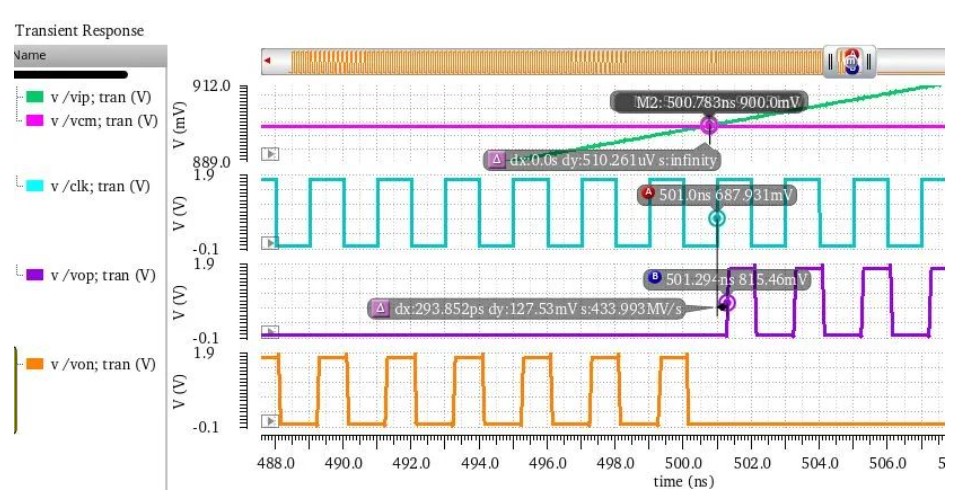

Input difference is 0.1mV.Pnoise integration is from 1Hz to 500MHz. The output noise is 34.86mV.With PAC gain of 51dB (363.584), the input referred noise is 0.096mV ~ 0.1mV.

相比于Transient noise,这种pnoise的方法一步就能得出input referred noise;所以也有paper专门对比过效率。

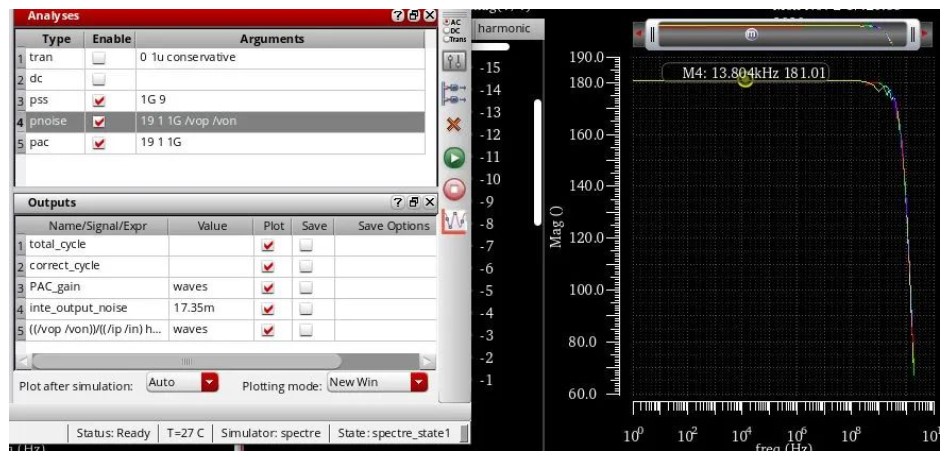

上面这张图是input差为0.1mV时候的仿真结果。作者君又勤快了点,多跑了一个仿真:

Input difference is 0.2mV.Pnoise integration is from 1Hz to 500MHz. The output noise is 17.35mV.With PAC gain of 45dB (181), the input referred noise is 0.096mV ~ 0.1mV.

当input差别变成0.2mV的时候,相对应的输出pnoise变小了差不多一半(34mV变成17mV),同样的,PAC得到的增益gain也减小了一半。因此,最后得到的input referred noise也基本上没变。

最后,对比一下transient noise 和Pnoise的结果,可以看到,我们拿到的input referred noise差不多都是0.1mV。哈哈哈,结果挺相符的,太棒了!(作者君这个comparator做得不错吧?加大input pair的size真的是挺有用的……就是面积有点大……囧)

PS:关于加的时钟频率比实际工作频率要高这点,作者君不是特别确定。希望读者们可以给出评论。谢谢大家!

在正常的用vpwl sweep comparator一端,固定另外一端的transient仿真时,比如工作频率是250MHz,可能出现因为时钟上升沿刚好没有对齐输入过零点导致的误差。这种情况下,加500MHz的时钟,可能会避免出现这种误差。

当clock是250MHz的时候,因为clock的rising edge没有对上,所以此时input的差是3mV,comparator对这个3mV的差做出了相应的切换。所以这个3mV主要是clock的edge造成的,noise的原因非常小。

当clock是500MHz的时候,因为clock的rising edge跟过零点非常接近,所以此时input的差是0.5mV,comparator对这个0.5mV的差做出了相应的切换。

审核编辑:刘清

-

电池电量的两种测试方法2010-01-16 4723

-

两种LED驱动模式的功能及使用方法2022-08-26 5233

-

Multisim仿真幅频特性曲线和相频特性曲线的两种方法2023-12-11 35064

-

详解ADC电路的静态仿真和动态仿真2025-06-05 2283

-

差模与共模两种噪声介绍2019-03-18 2366

-

两种传导噪声的对比了解2021-11-22 3396

-

Hopfield网络求解TSP两种改进算法的仿真研究2009-12-24 2114

-

匹配网络两种设计方法的对比研究2012-01-11 623

-

两种单相电路谐波及无功电流检测方法的详细比较资料说明2019-07-24 1280

-

PCI设备两种底层访问方法的实现及比较分析2020-10-04 4043

-

Comparator动态噪声的仿真2020-11-10 3660

-

浅析Comparator动态噪声的仿真2021-11-26 4069

-

浅谈VCS的两种仿真flow2023-01-10 6422

-

两种仿真软件的仿真结果有差异吗2023-12-28 2637

-

噪声传导的两种模式2024-10-15 1403

全部0条评论

快来发表一下你的评论吧 !