时序不满足的典型案例及解决方法

可编程逻辑

1395人已加入

描述

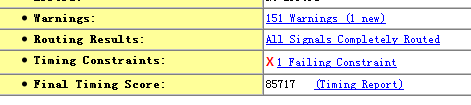

原先的时序报告:

根据时序报告中的路径提示,在ILA的某个路径上建立时间过长,而程序中并未例化ila的核,只是使用了chipscrop.。所以猜测是chipscrop部分的路径时序不收敛。

于是去除了名为AD9739_dds的chipscrop,发现时序就满足了。

证明时序是chipscrop中插入的ILA造成的时序问题。

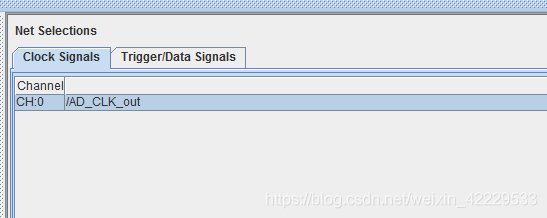

那么重新加入chipsrop,查看设置,发现他的采样时钟时AD_CLK_out,这个时钟是未经过IDEALY的。而所采集数据所用的fifo时钟是经过IDEALY的,这样,采集时钟就造成了时序的不匹配(主要是存在时间延迟)。于是时序不满足。

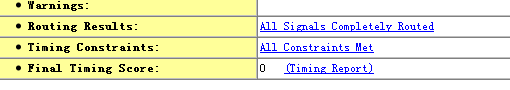

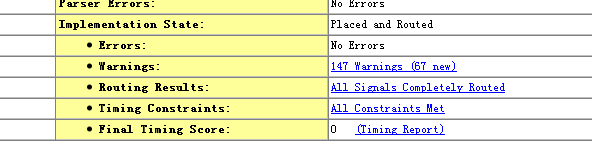

把这个时钟修改成经过IDEALY后的时钟查看时序报告。满足时序报告。

同理,不改动chipsrop的采样时钟,AD_CLK_out这个信号不经过ideay直接作为fifo的采样时钟一样可以满足时序。

审核编辑:彭静

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

在TC397的ASCLIN SPI Master Timing表格中,控制器所需要的最小setup time大于最小clock period,这是不满足时序要求的?2024-01-29 773

-

当运放用作比较器时,虚短特性是不满足的,为什么还会出现?2024-09-18 523

-

aic3106作为slave,sclk与Wclk是否可以不满足sclk=2*wclk*采样位数?2024-10-17 352

-

TUSB7340的GRST#信号时序在PERST#之后,不满足datasheet第104页Figure 23的时序要求,会有影响吗?2024-12-30 478

-

关于综合保持时间约束不满足的问题2025-10-24 152

-

有人能看看我这个运放为什么不满足虚短要求吗?2015-12-02 10396

-

条件结构中当满足条件时,数据可进入条件并输出,当不满足条件时,不想让数据进入,怎么实现?求大神指教。。。2016-03-22 4768

-

苹果的未来:不满足于做手机 还要布局智能家居2017-06-17 3379

-

sim800C gprs透传模式远程更新不满足条件2019-05-21 1210

-

ADS1232通道切换有什么好的解决方法吗?2019-05-28 2754

-

为什么条件不满足也进入了if循环?2019-11-11 5890

-

如果DFF的hold时间不满足怎么办2021-07-29 1271

-

AD9681输出赋值不满足LVDS电平要求怎么处理?2023-12-06 617

-

不满足于最好的Gear VR 三星将推出第一代AR眼镜2016-12-21 1188

-

REPEAT:不满足条件时执行2023-07-12 2583

全部0条评论

快来发表一下你的评论吧 !