关于奇数分频器

FPGA/ASIC技术

描述

因为偶数分频器过于简单,所以我们从奇数分频器开始说起8

01 奇数分频器假设我们要实现一个2N+1分频的分频器,就需要高电平占N+0.5个周期,低电平占N+0.5个周期,这样进行处理的最小时间段就变成了0.5个周期,就不能通过clk的计数直接实现了。

然而,时钟信号的上升沿和下降沿之间正好相差0.5个周期,利用这个就可以实现奇数分频啦

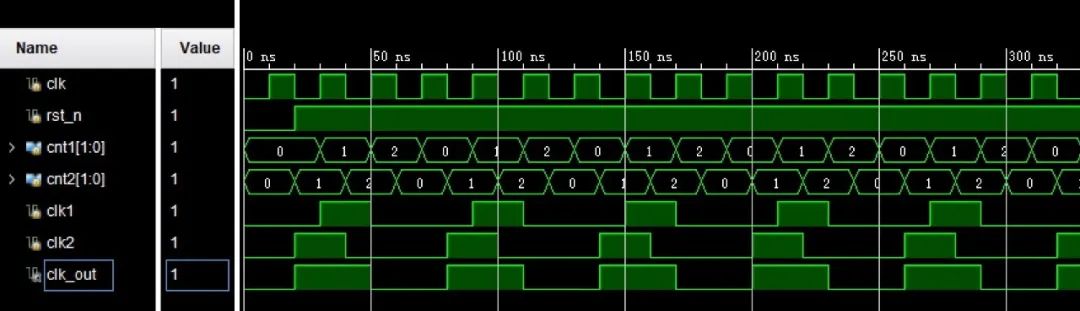

第一步:分别使用原时钟上升沿和下降沿产生两个计数器(基于上升沿计数的cnt1和基于下降沿计数的cnt2),计数器在计数到2N时,计数器归零重新从零开始计数,依次循环

第二步:cnt1计数到0和N时,clk1翻转,从而得到占空比为N:2N+1的clk1;

第三步:cnt2计数到0和N时,clk2翻转,从而得到占空比为N:2N+1的clk2;

第四步:clk1和clk2时钟进行或操作后,即可得到输出时钟clk_out;

下面为3分频的实现

module DIVCLK(

input wire clk,

input wire rst_n,

output wire clk_out

);

reg clk1;

reg clk2;

reg [1:0] cnt1;

reg [1:0] cnt2;

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

cnt1 <= 2'd0;

clk1 <= 1'b0;

end

else if (cnt1==2'd2) begin

cnt1 <= 2'd0;

end

else if ((cnt1==2'd0)||(cnt1==2'd1))begin

clk1 <= ~clk1;

cnt1=cnt1+2'd1;

end

else

cnt1=cnt1+2'd1;

end

always @(negedge clk or negedge rst_n) begin

if (!rst_n) begin

cnt2 <= 2'd0;

clk2 <= 1'b0;

end

else if (cnt2==2'd2) begin

cnt2 <= 2'd0;

end

else if ((cnt2==2'd0)||(cnt2==2'd1))begin

clk2 <= ~clk2;

cnt2=cnt2+2'd1;

end

else

cnt2=cnt2+2'd1;

end

assign clk_out=clk1|clk2;

endmodule

02 任意小数分频

在实际设计中,可能会需要小数分频的办法的到时钟,如在38.88M的SDH同步系统中,对应STM-1的开销的提取,需要2.048M的时钟,无法通过整数分频得到,只能用小数分频。

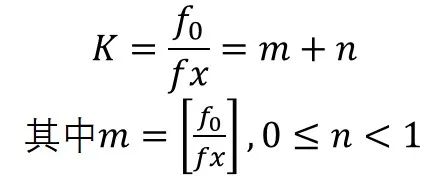

小数分频原理如下:设输入时钟频率f0,输出频率为fx,则

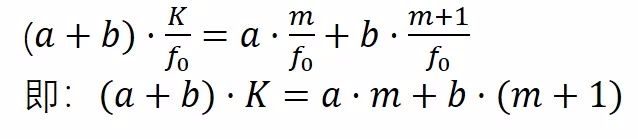

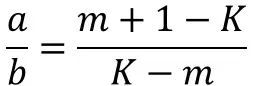

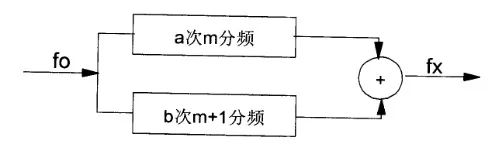

即m为整数部分,n为小数部分。为了实现K分频,可以对f0进行a次m分频和b次m+1分频,则有

整理后得

由38.88M得到2.048M的时钟,带入上式可得到m=18,a=1,b=63,即对38.88M进行1次18分频和63次19分频后间插就得到2.048MHz啦

审核编辑 :李倩

-

FPGA学习-分频器设计2023-11-03 3225

-

基于Verilog的分数分频电路设计2023-04-25 2556

-

偶数分频、奇数分频、半整数分频和小数分频详解2023-03-29 6702

-

偶数分频器的设计2023-03-23 2928

-

基于CPLD/FPGA的半整数分频器设计方案2021-06-17 1006

-

奇数分频器的介绍和实现2021-03-12 7111

-

奇数分频如何得到呢? 解读奇数分频和逻辑分析仪(ILA)的使用2020-12-28 3476

-

分频器的作用是什么 半整数分频器原理图分析2019-02-01 18549

-

用Verilog实现基于FPGA的通用分频器的设计2016-07-14 1179

-

需要讲解一个占空比50%的奇数分频器的原理2013-10-04 11688

-

FPGA实现小数分频器2011-11-29 817

-

基于FPGA的任意数值分频器的设计2010-04-26 2820

-

任意分频系数小数分频器相关文档及源代码2009-08-03 693

全部0条评论

快来发表一下你的评论吧 !