为高速SPI通信添加稳健可靠的隔离

今日头条

描述

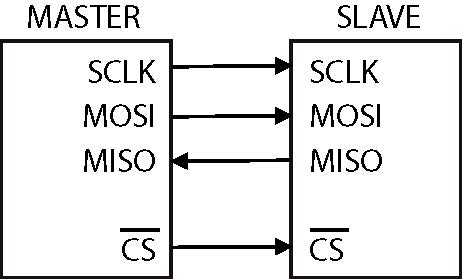

串行外设接口 (SPI) 是一种设备间总线协议,可在主设备和多个从设备之一之间提供快速、同步和全双工通信。主设备(例如 MCU 或 FPGA)驱动时钟并选择从设备(例如 ADC 或数字输出驱动器)进行寻址。

每个 SPI 设备都包含一个移位寄存器和控制电路,因此所选设备可以同时发送和接收信号。SPI通信中使用了四种信号,如图1所示:

• SCLK: 所有设备使用的同步时钟。主机驱动这个时钟,从机接收它。请注意,SCLK 可以被门控,不需要在 SPI 事务之间驱动。

• MOSI: 主输出,从属输入。也称为主站上的 DO 或从站上的 DI。这是主机驱动到 SPI 总线上所有从机的主要数据线。只有选定的从机时钟来自 MOSI 的数据。

• MISO: 主输入,从输出。在主设备上也称为 DI,在从设备上也称为 DO。这是由所选从设备驱动到主设备的主数据线。只有选定的从机可以驱动该信号。

• CS: 片选。该信号对每个从站都是唯一的。激活时(通常为低电平),所选从机必须根据 SCLK 转换驱动 MISO。

图 1:主从 SPI 连接。

隔离设计挑战

对于许多工业控制应用,数字处理器内核 (MCU) 和 I/O 模块设备之间的通信路径必须隔离。隔离有助于最大限度地减少噪声和接地回路问题。此外,它还为昂贵的控制单元(如 MCU 和 FPGA)提供保护。

传统的信号隔离方法是使用光耦合器。然而,一些缺点使光耦合器不适用于现代高速 SPI 数据传输应用。光耦合器体积庞大,会引入较长的传播延迟,并导致高功耗。因此,更小的 CMOS 电容数字隔离芯片现在已经取代了光耦合器。

然而,使用数字隔离器本身并不是灵丹妙药。为了使数字隔离器有效地用于高速 SPI 通信,它们必须满足几个具有挑战性的电压和时序参数。

通常,隔离器的模拟域和数字域中的电压处于不同的水平。因此,要使隔离器有效,它必须能够在模拟和数字域中的宽电压范围内工作。

此外,由于 SPI 是事实上的 标准而不是正式的标准,因此没有明确定义的时钟频率。尽管许多传统设备可能使用 5–10 MHz 范围内的时钟频率,但较新的设备具有更快的数据传输要求,使用 50 和 75 MHz 之间的时钟频率。有效的隔离器必须能够在如此宽的 SPI 频率范围内工作。

通过在主设备和从设备之间放置一个数字隔离器,会为 SPI 总线创建额外的信号延迟。主机使用时钟上升沿发送数据,下降沿采样从机发回的数据。

因此系统设计人员需要检查时序预算,以确保隔离器传播延迟不违反主控对采样 MISO 的时序要求。否则,主设备将失去同步或在接收和发送的数据中引入错误,如图2所示。

图 2:由于隔离器延迟导致的时序失配。

单个数字隔离器部件可能包含多个隔离通道——通常在 1 到 4 个之间。因此,隔离器通道之间的延迟匹配至关重要。否则,可能会引入传播延迟偏斜。因此,在例如时钟通过隔离器的一个通道传输而数据通过另一个通道传输的情况下,这一点至关重要。

最后,在电路中添加数字隔离器将不可避免地导致电流消耗增加。有效的隔离器不应过多地增加功率预算,以避免在小型外壳中散热。

解决电压和时序问题

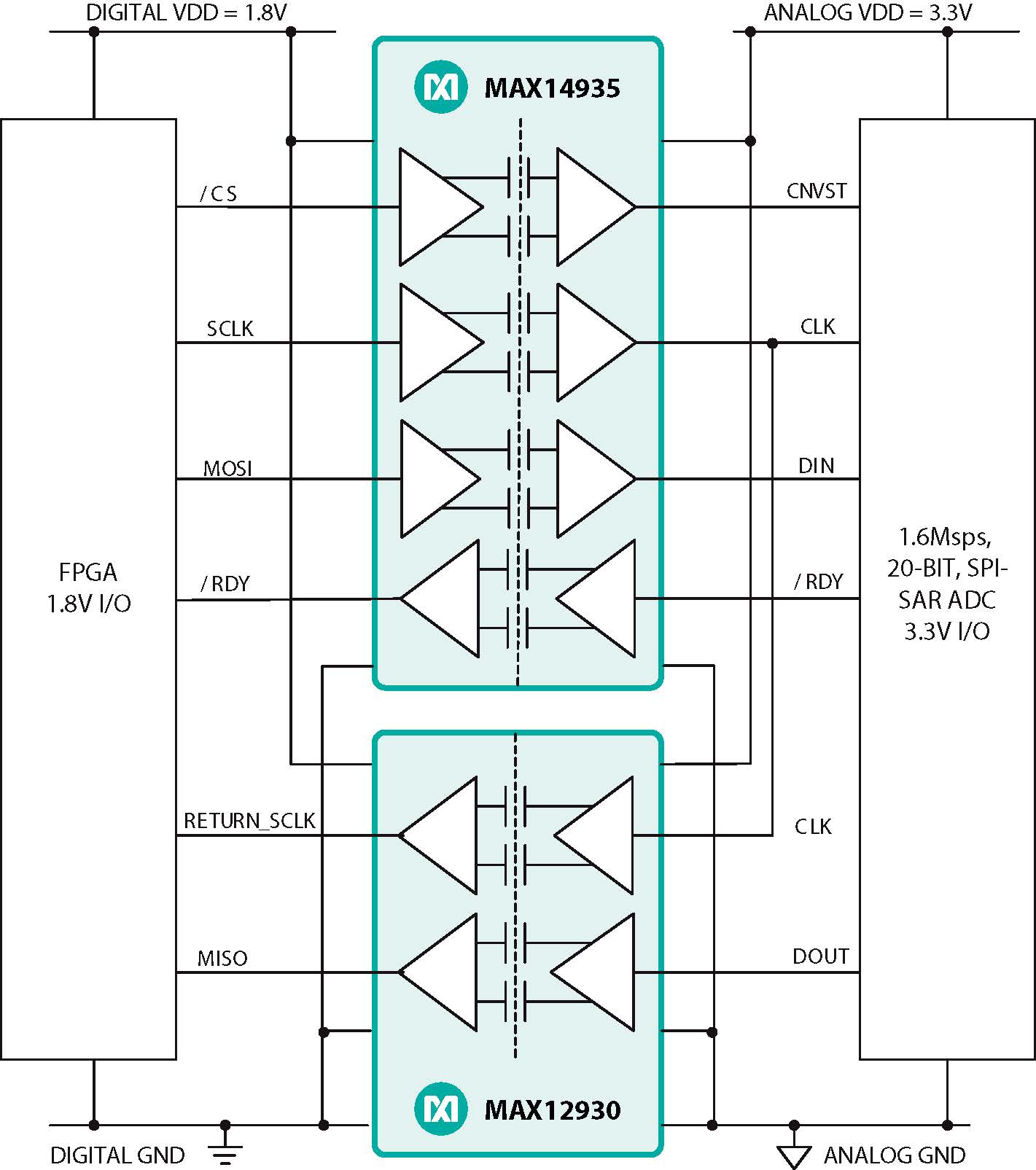

以 FPGA 和 ADC 之间的典型隔离高速 SPI 通信电路为例,如图 3 所示。ADC 使用两个数字隔离器与 FPGA 隔离。SCLK 将来自 FPGA 的数据 (MOSI) 提供给 ADC。在 ADC 的输入端,隔离 SCLK 表示为 CLK,隔离 MOSI 表示为 DIN。

图 3:典型的高速 SPI 隔离电路。

在低速 SPI 通信期间,主时钟还用于为反向传输的数据 (MISO) 提供时钟。为了补偿主时钟 (SCLK) 已经被正向隔离延迟的事实,当从 ADC 到 FPGA 的反向时钟数据时,会返回 CLK 的副本(隔离的 SCLK) . 它确保 CLK 和 DOUT 的时序在它们被隔离并分别作为 RETURN_SCLK 和 MISO 到达 FPGA 时仍然同步。

因此,要使这种安排成功,必须不仅具有低隔离器传播延迟和低通道间偏移,而且还具有低部件间偏移。因此,CMOS 数字隔离器应专门设计为满足这些要求,并确保电路布置能够成功实现,以在高速 SPI 通信中提供隔离(图 4)。

图 4:时钟返回主机的时序。

图 3所示的 MAX14934/35/36 和 MAX12930/31 系列数字隔离器 基于 Maxim 专有的电容隔离技术。它们提供高隔离电压保护(高达 5 kV rms),同时还支持高达 150 Mbps 的数据速率。这些器件在宽电源电压范围(1.71 V 至 5.5 V)内工作,典型传播延迟为 5 ns(最大值为 7.5 ns)。

1 ns 的最大脉冲宽度失真——加上 0.9 ns 的最大通道间偏移和 3 ns 的最大部件间偏移——确保在高速 SPI 通信电路中可靠运行。此外,通过提供四通道 (MAX14934/35/36) 和双通道 (MAX12930/31) 选项,这些数字隔离器还可用于可编程逻辑控制器 (PLC)、电信和医疗仪器应用。

审核编辑:汤梓红

-

SiLM5742CG-DG 100Mbps5.0kVRMS高速四通道数字隔离器2026-04-14 36

-

AEK-COM-ISOSPI1技术解析:SPI隔离通信在汽车电子中的应用2025-10-24 968

-

基于STEVAL-BMS1T的隔离式SPI通信技术解析与应用指南2025-10-16 799

-

基于STM32的SPI通信2023-06-21 3962

-

适用于可靠且稳健的工业高速链路的信号调节器2023-02-01 8076

-

为您的高速SPI添加强大和可靠的隔离交流2022-12-07 2382

-

STM32 SPI通信高速全双工的通信介绍2022-02-14 1354

-

SPI通信2021-12-22 860

-

请问隔离式SPI通信怎么实现?2021-03-18 1603

-

如何实现隔离式SPI通信2021-01-21 1200

-

隔离式SPI通信如何去实现2020-03-13 3909

-

在SPI总线中常用的6N137和ADuM315x两款隔离芯片分析2017-08-25 25238

-

用SPI总线实现DSP和MCU之间的高速通信2009-11-27 1033

全部0条评论

快来发表一下你的评论吧 !