通过硬件仿真将DFT转移到芯片设计中

今日头条

描述

在市场上所有的电子设计自动化 (EDA) 工具中,可测试设计 (DFT) 可能是最不被重视的。即使在设计阶段将可测试性构建到芯片中也会显着降低高昂的测试成本。根据最近的分析,在制造后测试一批芯片以确定哪些部件没有制造缺陷的成本已达到制造芯片成本的 40% 的惊人阈值。

DFT 可以消除通过问题设备的风险,该设备最终将在现场以比在制造车间发现的成本高得多的成本被捕获。它还可以避免拒绝无故障设备,从而提高良率。插入 DFT 还减少了与测试开发相关的时间,以及测试制造芯片的执行时间。

DFT 是电子行业的流行语,与自动测试模式生成器 (ATPG) 和内存内置自测 (MBIST) 相结合,是插入片上测试基础设施,例如扫描链、MBIST 结构或压缩/解压缩逻辑。扫描链通过串行移位寄存器增加了可控性和可观察性。使用扫描链,测试电路的问题被简化并简化为测试寄存器之间的组合逻辑。通过 ATPG 工具自动生成测试模式的能力可以减轻创建测试向量的耗时和烦人的任务。

在设计经过功能验证后,片上测试基础设施或扫描链被插入到门级网表中,并且必须谨慎行事,因为它可能会干扰芯片的功能正确性。设计更改需要门级验证,以确保设计完整性没有受到损害。测试由长序列的测试模式执行,这是一项计算密集型任务,比寄存器传输级别 (RTL) 验证要繁琐得多。

值得一提的是,从设计的角度来看,DFT 结构的创建和插入相当简单。然而,从密度和尺寸的角度来看,设计变得相当大,并且测试设计所需的测试模式量显着增加了尺寸。

DFT 验证

当设计规模达到数亿门时,基于模拟器的验证对于门级检查来说太慢了。DFT 方法只会让事情变得更糟。如果这还不够负担,那么优先访问接近流片的模拟农场有利于设计工程师,而与测试工程师竞争。芯片通常以最少的 DFT 验证流片,并且在流片后执行彻底的 DFT 测试,为时已晚,无法修复设计错误。

DFT 验证有多种形式,包括需要验证的自定义初始化模式。它可以是由自动测试模式生成工具插入的片上时钟控制器,需要在模式执行期间进行动态验证,或者是为 MBIST 添加的逻辑,需要对与测试模式相关的逻辑进行功能验证。SoC 可以包括自定义初始化模式,该模式配置测试并导致从功能模式到测试模式的转换。其他测试模式可能具有低功耗技术,在测试期间将部分芯片置于低功耗模式,这需要在适当的条件下验证测试基础设施。

使用 DFT 应用程序进行硬件仿真

硬件加速加速了进行彻底 DFT 验证所需的仿真周期。它可以验证芯片的功能,无论其大小和复杂性如何。

虽然硬件仿真已经使用了 30 年,通过部署可重新编程的硬件来增加验证周期,但新的部署模式使其成为一种更加可行的验证工具,并为“应用程序”方法铺平了道路。对于那些使用更困难的基于模拟器的验证方法的芯片设计团队来说,最近发布的一些用于硬件仿真的应用程序可能是受欢迎的消息。DFT 应用程序加快了需要全面门级仿真的芯片设计进度。利用自动生成的模式,设计团队可以缩短整个模式的开发周期。

这种类型的硬件仿真的可扩展硬件和编译器能够对大型门级设计进行测试模式验证,并将扫描和其他测试结构嵌入到设计中。其高性能可实现更多仿真周期,加速 DFT 分析。DFT 应用程序可与其他工具互操作,因为它支持生产测试仪上使用的行业标准 STIL 格式文件,以识别制造过程中损坏的芯片。

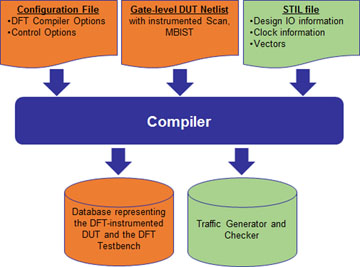

用于硬件仿真的 DFT 应用程序改变了硬件仿真器部署过程中的编译流程和运行时执行。这些是编译流程和运行时执行的变化。带有扫描和 MBIST 的门级设计被输入硬件仿真的编译器。编译器创建必要的测试基础设施,用于从 STIL 文件中读取测试向量,将它们应用到合成的被测设备 (DUT) 并比较输出。编译器将用户网表重新编译并综合成与硬件仿真兼容的结构描述。在编译时,仿真器创建必要的基础设施,用于从 STIL 文件中读取测试向量并将它们应用到合成的 DUT,然后重新编译并将网表合成为与仿真兼容的结构描述。测试工具包括一个比较输出的机制。见图#1。

图 1:DFT 应用修改后的编译流程。

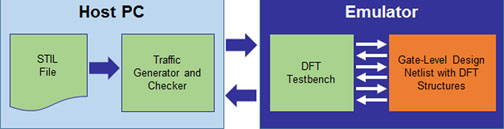

调用时,设计和测试平台被映射到仿真器中。在运行时,硬件仿真从 STIL 文件中提取测试向量,将它们应用到 DUT,并比较输出——所有这些都以仿真速度进行。见图#2。

图 2:运行时图显示了主机 PC 和仿真器中的操作分解。

DFT 应用程序支持执行完整的模式集以进行 DFT 验证,以缩短模式开发周期。一个可扩展的仿真平台可以容纳多达数十亿个门的设计,以及一个可以支持 DFT 方法的编译器,可以对嵌入了扫描和其他测试结构的大型门级设计进行测试模式验证。

一旦芯片制造完成,相同的 STIL 文件就可以在测试台上使用。加载到 ATE 中,测试向量运行芯片并将其响应与 STIL 文件中的预期值进行比较。

测试设计

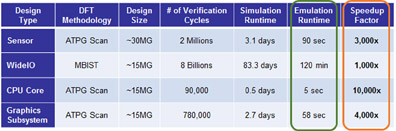

硬件仿真不会以比仿真更快的速度进行仿真——它要快几个数量级。在硬件仿真上运行 DFT 模式时,一些基准测试显示了四到五个数量级的改进。见表#1。

表 1:DFT 应用基准的比较显示了性能改进。

通过将模拟器上通常需要三个月的测试时间减少到两个小时,硬件仿真允许在芯片流片之前对测试向量和 DFT 逻辑进行完整验证。为硬件仿真提供 DFT 应用程序可拓宽使用模型、提高性能并帮助验证工程师规避风险。DFT 工程师现在有一种方法可以利用硬件仿真的强大功能来确保芯片适合使用“应用程序”进行制造。

审核编辑:汤梓红

-

CSP LED切割前如何转移到UV膜上2024-10-29 3936

-

如何用加载分散法将软件中部分变量从内部RAM转移到外部RAM?2024-05-10 474

-

通过转移到SiC技术来获得暖通空调更佳的SEER等级2023-11-28 1520

-

嵌入式开发中,如何将Flash中的程序转移到RAM中运行?2023-10-29 5666

-

如何将pin从arduino转移到esp32?2023-04-12 534

-

ch579例程里使用的是Keil编译,转移到MounRiver是有什么要配置的吗?2022-09-02 964

-

STM32是如何从TRUEStudio转移到STM32CubeIDE上的呢2022-02-17 1094

-

苹果准备将 10% 的 iPhone 12 生产从中国转移到印度2021-03-09 4058

-

亚马逊将Alexa语音助手的部分计算任务转移到自主设计的芯片上2020-11-19 2740

-

如何将旧的ISE设计转移到Vivado 2014.12020-05-29 3451

-

华为内部设计芯片生产工作正逐步转移到中芯国际 资源将向中芯国际倾斜2020-04-17 3684

-

cyclone3工程转移到cyclone42019-04-11 4115

-

vDGA转移到vGPU2018-09-07 4146

-

APD 14.2 wirebond的档案转移到15版2009-09-06 1428

全部0条评论

快来发表一下你的评论吧 !