关联USB Type-C参考通道的仿真和测量(二)

今日头条

描述

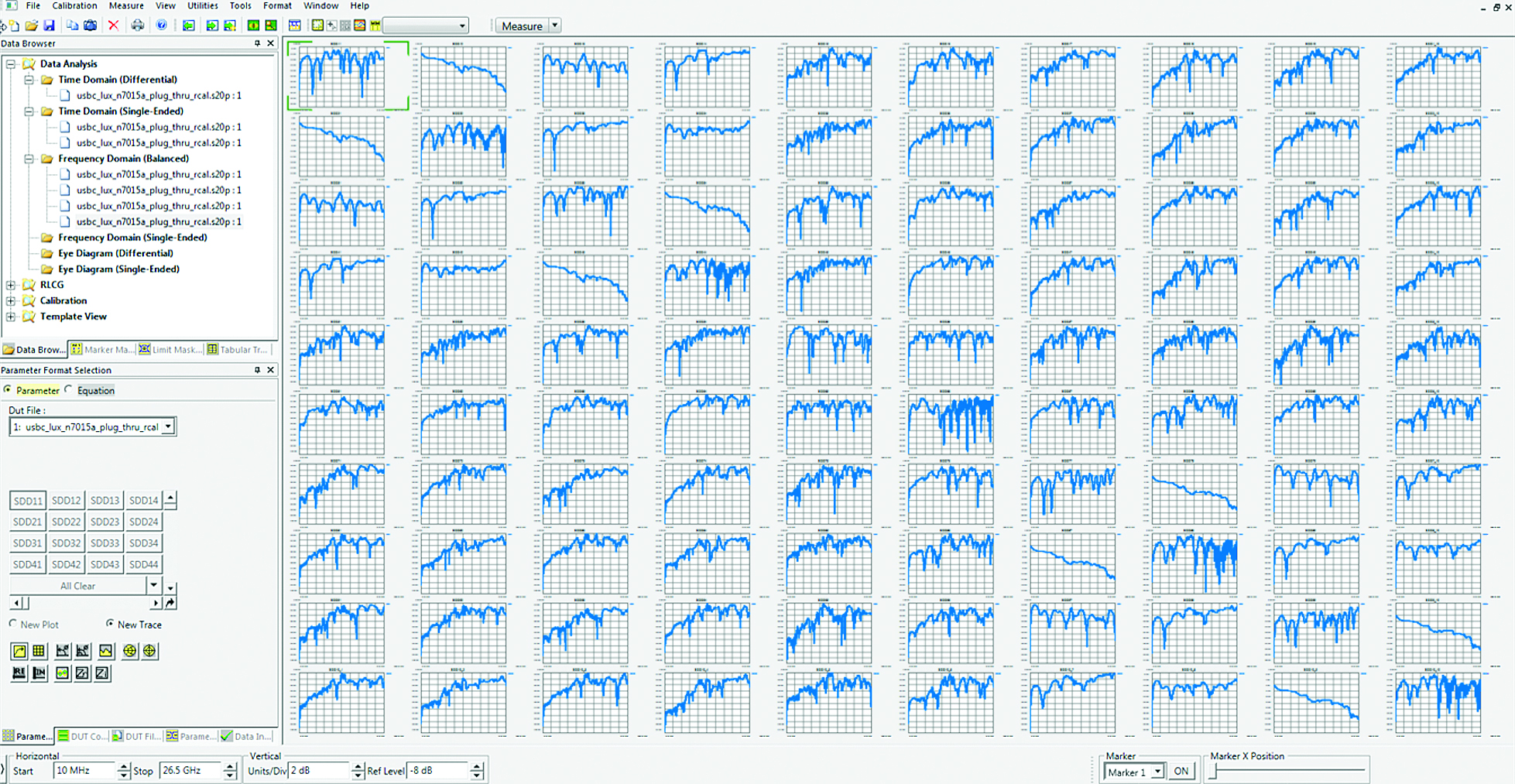

在本文的第 1 部分中,我们了解了微分 S 参数背后的基本思想。现在我们可以开始探索多通道 Touchstone 文件中的大量信息(图 1)。虽然起初看起来很复杂,但有一些基本的分析方法可以一次又一次地完成,并取得非常成功的结果。我们现在将讨论其中一些分析技巧和技术,这些技巧和技术可以帮助您以最快的方式深入了解设备性能。

图 1:在 20 端口 .s20p Touchstone 文件的左上象限中,可以一次查看 400 个 S 参数或一次查看多个图。

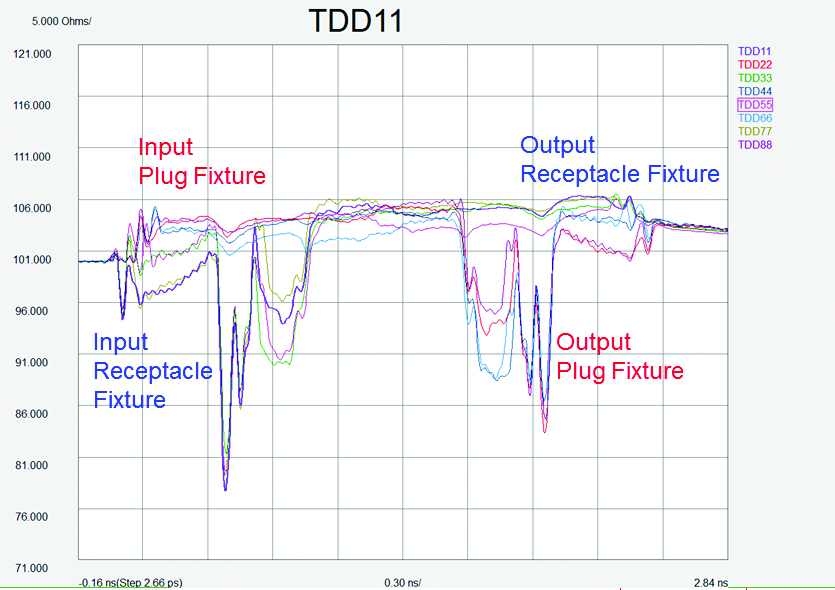

对称是一件美妙的事情 分析大型多通道 S 参数文件的第一步是使用时域。VNA S 参数测量可以使用逆快速傅里叶 (IFFT) 函数进行修改,以提取 TDD11 时域参数,这是描述为电阻与时间的阻抗曲线,时间表示距离(信号传播所需的时间)并反映电阻变化或不连续性)。

为什么这比使用 SDD11 频域数据更受欢迎?因为频域不提供任何空间信息。在时域中,可以快速定位不良电缆、开路、短路和其他异常的位置。绘制所有差分通道的差分阻抗曲线是在保存数据之前对测量设置进行此类“健全性检查”的一种快速方法。

所有差分通道的图(图 2)显示了所有正向和反向阻抗分布波形之间的美丽对称。应该有大量镜像波形,因为我们已经自动测量了每个通道的正向和反向。这是拥有高端口数仪器的好处。

图 2:所有差分通道的图显示了所有正向和反向阻抗曲线波形之间的美丽对称。

右上角的波形图例表明我们绘制了 TDD11 到 TDD88。TDD11 是与 TDD22 完全相同的通道的正向差分阻抗分布,除了 TDD22 只是反向差分阻抗分布。所以这两个测量图应该是对称的,而且它们是对称的。其余的地块对也是如此。

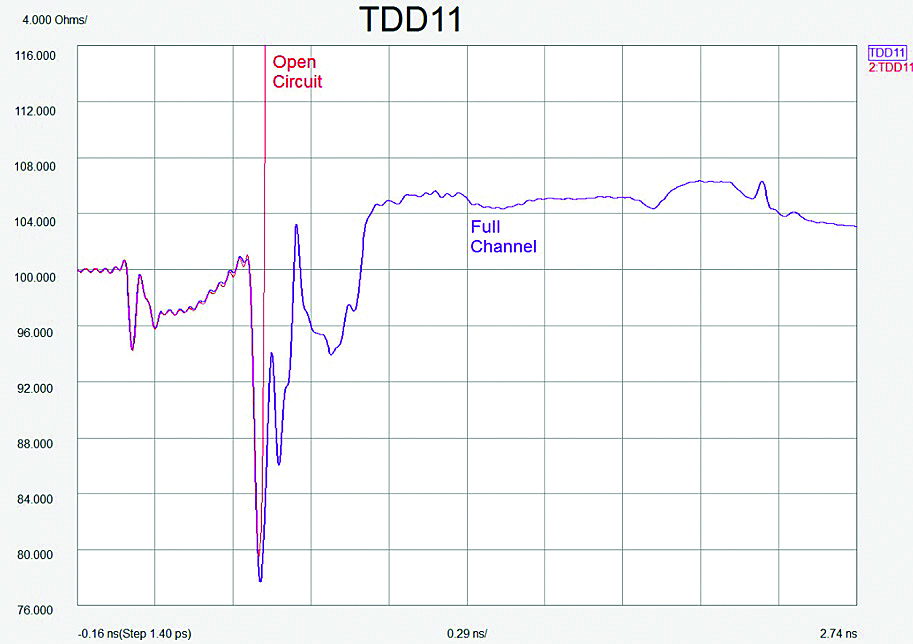

正向和反向通道阻抗曲线 分析数据通道的下一步是在空间上将 USB Type-C 连接器定位在中间。(我们知道它在靠近中间的某个地方,但确实需要确切的位置。)为此,我们再次查看时域数据,并在物理断开两个灯具后简单地测量通道。当我们断开两个夹具时,我们将看到一个夹具的阻抗曲线终止于开路。这在连接器所在的时间位置用一条直线上升到无穷大阻抗的尖锐垂直线表示(图 3)。

图 3:垂直的红线表示在夹具断开时的开路。这可以深入了解每个夹具的结束和开始位置。

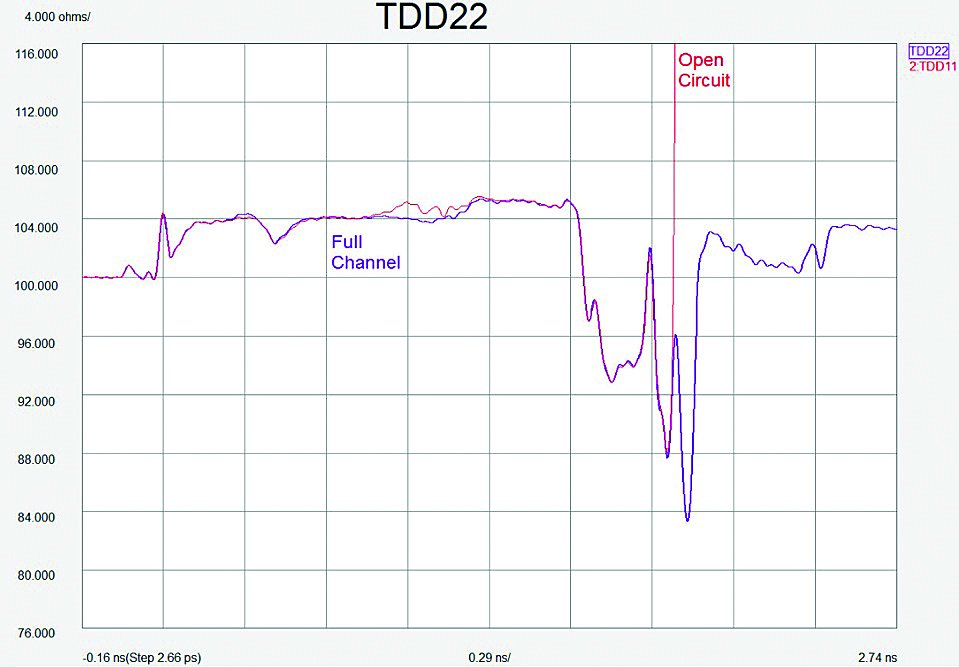

为了验证和仔细检查我们的工作,我们将查看断开夹具的相同阻抗分布,但现在从另一个方向查看(图 4)。正如我们之前提到的,TDD22 只是 TDD11 通道的反向阻抗曲线。我们看到相同的垂直红线准确地指示了一个夹具的结束位置和另一个夹具的开始位置。在查看最后两个 TDD11 和 TDD22 波形时,很明显这两个灯具彼此完全不同。

图 4:将此图与图 3 进行比较,可以看出灯具之间的差异。

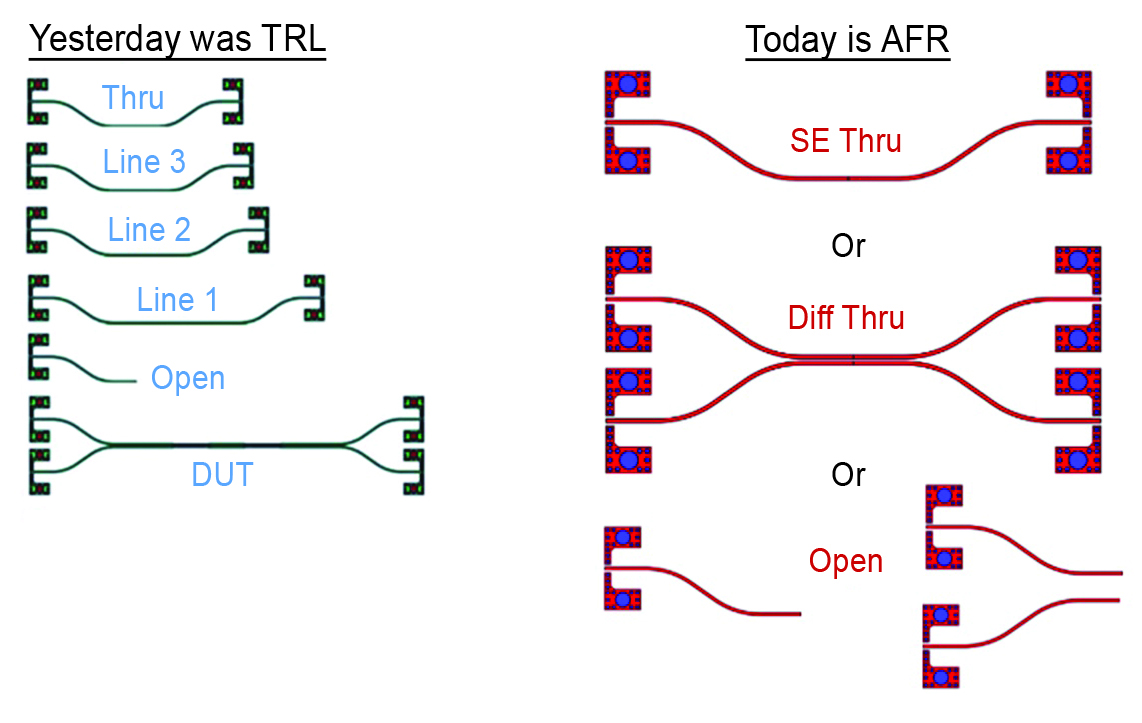

测量通道 从历史上看,通常有两种方法用于从被测设备或 DUT 中消除测量夹具的影响(图 5)。

图 5:要准确测量被测设备 (DUT),必须首先消除夹具的影响。

第一种方法是使用电磁模拟器对夹具进行建模,并使用仿真的 S 参数结果来反嵌夹具的影响。为夹具创建准确的模型可能需要一些时间。第二种技术是在用于制造夹具的同一 PCB 上建立校准标准。

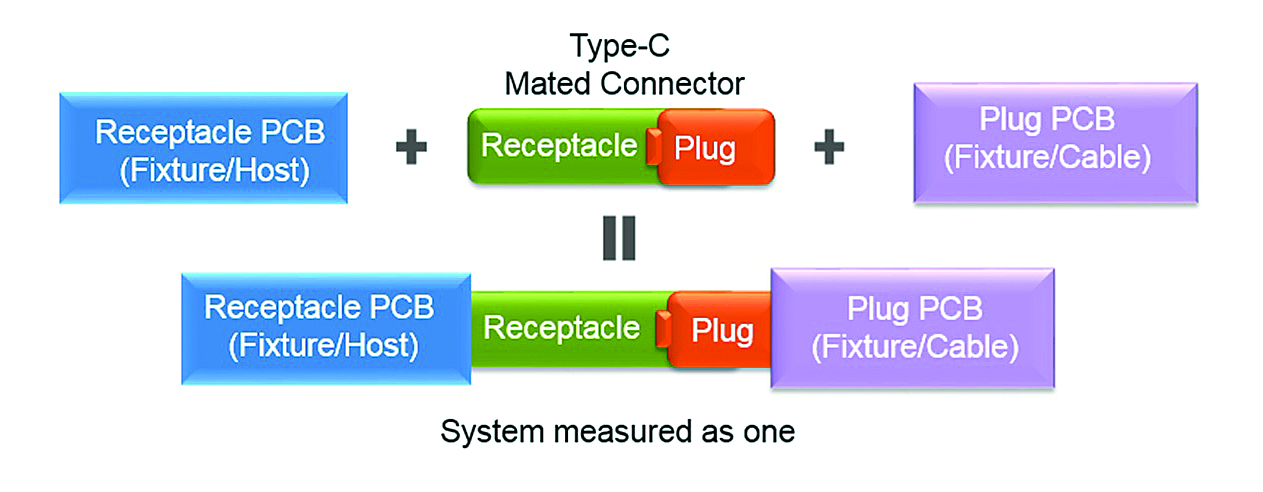

这些传统的校准方法将参考平面放置在夹具 PCB 上可以放置定制标准的位置。像 TRL 这样的校准标准需要在参考平面上使用 TEM 模式;也就是说,机械结构在参考平面上镜像。此类校准的最终结果通常将匹配的连接器性能作为 DUT 的一部分,例如 USB 主机、电缆或设备。可以将夹具从全路径测量中移除,以获得包含配对连接器性能的 DUT 的 S 参数(图 6)。这通常是需要的,因为渠道中这些不同组件的供应商需要证明他们的产品可以与配对的连接器一起使用。

图 6:虽然可以从全路径测量中移除夹具以获得包含配对连接器性能的 DUT 的 S 参数,但哪种类型的校准会将参考平面放置在配对连接器的中间以提供正确的通道延迟?

但是,虽然在 DUT 中包含配对连接器非常适合表征和比较通道中不同组件的性能,但在仿真中将组件级联在一起以与测量的全路径性能进行比较时会带来挑战。对于观察者来说,很明显应该在配合面上拆分配合的连接器,只留下插头或插座作为 DUT 的一部分。困难的问题是,什么类型的校准会将参考平面放置在配对连接器的中间?

自动夹具移除 几年前推出的一种相对较新的技术,称为自动夹具移除 (AFR),只需要一个校准标准,而不是 TRL 所需的多个标准。该标准可以是通过路径的背靠背 2x 夹具,或者在某些情况下,只是一个开放的 1x 夹具结构。直通只是没有 DUT 连接的左半边和右半边夹具。这里最大的假设是通过必须是对称的。在 USB Type-C 连接器的情况下,很难创建背靠背直通路径,因为一个插座不能与另一个插座配合。

图 7:比较传统的 TRL 校准结构(左)和 AFR 技术使用的校准结构(右),AFR 应用第二层 AFR 校准将测量参考平面移动到最终位置。

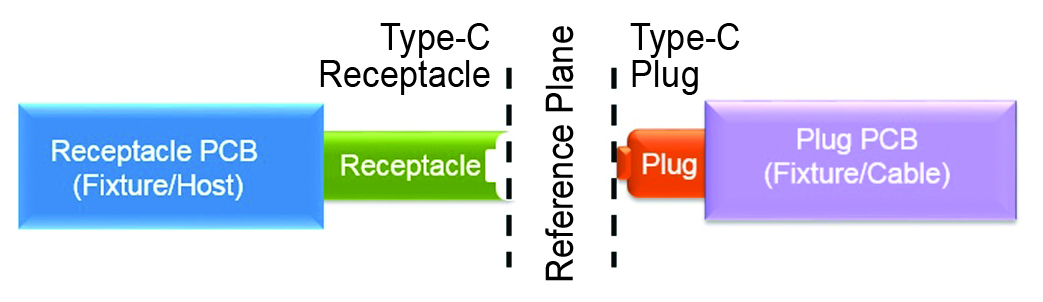

1-Port AFR 技术的优势在于它能够自动将参考平面放置在 Type-C 插头和插座的所需配合表面(图 8)。这会导致主机、电缆或设备的 S 参数行为模型可以级联到仿真中,从而通过精确的电延迟改善仿真与测量的相关性。

图 8:1 端口 AFR 技术自动将参考平面放置在 Type-C 插头和插座的配合面上。

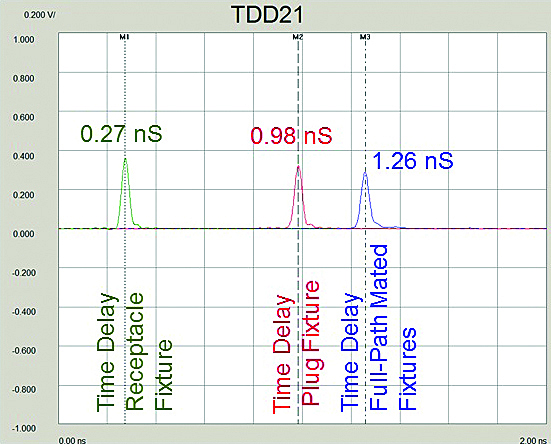

每个组件的电延迟可以通过频域中的群延迟或时域中脉冲响应峰值的到达来测量(图 9)。插头夹具时间延迟和插座夹具时间延迟的 1 端口 AFR 测量值加起来是两个插在一起的夹具的测量全路径时间延迟。

图 9:插头夹具时间延迟和插座夹具时间延迟的 1 端口 AFR 测量加起来是两个插在一起的夹具测量的全路径时间延迟。

审核编辑:汤梓红

-

如何关联USB Type-C仿真和测量-应用笔记2018-09-20 1850

-

USB Type-C设计细节2019-07-16 5470

-

usb-c和type-c的区别比较2017-12-14 211964

-

USB Type-C接口资料合集免费下载2018-11-26 5251

-

TI关于USB 3.2 Type-C的解决方案(2)2019-04-24 5228

-

USB Type-C型电源的特点优势及应用介绍(2)2019-04-03 3457

-

USB Type-C拓展坞方案特点及相关信息2019-10-16 13763

-

USB Type-C 多路复用USB 3.1 应用2022-07-27 7407

-

USB Type-C设计日记2022-08-12 1491

-

关联USB Type-C参考通道的仿真和测量(一)2022-08-22 2533

-

USB Type-C拓展坞方案简介2022-09-05 8690

-

usb-c和type-c的区别,usb-c和type-c可以混用吗2023-07-19 54819

-

type-c和USB-c有什么区别 type-c和USB-c接口原理2023-09-01 38306

-

USB Type-C直角型线缆的6个优势2023-11-27 1370

-

usb-c和type-c的区别2023-12-08 15872

全部0条评论

快来发表一下你的评论吧 !