ZVS振荡器的工作原理及参数设计

电子说

描述

简 介:本文基于 LTspice 仿真,分析了 ZVS 振荡器的工作原理以及相关的参数设计。

01 ZVS工作原理

一、背景介绍

零电压开关(Zero三 Voltage Switch)振荡电路是功率开关管在导通和关断(模式切换时)两端电压为0(实际上应该是非常接近于0)的电路,这种特性使得电路功率损耗变小,所以被广泛 应用到大功率加热、高压电路中。比如在一些LLC 电源, 电磁炉驱动电路中。

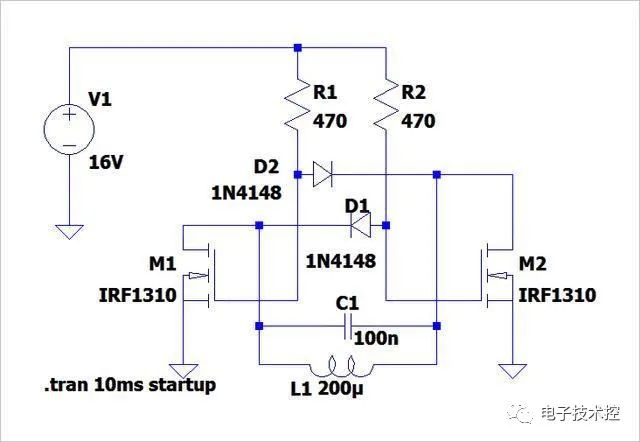

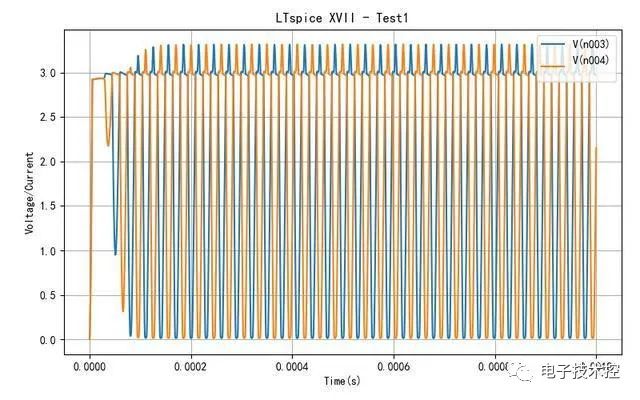

下面借助于 LTspice 仿真软件对 ZVS 的工作原理进行介绍。请大家注意,一开始在LTspice搭建ZVS振荡器仿真[1]电路,电路并没有起振工作,经过调整仿真瞬态参数,设定仿真电路电源是从 0V 开始工作,这样电路便可以正常工作了。

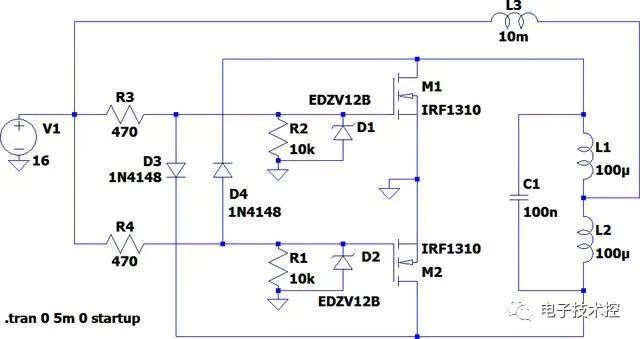

▲ 图1.1.1 ZVS LTspice 仿真电路

1、需要回答的问题

初次接触到 ZVS 的人对于这个电路形式可能会询问一下几个基本问题:

这个电路是如何振荡的?

电路器件参数是如何影响电路工作特性的?

电路中主要器件设计依据是什么?

二、电路振荡原理

1、多谐振荡器

相比于常见到的多谐振荡电路[2],ZVS电路结构也呈现鲜明的对称性,但其中元器件更多,而且还有 谐振回路,ZVS电路工作原理则显得更加的扑朔迷离。

下面给出多谐振荡电路的基本电路原理图,如果你对于该电路工作原理比较熟悉,这也可以帮助你了解 ZVS 电路振荡原理。

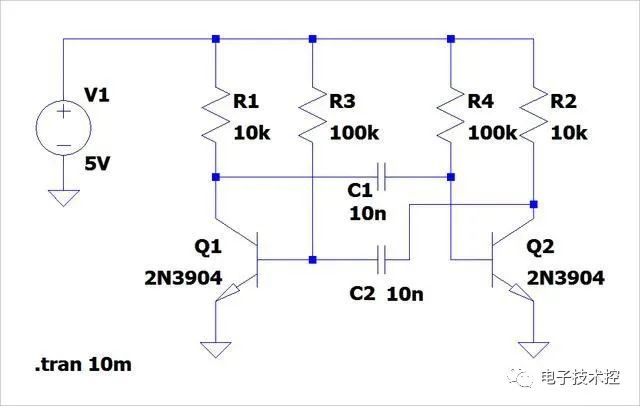

▲ 图1.2.1 多谐振荡器原理图

这类无稳态多谐振荡电路实际上是将两级反向放大电路串联成回路,信号经过回路形成正反馈从而使得电路中的三极管在两个状态(导通、截止)之间反转。下图给出了 LTspice 仿真后, Q1 的集电极和基极电压波形。

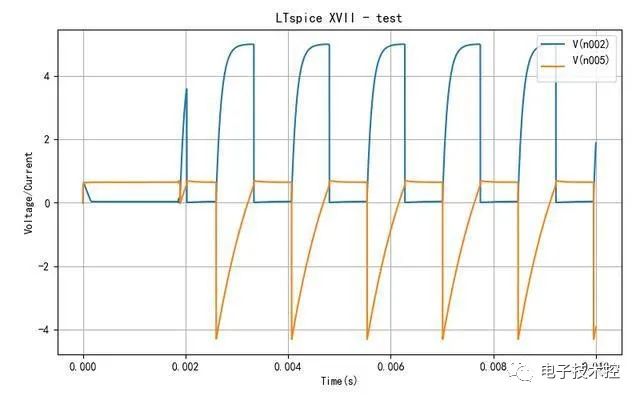

▲ 图1.2.2 多谐振荡器Q1的集电极和基极电压波形

2、二极管耦合电路

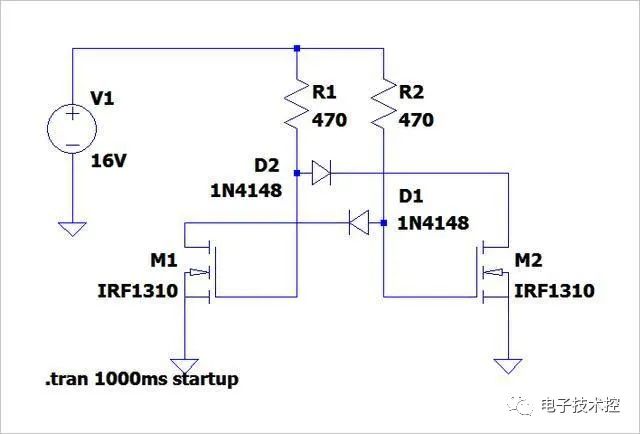

观察 ZVS 电路,可以看到原来的两个耦合从美容 C1,C2 现在变成了二极管 D1,D2。下面给出了 ZVS 电路中最核心的六个器件组成的反向耦合电路。这个电路具有三个特殊的平衡状态。

平衡态1:M1截止,M2导通:这是一个稳态。 M1截止,使得 D1不导通。因此 R2 将电源施加在 M2 的栅极维持 M2 的导通;M2导通之后, D2 通过 M2 把 M1 的栅极接地,从而使得 M1继续截止。

平衡态2:M1导通,M2截止:这是一个稳态。分析的方法与上面稳态相同。

平衡态3:M1,M2处在放大状态:这是一个不稳定的平衡态。

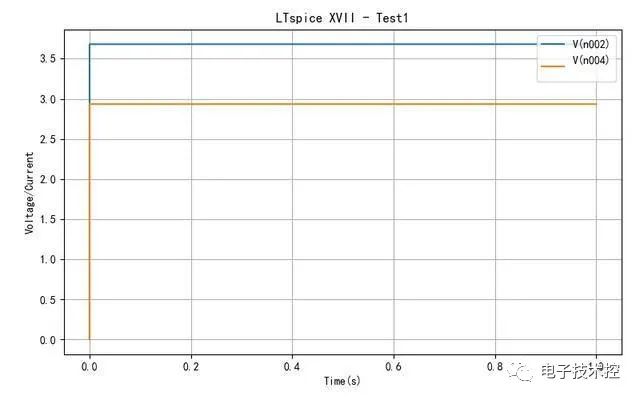

▲ 图1.2.3 ZVS电路中的核心器件

在 LTspice 中,通过仿真可以计算出 M1,M2放大状态时, M1,M2 对应的漏极和栅极电压。下图给出了 M1 的栅极电压(Vn002)以及漏极(Vn004)。电源通过 R1,R2 给 M1、M2 的栅极提供偏置电压,这个电压又通过 D1,D2 连接到 M2,M1的漏极。所以 M1,M2 的漏极比栅极电压低了一个二极管的导通电压(大约 0.7V)。

▲ 图1.2.4 LTspice 对M1,M2放大状态的仿真结果

上面仿真验证了 M1、M2 都处在对称放大状态的存在,但这个状态属于不稳定状态, 一点点的扰动可能使得电路变换到平衡态 1 或者平衡态 2。这是因为:

两个 MOS 管组成的放大电路,形成正反馈

每一级 MOS 的放大电路的增益在平衡态时增益大于1;

3、MOS单管放大电路

为了验证上面基本电路中 MOS 管处在放大状态下的增益大于1, 下面对 MOS 管电路放大特性进行仿真求解。

(1)MOS管单管跨导放大特性

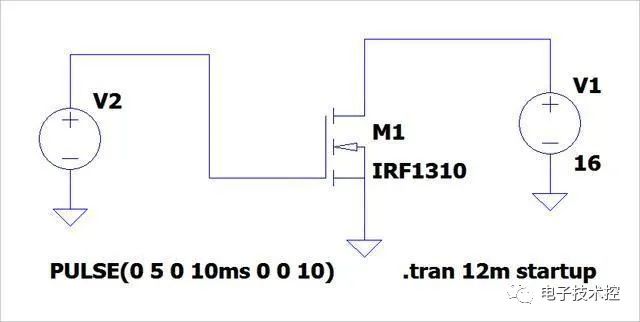

首先通过下图测试 MOS 管(IRF1310)的栅极电压与漏极电流之间的关系。

▲ 图1.2.5 测试 MOS 管的栅极电压 Vgs 与 漏极电流 Ids之间的关系

下图给出了栅极电压与漏极电流之间的仿真结果。可以看到当输入电压超过 3.7V 之后, 漏极电流便开始快速上升。在不同的栅极电压下(或者说在不同的漏极电流 下) MOS 管的栅极电压与漏极电流之间的动态跨导 定义为:

▲ 图1.2.6 MOS管栅极电压与漏极电流之间的关系

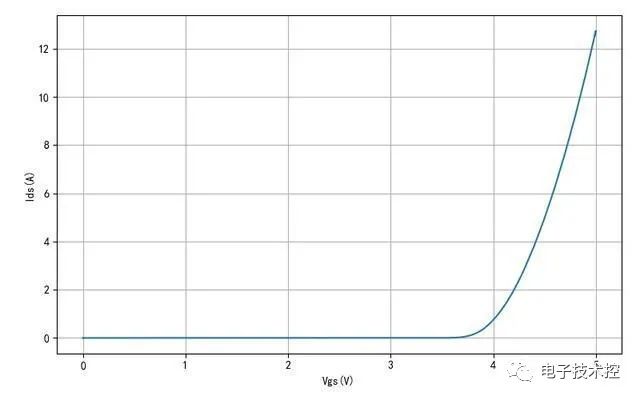

利用仿真得到的数值 ,通过各自的差分比值获得 MOS 栅极到漏极之间的跨导 ,如下是计算出的曲线。可以看到 MOS 的跨导与漏极电流大体上可以使用平方根函数进行建模,根据计算数据获建模参数为:

▲ 图1.2.7 MOS管跨导与漏极电流之间的关系以及平方根建模数据

(2)MOS单管放大器

下面使用单个 MOS 管搭建放大电路,电路的放大倍数等于:。其中 是电路静态漏极电流工作点。通过仿真可以求出 。根据前面求出的跨导模型,可以计算出 ,因此,可以计算出电路放大倍数约为:。

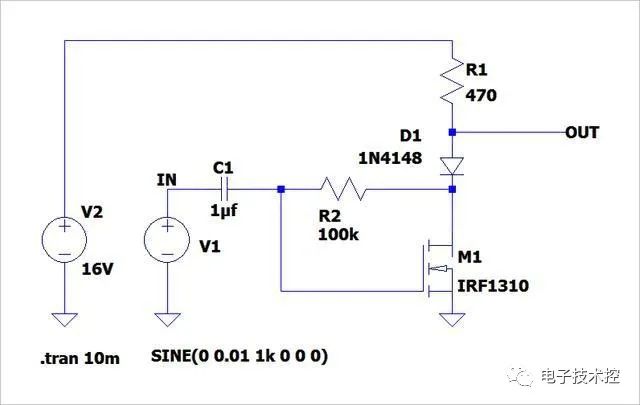

▲ 图1.2.8 单个MOS管放大电路

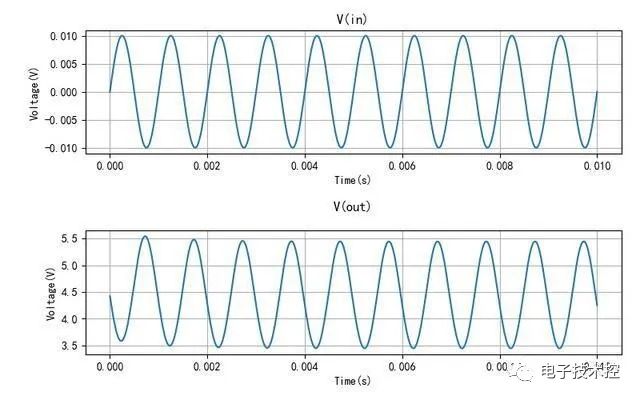

下面是在电路输入施加 峰峰值为0.01V的信号时,电路输出峰值为1V的交流信号。因此电路实际放大倍数为 100 左右。

▲ 单个MOS管输入输出电压信号

通过上述仿真计算,验证了 MOS 管处在放大状态增益远远大于 1。

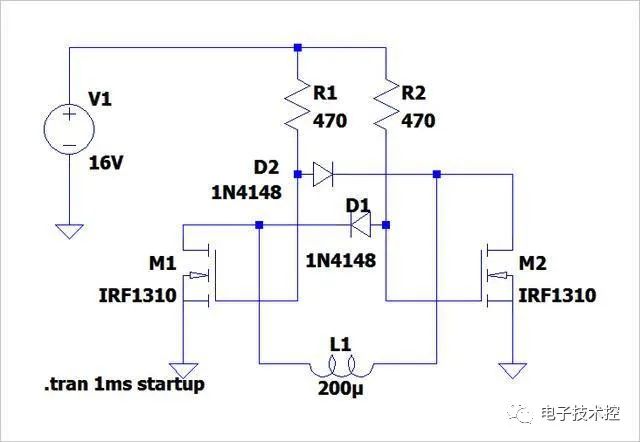

4、ZVS振荡器

由于二极管耦合电路具有两个稳态,所以该电路上电之后便停留在两个稳态之一,并不振荡。如果在两个 MOS 管的集电极增加一个电感之后,强制在两个 MOS 管的漏极之间建立一个直流通道,电路便不会在两个稳态之间持续停留了,会发生什么呢?下面看看仿真后的结果。

▲ 图1.2.10 在两个MOS管的漏极之间增加一个电感

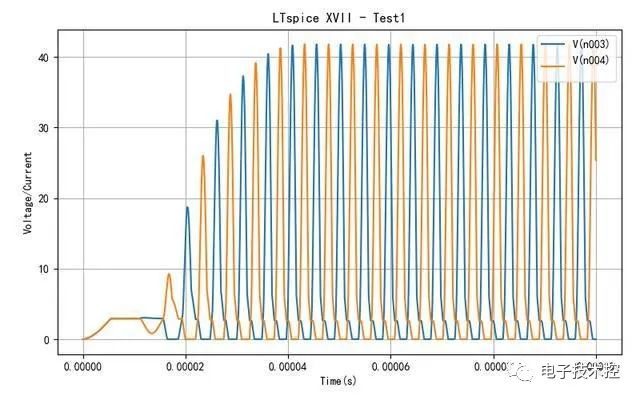

此时二极管耦合电路开始震荡,也就是在两个稳态之间来回切换。在上面电路图参数下,振荡频率为 213KHz,这应该是 L1 与 两个 MOS管杂散电容谐振的频率。

▲ 图1.2.11 M1,M2漏极电压信号

如果在 L1 上并联一个电容 C1, 电路震荡频率由 L1、C1的谐振频率决定。

▲ 图1.2.12 在L1上并联谐振电容C1

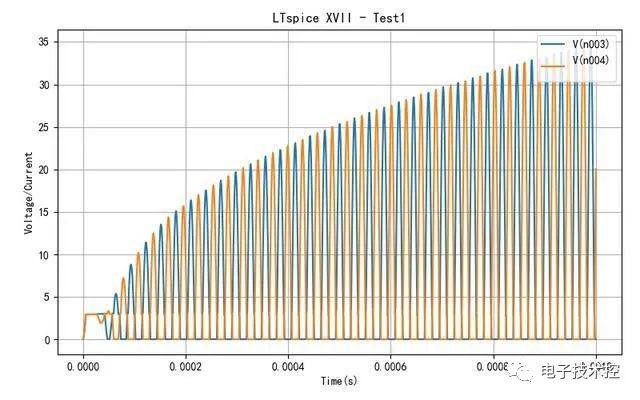

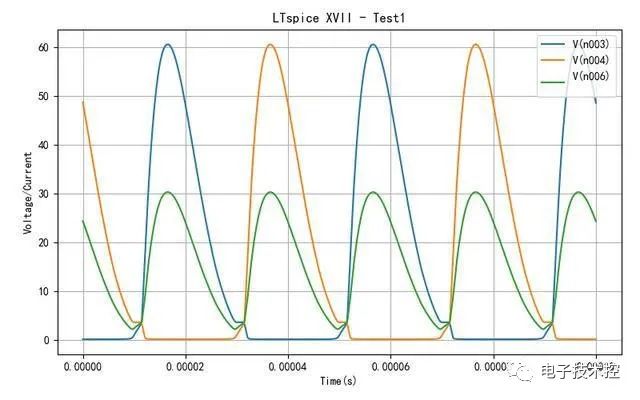

下图显示了并联谐振电容 C1 之后,电路上电后起振时两个 MOS 管漏极电压波形。震荡频率为 35.04kHz,这个频率与 C1、L1谐振频率相同。

▲ 图1.2.13 增加谐振电容电路起振后两个MOS管漏极电压波形

通过以上分析可以看到 ZVS 基本电路起振原理比较简单,在二极管耦合电路的基础上,通过将 LC 谐振电路连接在两个 MOS 管的漏极,使得电路无法停留在两个稳态状态,只能够在两个稳态之间来回切换,切换的频率最终有 LC 谐振频率决定。

三、振荡电路的改进

1、电路缺点

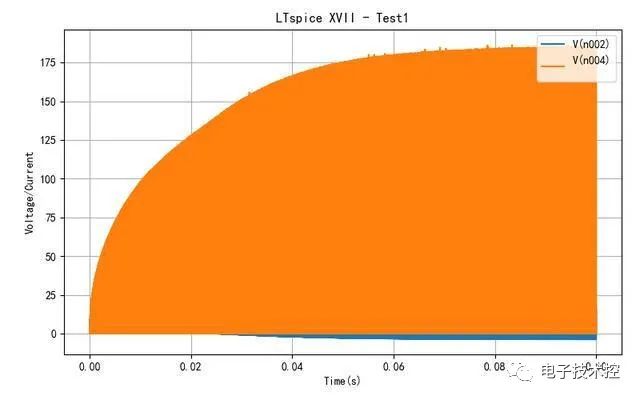

上面 ZVS 电路虽然能够振荡,但它存在一定的缺点。首先,电路振荡幅度不受控制。在电路每一次切换过程中, 在 C1 上的电压低于电源电压的器件, 电源总可以通过 R1,R2, D1,D2向 C1 充电,这个电能会叠加在 LC 谐振回路中。当 C1 上的电压超过 12V 时, 截止的二极管和 MOS 管又阻止 LC中的能量消耗,这就会使的 LC 谐振电压越来越多。

下图显示了电路在 0.1 秒钟之后 MOS 管漏极震荡电压就超过了 180V, 这个电压已经超过了 IRF1310 的 Vds 最高耐压了。

▲ 图1.3.1 MOS管电压波形

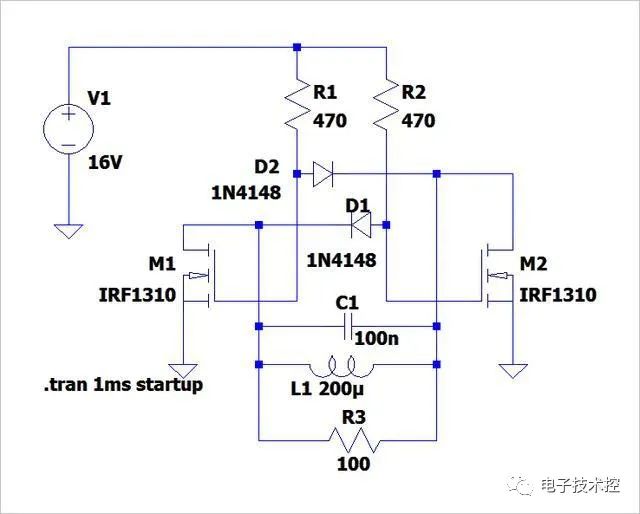

电路的第二个缺点就是 LC 谐振回路带负载能力弱。比如在 LC 谐振回路上并联一个负载电阻 R3(100欧姆), 此时两个 MOS 管的漏极电压峰值降低到 3.3V。这主要是因为电源能量需要经过 R1、R2才能够补充到 LC 回路,所以损耗比较大。

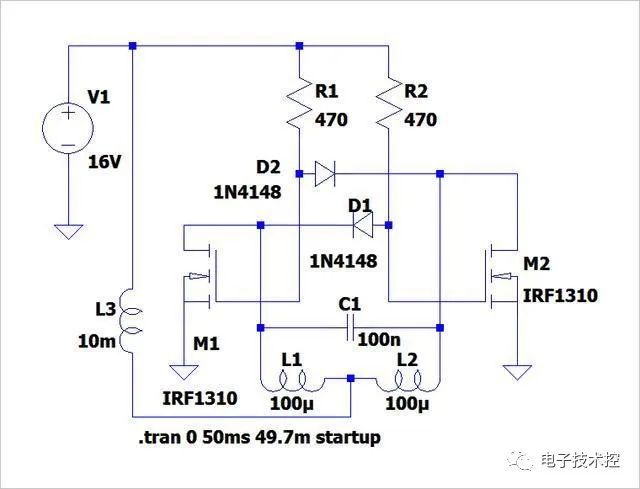

▲ 图1.3.2 在LC谐振回路增加负载电阻R3之后的电路图

▲ 图1.3.3 增加负载之后MOS管漏极电压波形

2、电路改进

为了消除上面的缺点,考虑将电源电压直接引入 LC 谐振回路。把原来的电感 L1 分成两个对称的电感 L1,L2,然后在使用一个扼流圈 L3 将 L1,L2 中点连接到电源 V1 上。这样电源直流电能便可以通过 电感 L3直接补充到谐振回路中了。

▲ 图1.3.4 通过扼流圈L3直接把电源引入LC谐振回路

之所以使用扼流圈,也就是数值比较大的电感 L3 连接 LC 谐振回路到电源,是为了隔离 LC 谐振回路与电源之间的交流通道,即 LC 谐振回路的频率和波形不会因为接入电源而发生改变,因此要求 L3 的电感量比较大,需要比 L1、L2的电感量超出一个数量级以上。

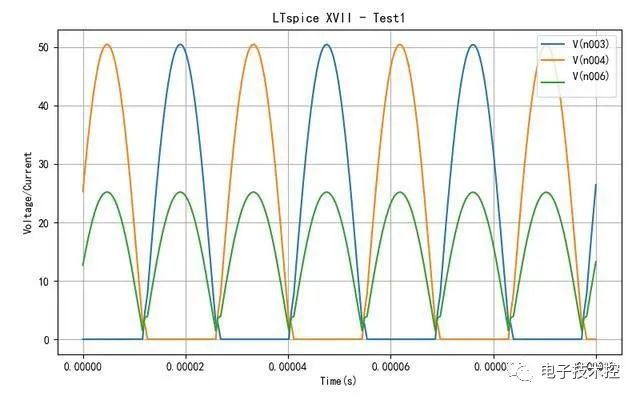

下面是电路中两个 MOS 管漏极电压以及 L1、L2 中点电压波形。

▲ 图1.3.5 两个MOS管漏极电压以及L1L2中点电压波形

LC 谐振回路两端电压波形应该是正弦波,由于谐振回路两端被两个 MOS 管分别在两个半周期接地,所以在每个 MOS 管的漏极就出现了正弦波半波整流电压波形。L1、L2中点的电压波形是两个 MOS 管漏极电压的平均值,所以它是正弦波的全波整流波形。

施加在扼流电感 L3 两端的电压,一端是电源电压 V1, 一端是L1、L2中点电压。当 L1、L2中点电压的平均值低于电源电压 V1 时, L3 中的流向谐振回路电流变化增加,持续向 LC 谐振回路增加能力。如果 L1、L2 中点电压平均值低于 电源电压 V1 时, L3 中的电流变化减少,甚至反向流向电源 V1。

因此,在电路震荡平衡时, L1、L2 中点电压的平均值应该等于电源电压 V1。对于峰值为 E 的 全波整流信号,对应的平均值为 ,所以有:

MOS 管漏极电压峰值为 L1、L2 中点电压峰值的两倍,所以可以得到 MOS 管两端正弦半波整流的峰值电压为 。在上面仿真电路中,由于 ,所以 MOS 管两端峰值电压为 50.3V 左右。

下面在 LC 回路两端并联负载电阻 R3=32Ω,经过仿真,仍然可以看到电路振荡幅度维持在 50V 以上,这也显示了 LC 谐振回路很强的带负载能力。

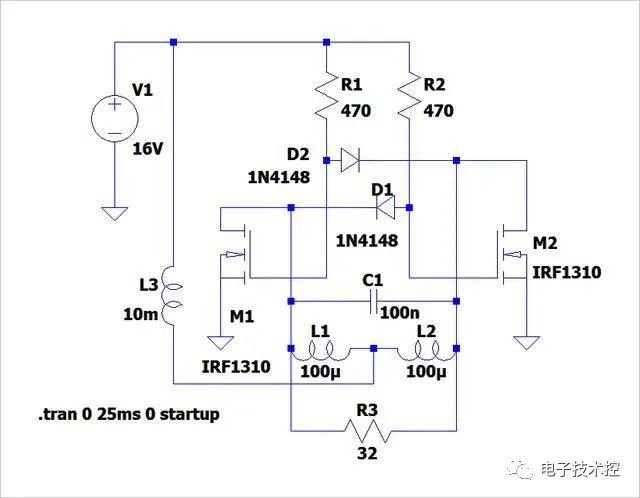

▲ 图1.3.6 在谐振回路并联负载电阻

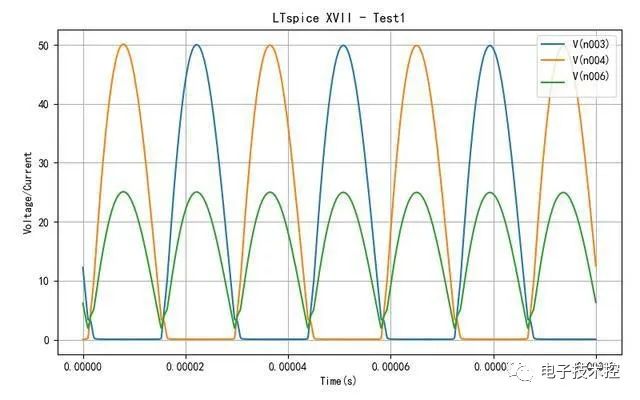

下图显示了两个 MOS 管漏极电压和 L1、L2 中点电压波形。由于负载电阻 R3 已经小于 LC 谐振时对应的 L 感抗(大约在44.7欧姆),所以 LC 振荡波形已经有了明显的失真了。

▲ 图1.3.7 增加有负载电阻后的MOS管漏极以及L1,L2中点电压波形

如果想进一步提高电路中 LC 回路带负载能力, 需要减少 L1、L2 的电感,增加 C1的电容,这样便可以增加 LC 回路储能数量, 降低谐振时 L 对应的感抗。比如在上述电路中, 将 L1、L2的电感减少到 20uH, C1增加到 500nF,LC 谐振频率不变,仍然并联 32Ω 的电阻负载,电路振荡波形如下图所示。可以看到电路振荡受到影响很小。

▲ 图1.3.8 电路振荡波形

3、MOS管栅极保护

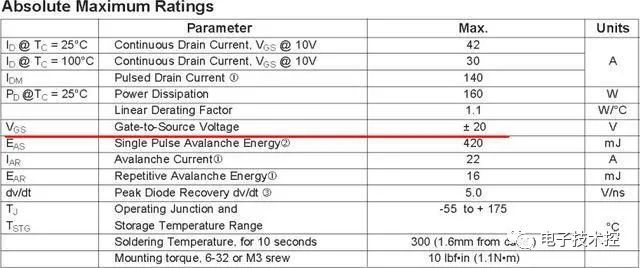

为了进一步提高电路功率输出,可以提高电路的工作电源 V1 的电压值。由于 MOS 管的栅极与源极之间具有最大耐压限制,比如对于 IRF1310 MOS 管, Vgs最大不超过 ±20V,所以需要对 MOS 管的栅极增加保护,一般是通过增加稳压二极管来限制 MOS 管的最大电压。

▲ 图1.3.9 IRF1310 栅极最大电压限制

在最初大家看到的电路中, 稳压二极管 D1 ,D2 就是用于保护两个 MOS 管栅极电压的。并联的 R1,R2 是为了加快 MOS 管栅极电压更快的降低。

四、电路参数设计

根据前面介绍的 ZVS 工作原理,对于电路中的 MOS管参数、LC 谐振回路参数、保护二极管耐压等都比较容易选择。下面对于电路中其它的器件参数进行讨论。

1、扼流线圈

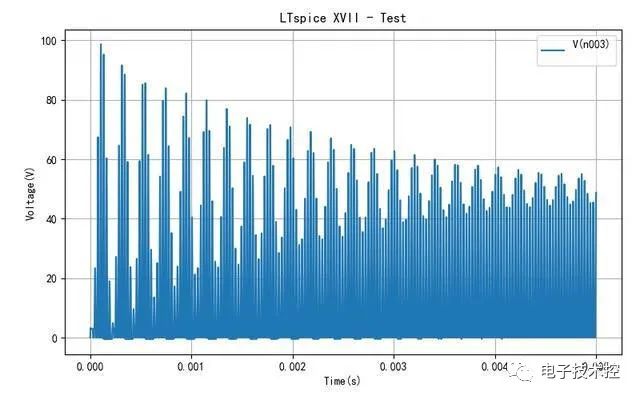

扼流线圈的存一方面是放置 LC 回路受到电源回路的影响,同时也能够降低 ZVS 电路在起振过程冲击电流,它的电感比 LC 谐振回路中的电感要大一个数量级以上。

扼流线圈也会与 LC 回路中的电容形成谐振关系,影响 LC 电路振荡幅度。下面是扼流圈电感去 1000nF时,ZVS 电路起振过程中 MOS 管漏极电压信号,可以看到由于扼流线圈引起电路在起振过程中出现幅度的波动。

▲ 图1.5.1 ZVS起振过程中MOS漏极电压信号

扼流线圈电感量增加也会带来线圈体积、串联电阻的提升,所以在工程设计中需要进行折中。

2、偏置电阻

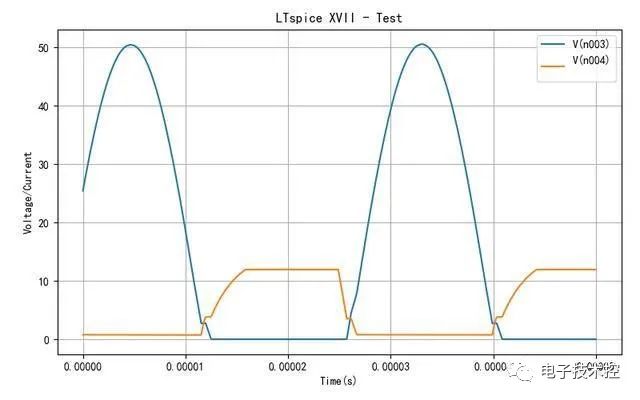

ZVS 电路中的两个偏置电阻 R3,R4 取值会影响到 MOS 管栅极开启电压的速度。下面给出了电路 MOS 管的漏极电压和栅极电压波形,其中偏置电阻取 470 欧姆。由于二极管的作用, MOS 管的栅极电压下降比较快,但上升过程,则是由两个偏置电阻引起栅极电压的上升。因此,偏置电阻需要尽可能减小,提高 MOS 管导通速度。

▲ 图1.4.2 MOS管漏极和栅极电压波形

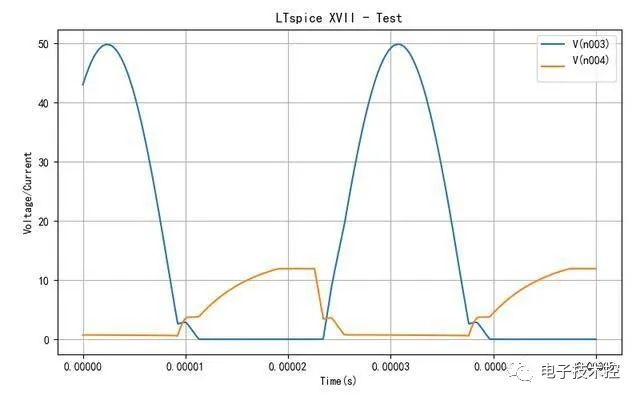

下图给出了偏置电阻取 1000Ω 时,电路振荡波形,可以看到 MOS 管栅极电压上升明显减缓了,这样就会增加 MOS 开启过程中的功耗。

▲ 图1.4.3 MOS管漏极和栅极电压波形

当然, R1, R2也不能够太小,否则两个电阻上的功耗也会增加。

总 结

本文基于 LTspice 仿真,分析了 ZVS 振荡器的工作原理以及相关的参数设计。

审核编辑:汤梓红

-

压控振荡器的工作原理是什么2024-09-25 2618

-

多谐振荡器的工作原理、分类、设计方法和应用2024-07-17 6409

-

振荡器的工作原理解析2023-11-22 9516

-

振荡器的工作原理2023-07-04 3879

-

RC相移振荡器工作原理+参数计算公式+电路设计总结2023-03-30 15415

-

振荡器的分类及工作原理2021-08-11 20408

-

石英晶体振荡器工作原理和应用2017-02-07 1739

-

压控振荡器工作原理及应用2010-04-23 11173

-

RC桥式振荡器的工作原理2010-04-20 8265

-

压控振荡器(VCO)的定义 控振荡器工作原理及应用2010-04-17 7311

-

反馈式振荡器,反馈式振荡器工作原理分析2010-03-22 3206

-

振荡器工作原理2009-08-21 17148

-

变形间歇振荡器工作原理2008-01-21 1492

全部0条评论

快来发表一下你的评论吧 !