一文解析ADC/DAC架构

电源/新能源

描述

如今的世界充斥着各种数字信号和模拟信号。这些信号表现不同,但通常都被用来帮助实现更大的目标。想象你是负责控制 HVAC 装置的工程师。无论你打算使用哪种类型的微控制器或微处理器,它必须能够读取具有无限量值的模拟温度,并将其转换为分立步进中的二进制表示形式。这种二进制表示的模拟值将由微控制器或微处理器处理。这些数据将被 HVAC 装置用来帮助执行一个程序,以帮助维持稳定的环境。在处理需要由数字系统处理的模拟值时,模数转换器 (ADC) 是必不可少的。同样的理论也向后适用于需要转换成模拟信号的数字信号。在线播放歌曲涉及到将数字信号转换为模拟信号的几个步进。主机设备从服务器接收到的信号将是原始模拟信号的二进制表示。侦听器无法解读此二进制数据的音频响应。原始信号是模拟的,所以最后的表示也应是模拟的。模数转换器 (ADC) 可以解决这个问题。这种类型的设备可以将一个被模数转换器编码的二进制代码转换回模拟电压。

对如今的工程师来说,将模拟信号和数字信号相互转换是一项不可避免的任务。有很多不同类型的模数转换器和数模转换器。虽然它们的架构不同,但功能是类似的。不能用模拟值来进行数字信号处理,这就跟讲法语的人跟讲德语的人无法交谈是一个道理,必须要有翻译员才行,而 ADC 和 DAC 就相当于翻译员。当 ADC “看到”模拟电压时,其工作就是在给定的时间段内将模拟电压转换为二进制码,这意味着它必须在瞬间完成对模拟电压的采样,然后确定 ADC 输出端的二进制值。该器件每秒钟采样的数量将在其说明文档中被调出。例如 Maxim Integrated 的 MAX1118EKA+T。该器件的采样率为100 kHz,即每秒钟对输入端的模拟电压采样 100,000 次。它能够在一秒钟内采集这么多样本,意味着可以通过使用二进制表示来精确地记录模拟电压。有时,ADC 的采样速率不够高,不足以准确地重建引起混叠的输入。这时,信号开始无法彼此区分或混叠。想象一下,数码摄像机每秒可拍摄 24 帧,对大多数应用来说是足够的,但要捕捉移动非常快的物体,可能就会导致图像扭曲。回想九十年代后期在电视上看录像带的效果,电视上的图像会不停闪烁,这是因为电视本身的刷新率比录像带的每秒帧数还要快。图像之所以会扭曲,是因为视频实际上是一连串图片的组合。视频实际无法呈现出每两幅图片之间发生的所有活动。ADC 也是同样的道理。为避免这种情况,应确保采样率至少比需要传输的最高频率高两倍。这通常被称为“奈奎斯特率”。

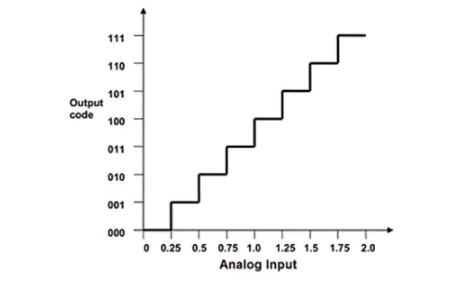

更高的采样率可以使设备更加精确,但这不是控制精度的唯一方法。这是一个将模拟信号转换为二进制码的过程,因此,有一定数量的离散步进可用于表示特定时间点的电压。用来表示这个数字的位数是分辨率。ADC 的分辨率越高,可采取的分立步进就越多。为获取更多细节,应了解如何确定 ADC 可采取的步进的数量。ADC 的一个二进制输出可代表供电电压。如果供电电压是 10 V 并且有一个 8 位 ADC,可能会有 256 步。分辨率可通过等式 2n 计算出来。“2”是一个常数,“N”代表位数。例如,等式 28 的结果是 256 步。如果供电电压是 10 V 并且有 256 步,那么每步是 39.0625 mV。针对每个步将会有不同的二进制码。如果在 ADC 上从低到高运行所有可能的输入选项,就可以看到结果呈现出楼梯的形状,这是 ADC 传递函数的图形表示。图 1 展示了使用 3 位 ADC 和 2 V 基准进行的转换。

图 1: 3 位 ADC 和 2V 基准的传递函数。(由 Microchip Technology 提供)

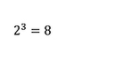

对于 3 位 ADC,可以通过以下 2n 等式来计算步总数:

如图 1 所示,000 与 111 之间有 8 步。每两步之间增加 1 个 LSB。

如前所述,ADC 有几种不同的架构。三种最常见的 ADC 架构是逐次逼近寄存器 (SAR)、三角积分 (∆∑) 和流水线转换器。每一种类型的转换器都可以将模拟信号转换为数字输出,但在实现过程方面有细微的差别。SAR 对模拟输入进行采样并保存,然后将其转换为数字信号并输出。三角积分转换器取的是一段时间内所采样本的平均值,然后再转换为数字信号。流水线转换器将转换过程划分为多个阶段,以实现超快的转换速度。这些转换器都各有优势和劣势。SAR 架构易于使用,通常具有低功耗、低延时和高精度的优点。三角积分转换器具有分辨率极高、稳定性高、功耗低和成本低的优点,但工作速度要比 SAR 和流水线架构低很多。流水线 ADC 的工作速度和带宽相对较高,但分辨率较低,需要更多的功耗。

逐次逼近寄存器

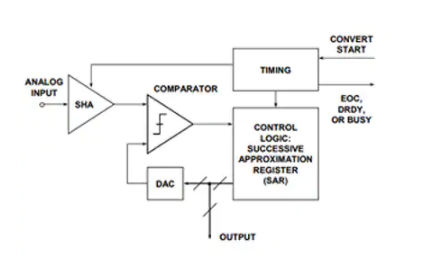

逐次逼近寄存器是最常见的 ADC 类型,其通常会有一个 I2C 或 SPI 接口,有时会有一个并行输出。为帮助处理模拟信号,SAR ADC 将采样并保存,以维持信号恒定。它带有一个比较器,可以根据内部 DAC 测量模拟输入。此时,DAC 将被设置为其潜在电压的 ½。如果输入高于 DAC,比较器将输出 1 以存储在逐次逼近寄存器的 MSB 中。然后,DAC 将被设置为其潜在电压的 ¼。这个过程将重复下去。DAC 的下一个值是 1/8,然后是 1/16,以此类推,直到所有的位被加载到寄存器。打个比方,为了确定某个物品的重量,我们会逐次增加或减少砝码,这是同样的道理。下面的图 2 说明了这一点。

图 2: 逐次逼近 ADC 将模拟值转换为数字值的图示。(由 Analog Devices 提供)

方块 = 45 个单位。第一次尝试将放上 32 个小方块,每个小方块为 1 个单位。该方块比所有小方块还要重,因此保留 32 个小方块。下一步是增加 16 个小方块,即 32 + 16 = 48,结果比方块要重,拿走这 16 个小方块。下一步是增加 8 个小方块,即 32 + 8 = 40,仍需增加小方块。可以再增加 4 个小方块,达到 44 个。之后再增加 2 个小方块,即 46 个单位,但这样会大于 45,因此拿走这 2 个小方块。最后增加 1 个小方块,天平达到平衡。每次增加的小方块的数量都是上一次的一半。这个图示展示了 SAR 中 DAC 提供数值的过程。图 3 显示了逐次逼近寄存器 ADC 的框图。

图 3: 逐次逼近 ADC 的功能框图。(由 Analog Devices 提供)

SAR ADC 的例子包括 Texas Instruments 的 ADS7886SDBVT。这是一个 12 位 ADC,意味着 0 V 与电源电压之间有 4,096 步。采样率为 1 MHz,即每秒查看输入一百万次。在应用于成品之前应测试 ADC 性能,因此,制造商通常会制作评估工具来帮助测试。ADS7886SDBVT 拥有此类评估工具,即 ADS7886EVM。该工具提供了一个带有 ADC 功能测试所需的所有无源器件的电路板,使测试更加轻松。

三角积分 ∆∑

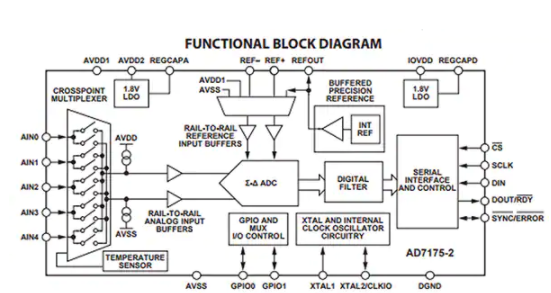

三角积分转换器非常适用于需要高分辨率和精度的应用,录音就是三角积分转换器的一个很好的用例。三角积分转换器需要对其输入进行过采样。讨论三角积分转换器时,通常无需考虑奈奎斯特率,当采样率比最高采样频率高大约 20 倍时,它们会达到最佳运行状态。三角积分转换器的输出被输送到数字滤波器和抽取器,以处理数字位流,形成最终输出。数字滤波器和输出之间通常有一个串行接口。三角积分转换器的例子包括 Analog Devices, Inc 的 AD7175-2BRUZ。 图 4 为 AD7175-2BRUZ 的功能框图。

图 4: Analog Devices AD7175-2BRUZ 三角积分 ADC 的功能框图。(由 Analog Devices 提供)

三角积分 ADC 具有 24 位分辨率和 250 kHz 的采样率,步进总数有可能达到 16,777,216,这意味着它的分辨率比上一个例子的 SAR ADC 还要高很多,但采样率只有后者的大约 ¼。和之前的示例一样,AD7175-2BRUZ 也有一个测试用的评估板。这块电路板是 EVAL-AD7175-2SDZ,提供了轻松评估 ADC 的方式。

流水线

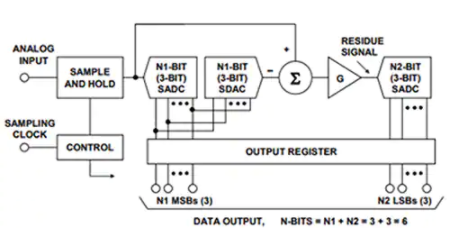

流水线 ADC 是速度最快的。“ADC 架构 IV: 流水线分区 ADC”中的例子通过 6 位流水线 ADC 说明了这一点。它会象 SAR 一样采样并保存,但在那之后,3 位子 ADC 闪存转换器将直接对信号进行数字化处理。3 位转换将针对 3 个最大有效位。之后,子 DAC 会将模拟信号转换回数字信号。ADC 将从采样和保存输出中减去该输出,将其放大,然后发送回第二级 3 位子 ADC,以处理其余三个最小有效位。图 5 的框图可以说明这一点。

图 5: 流水线分区 ADC 的功能框图。(由 Analog Devices 提供)

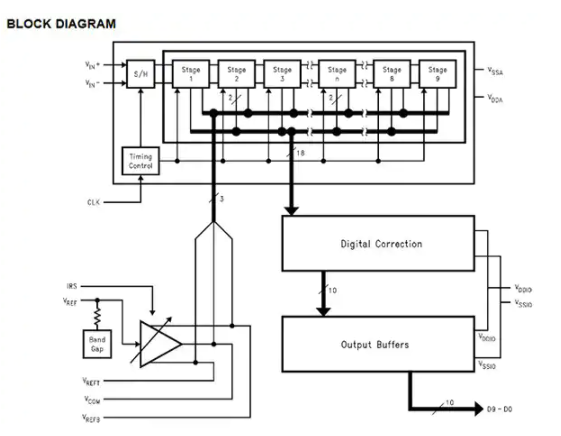

流水线 ADC 的例子包括 Texas Instruments 的 ADC10080CIMT/NOPB。它是一个 10 位 ADC,可达到 1,024 步,每秒可转换 80 兆样本。这种设备可用于超声波和成像、仪器、数据采集系统,或者任何涉及快速转换的应用。查看 ADC10080CIMT/NOPB 框图可以了解如何按前面所述进行设置。图 6 是 ADC1008CIMT/NOPB 规格书中的框图。

图 6: Texas Instruments ADC10080CIMT/NOPB 的功能框图。(图片由 Texas Instruments 友情提供)

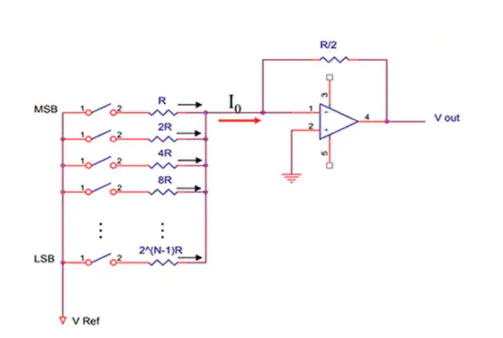

二进制加权 DAC

到目前为止,本文重点讲述了 ADC 的数据转换,但这只是需要考虑的一部分。通常需要将二进制数据转换回模拟信号,这时就需要数模转换器。学校教授的第一种 DAC 通常是二进制加权 DAC。它需要使用一个电阻器系统,其输出将全部输入到同一个求和电阻器。有效位更大,输出的电流也就更多。这是通过创建一个反比的电阻器网络来完成的。数字码的每个二进制位将拥有相同的电压值,通过对每个位使用反比电阻器,较大的位将允许更多的电流通过。这种转换方法如今已经不常用了,现在有更简单的方法。不过,它是说明 DAC 运作方式的绝佳着手点。这种方法最大的困难在于找到能够相互配合的不同等级的电阻器。此外,二进制加权方法要求容差非常小,而且需要几个不同值的电阻器,这比相似值的电阻器很难找。图 7 通过二进制加权电阻器网络的图示展示了这种架构。

图 7: 二进制加权电阻器网络的图示。(图片由 Georgia Institute of Technology 提供)

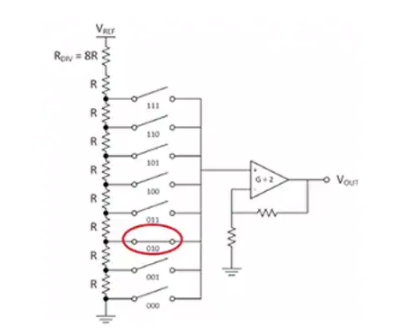

串式 DAC

另一种常见的 DAC 架构是串式 DAC。这是最简单,也是线性最小的架构,有时被称为“Kelvin 分频器”。这种 DAC 有一系列串联的等值电阻器,顶部有基准电压值,串联的前面有高阻抗的电阻器,并且每个节点都有专用于二进制码的开关,在设备读取该代码时关闭。这有助于模拟电压值的使用,而该值取决于二进制输入。图 8 来自 Texas Instruments 的标题为“什么是串式 DAC?”的视频。代码 010 被选为十进制值 2。010 的开关处于关闭状态,使该节点的 DC 电压传输到求和放大器。

图 8: 串式 DAC 的图示。(图片由 Texas Instruments 友情提供)

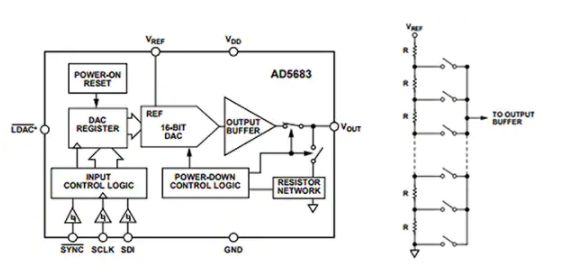

串式 DAC 很容易形成,因为串联的每个部分都使用等值电阻器(不包括高阻抗电阻器)。串式 DAC 的例子包括 Analog Devices Inc. 的 AD5683RBRMZ。它是一个与 SPI 配合的 16 位串式 DAC。图 9 是这个设备的功能框图,图 10 是电阻分压器的功能框图。这款产品也有评估工具,即 EVAL-AD5683RSDZ

图 9 和图 10: Analog Devices AD5683RBRMZ(左)及其电阻分压器网络(右)的功能框图。(由 Analog Devices 提供)

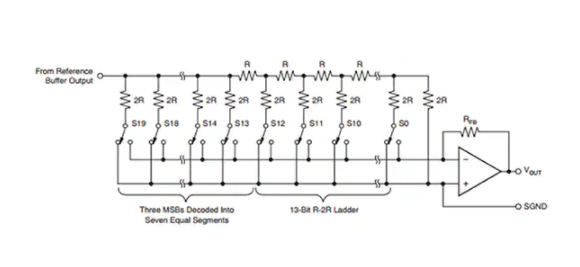

R-2R

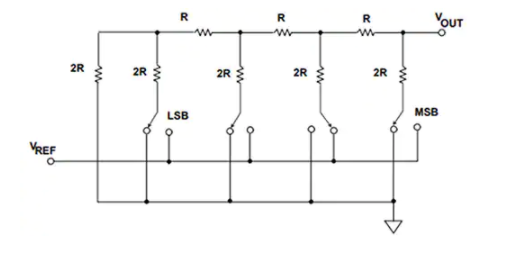

R-2R 网络是一种很常见的 DAC 架构。它只使用两个电阻值,只要 2R 是 R 的两倍,这两个值就无关紧要。这使得 R-2R DAC 的可扩展性很大。无论这种 DAC 是多少位,都只需要两个电阻值。图 11 展示了 4 位 R-2R 梯形网络。

图 11: R-2R DAC 的图示。(由 Analog Devices 提供)

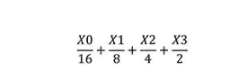

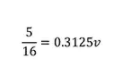

这种分频器网络使用了戴维南定理,最终为整个“R”网络实现戴维南等效电阻。每个阶段都允许电压翻倍,直到最后阶段。在这个例子中,如果 Vref 是5 V,那么 LSB 最左边的阶段只能产生 0.3125 V。从左到右的比例电压输出将是:

这是所有数字输入的代表,X0 是 LSB,X3 是 MSB。使用 5 V 基准可得到:

按照相同的逻辑,要找到最大有效位的模拟电压值,可以使用以下等式:

如果有一个 1111 的二进制输入,输出就不会等于 5 V。请回想前面讨论的解决方法。如果是 4 位 DAC,可以有 16 步。这是因为 24 等于 16。LSB 是 0.3125 V,如果你认为直接用 0.3125 x 16 = 5,那就错了,因为其中一步涉及接地的 0 V,以代表二进制 0000。这意味着可实现的最高电压是电源电压减去一个 LSB 电压,结果是 4.6875 V。

R-2R DAC 的例子包括 Texas Instruments 的 DAC8734SPFB。它是一个 16 位转换器,可体现这些设备的可扩展性。它的 R-2R 网络的布局与上个例子非常相似。图 12 展示了 DAC8734SPFB 的 R-2R 网络。DAC8734SPFB 也有评估工具,即 DAC8734EVM。

图 12: Texas Instruments 的 DAC8734SPFB R-2R DAC 的图示。(图片由 Texas Instruments 友情提供)

还有许多其他类型的 ADC/DAC架构,但本文仅讨论一些更常见的架构。这些设备对如今的数字信号处理而言是必不可少的。如果没有 ADC/DAC 器件,就无法将模拟输出集成到任何类型的数字信号处理中,反之亦然。对外行来说这没有什么,但对于负责将模拟部件连接到数字系统的工程师而言,这是需要考虑的最重要的步骤之一。在思考模数转换时,可以回想一下讲不同语言的两个人交谈的类比。如果没有翻译员,讲不同语言的人就无法沟通。如果没有正确使用 ADC/DAC器件,设备只能使用单纯的模拟信号或数字信号。ADC/DAC 器件是这两个领域之间的桥梁。

资源

- “AVR127: Understanding ADC Parameters”.May.2016.

- “Choose the right A/D converter for your application”.Retrieved 8 May.2017.

- Kester, Walt.“ADC Architectures II: Successive Approximation ADCs”.Oct. 2008.

- Kester, Walt.“ADC Architectures III: Sigma-Delta ADC Basics”.Oct. 2008.

- Kester, Walt.“ADC Architectures IV: Sigma-Delta ADC Advanced Concepts and Applications”.Oct. 2008.

- Kester, Walt.“ADC Architectures V: Pipelined Subranging ADCs” Oct. 2008.

- Kester, Walt.“DAC Interface Fundamentals”.Oct. 2008.

- Kester, Walt.“Basic DAC Architectures II: Binary DACs”.Oct. 2008.

- Lee, J., Jeelani K., Beckwith, J. “Digital to Analog Converter”.Retrieved 8 May.2017

- Poole, Matt.“What is a String DAC?”.April 4, 2016

-

解析电阻串DAC架构原理2018-07-26 17246

-

基本DAC架构:分段DAC2022-08-01 3445

-

一文详解ADC与DAC2022-08-30 43238

-

ADI ADC和DAC电路解析2013-04-10 2663

-

电阻串DAC架构原理2018-09-18 2865

-

ADC/DAC的基础知识2018-11-01 5491

-

ADC及DAC的历史进程概况2010-02-26 2705

-

ADC/DAC,ADC/DAC的原理是什么?2010-03-26 22066

-

DAC/比较器架构与集成ADC优势比较2011-12-28 3327

-

一文解析PLC的应用2018-07-19 6310

-

如何针对应用选择合适的DAC或ADC2019-07-03 6183

-

DSP教程---ADC和DAC2021-09-16 1470

-

详解ADC和DAC的基本架构2022-03-01 9670

-

一文带你了解 DAC2023-12-07 13923

-

AD5592R:8 通道、12 位可配置 ADC/DAC 的全面解析2026-03-25 192

全部0条评论

快来发表一下你的评论吧 !