高速链路建模及信号完整性分析系列装备介绍

模拟技术

描述

今天介绍全新的高速链路建模及信号完整性分析系列装备。 通过收购 SiSoft 及其产品,MathWorks 将 QCD 和 QSI 工作流与 MATLAB 和其他产品集成,使您能够超越信号完整性分析。

(一) 产品映射

QCD 和 QSI 的布局前功能(pre-layout)和布局后功能(post-layout)现在是信号完整性工具箱(Signal Integrity Toolbox)和RF PCB 工具箱(RF PCB Toolbox)的一部分。 信号完整性工具箱提供两个应用程序:串行链路设计器应用程序(Serial Link Designer APP)和并行链路设计器应用程序(Parallel Link Designer APP),分别提供与QCD和QSI相同的预布局功能和接口,允许您使用 IBIS-AMI 和行业标准设计工具等模型设计和分析高速串行和并行链路。 您可以使用信号完整性工具箱和RF PCB 工具箱实现 QCD 和 QSI 的 post-layout 布局后功能。RF PCB 工具箱允许您将PCB布局导入信号完整性工具箱,以关联和验证您的设计。RF PCB 工具箱还提供全波电磁技术,您可以分析板上互连,如通孔和有损传输线;使用此分析获得S参数、阻抗以及电荷和电流分布。 如果使用 SimFarm 进行大规模仿真,现在可以使用并行计算工具箱(Parallel Computing Toolbox)执行数千次仿真,并使用 MATLAB 并行服务器(MATLAB Parallel Server)将这些模拟扩展到远程集群。

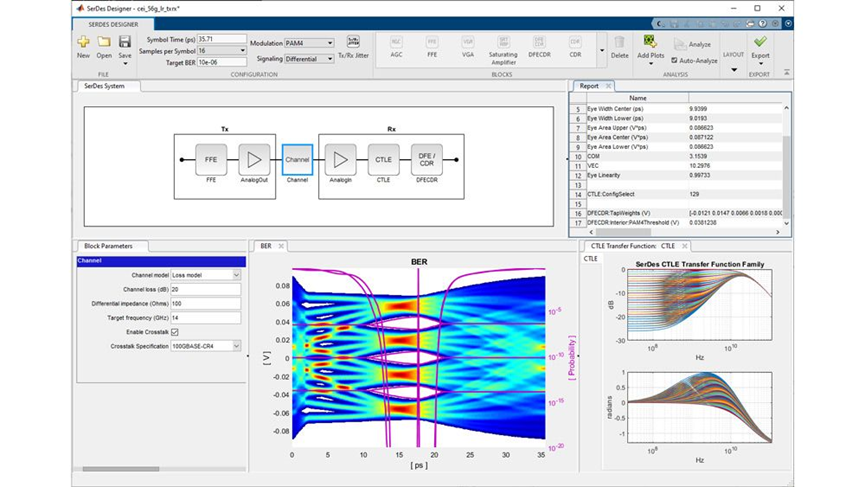

(二) 高速链路建模和信号完整性系列新装备一瞥 SerDes Toolbox

可用于设计和验证高速串行器/解串器 (SerDes) 系统或 DDR5 等高速存储器物理层设计,并生成 IBIS-AMI 双模型。工具箱提供 PCIe、USB、以太网和 DDR 等典型应用的白盒示例,您可以在这些参考设计的基础上开展设计, 包括 CTLE、DFE、FFE 和 CDR 等架构设计和自适应算法。评估眼图、浴盆曲线和通道裕量 (COM) 等指标,包括抖动和串扰效应。

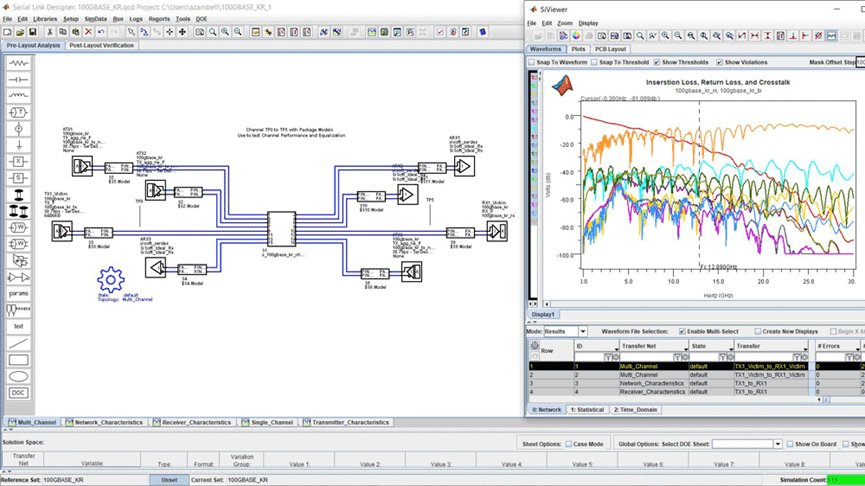

PAM 4 SerDes 系统,包括自适应 CTLE 和 DFE Signal Integrity Toolbox 对高速串行和并行链路进行仿真和分析。您可以使用多端口 S 参数数据、IBIS、HSPICE 和解析模型来描述通道。分析波形和眼图并测量通道质量,同时观察 ISI、抖动和噪声等影响。在频域中分析通道的插入损耗、回波损耗和串扰,并验证是否符合行业标准,包括 IEEE 802.3、OIF、PCIe 和 DDR。

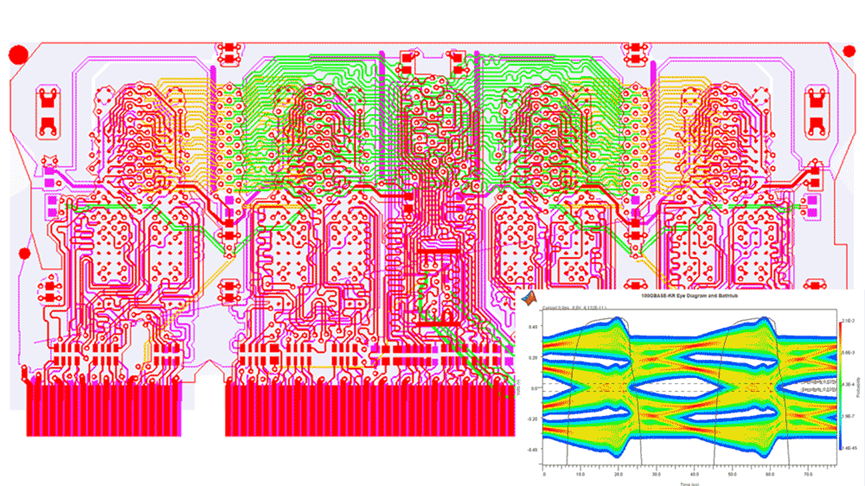

100GBASE-KR 串行链路的设计 RF PCB Toolbox 用于设计、分析和可视化高速和射频多层印刷电路板 (PCB)。支持互连结构的布局后分析和全波电磁分析。

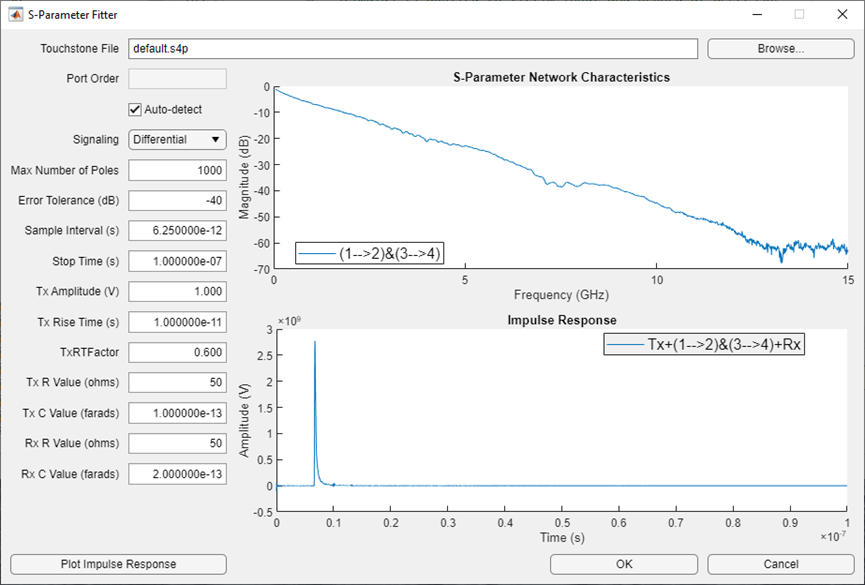

验证复杂PCB的布局后性能 RF Toolbox 提供一组丰富的函数,用于验证、操作和可视化S参数,以在信号完整性分析中使用。

从S参数数据文件创建脉冲响应

(三) 业界应用案例

新系列工具箱在最近 3 年内陆续推出,已经赢得了不少半导体和通信公司的青睐。

英飞凌(Infineon)使用Simulink和SerDes工具箱在两周内开发、验证和交付IBIS-AMI模型。

“如果没有 SerDes 工具箱,我们将不得不把工作承包出去。即便如此,由于需要来回奔波,要在短短两周内完成这项工作也极为困难,我们也不得不透露我们的知识产权。与我们合作的 MathWorks 工程师帮助我们快速开始 IBIS-AMI 建模,指导我们应对技术挑战,并通过示例向我们展示了如何一起使用 SerDes 工具箱、Simulink 和 QCD。” 英飞凌首席电气设计工程师尼克·博德纳鲁克(Nick Bodnaruk)说。 “使用 SerDes 工具箱创建和配置 IBIS-AMI 模型的过程简单易学。在自己完成一次后,我们完全控制了 IBIS-AMI 模型的创建,并消除了对承包商的依赖。” 该英飞凌团队从事 USB、PCIe 和 DisplayPort 应用程序的高速 SerDes 设计,并将根据客户的要求使用相同的工作流创建 IBIS-AMI 模型。

新思科技(Synopsys)使用 SerDes 和 Signal Integrity 工具箱建模和分析 USB4.0 IP IBIS-AMI 模型。

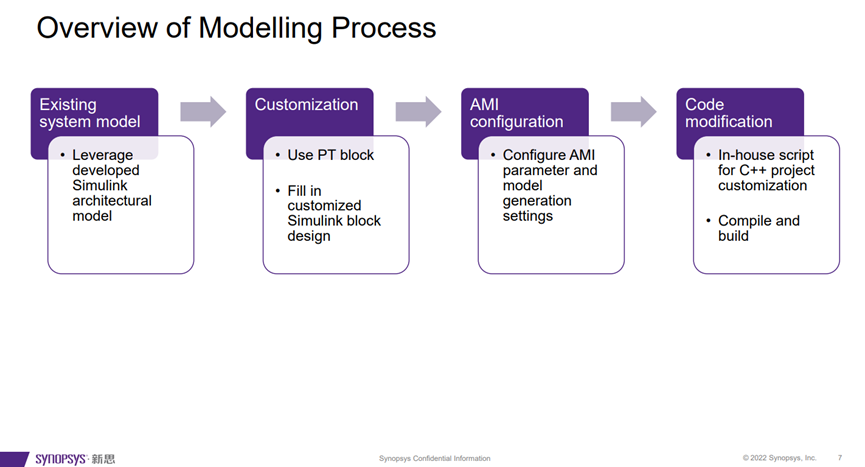

迄今为止,新思科技团队已建立了包括 USB4.0 在内的多种多协议接口 IP IBIS-AMI 建模的标准流程,SerDes 和信号完整性工具箱帮助把已有的 SerDes 架构设计整合到 IBIS-AMI 建模标准流程中。

首先使用 SerDes 工具箱进行 USB4.0 IBIS-AMI 的建模,然后运用信号完整性工具箱进行 IBIS-AMI 模型信道仿真与后仿真精度数据比对,以及运用自行开发的 Python 脚本对 MATLAB 编译器生成的 C++ 代码工程进行后处理。

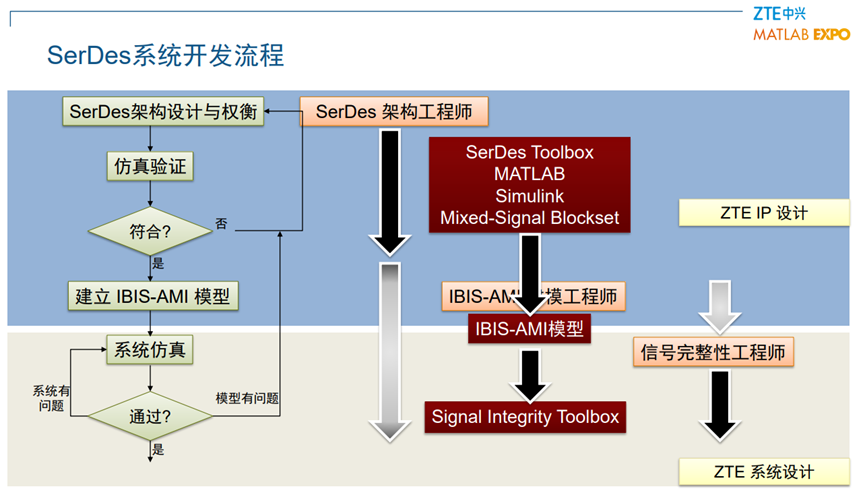

中兴通讯(ZTE)使用 SerDes 和 Signal Integrity 工具箱设计和实现5G全光承载网中的高速数据链路。

ZTE 借助 MathWorks 的工具链,快速开发用于 5G 承载网的 CEI-112G PAM4 SerDes系统,持续优化收发器结构及均衡器,确认满足系统要求。从 Simulink 自动生成IBIS-AMI模型,建模信道并进行包含 FEXT、NEXT 的 SerDes 系统信号完整性分析,确认系统符合行业规范。

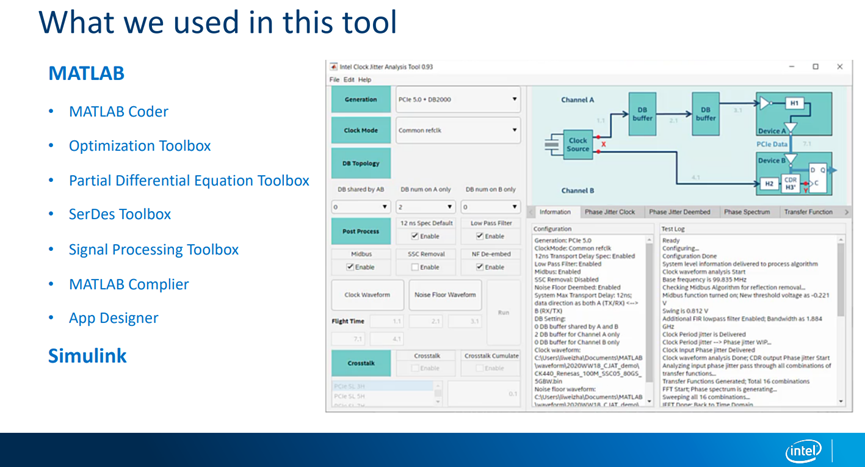

英特尔(Intel)开发 Intel Xeon 平台的时钟抖动分析工具 CJAT。

来自硅片的真实相位抖动常被示波器和探头噪声基底的影响所压倒,Intel 开发的 Clock Jitter Analysis Tool (CJAT) 可以消除示波器和探头噪声基底的影响,并保持真实的硅片抖动行为。CJAT解决了困扰工业界多年的瓶颈问题、成为业内相应领域的标杆。

CJAT 工具的开发基于数学物理方法论,同时使用了演绎法(从物理理论到数学模型)和归纳法(从验证到一般方法)。MathWorks 工具很好的整合了这2 种方法论。Intel 团队用 SerDes 和其他工具箱建模了物理学,从硅片热噪声、PLL/CDR 传输函数到 Buffer 抖动,从噪声背景中挑选关键冲击器。同时使用设备进行验证扫描,用信号处理工具箱等进行数学建模和统计分析。 通过将对高速理论的扎实理解和信号完整性知识应用于尖端设计,CJAT 引领了时钟抖动方法的创新。此外,通过将新算法打包分享给行业合作伙伴,CJAT 促进了生态系统和测量技术的发展。

结语

高速链路建模及信号完整性分析工具箱系列将在未来的产品版本中继续成长,通过结合最新的技术和解决方案实现成功的信号完整性设计。

审核编辑:刘清

-

听懂什么是信号完整性2024-12-15 1403

-

高速PCB信号完整性设计与分析2024-09-21 750

-

如何实现高速连接器信号完整性分析2023-06-04 3501

-

高速PCB电源完整性设计与分析2021-04-21 2204

-

基于信号完整性分析的高速数字PCB板的设计开发2018-08-29 2171

-

【下载】《信号完整性分析》2017-09-19 25445

-

高速信号的电源完整性分析2012-08-02 3625

-

高速电路信号完整性分析与设计—高速信号完整性的基本理论2012-05-25 2122

-

高速电路信号完整性分析与设计—信号完整性仿真2009-09-12 44560

-

高速电路的信号完整性分析2008-10-15 1416

-

基于信号完整性分析的高速数字PCB的设计方法2008-06-14 5957

-

高速电路信号完整性分析之应用篇2006-05-28 1128

全部0条评论

快来发表一下你的评论吧 !