基于FPGA 架构的微控制器子系统实现

可编程逻辑

描述

随着物联网应用的采用势头越来越猛,嵌入式开发社区面临的压力也越来越大,他们需要平衡每个设计的可用计算资源、延迟、成本和尺寸。由于其实时性,对云连接的关注也被视为某些发展的挑战,从而导致混合“雾”计算方法。配置本地网关以向雾方法提供本地云方面可能需要相当高的计算需求和算法处理。许多负责开发网关设备的设计人员面临的挑战是了解其计算要求的多样性。一些应用,尤其是工业物联网部署中的应用,可能涉及相当复杂的电机控制或视觉处理任务。对于这些要求,不仅需要高水平的计算能力,还需要实时确定性行为。虽然高端 CPU 通常是首选设备,但还有许多其他设备正在引起开发人员的注意。其中之一是现场可编程门阵列 (FPGA),由于其硬确定性能力,它正在迅速发展。

那些不熟悉使用 FPGA 的人面临着许多关于这些设备的复杂性、成本和功耗特性的神话。许多开发人员认为 FPGA 可能只适用于高度专业化、高成本的军事系统,但目前的情况与这种情况相去甚远。在当今的云连接世界中,FPGA 的最大应用是数据中心应用,除了加速搜索功能外,它们还用于使用神经网络深度学习技术进行图像识别搜索。

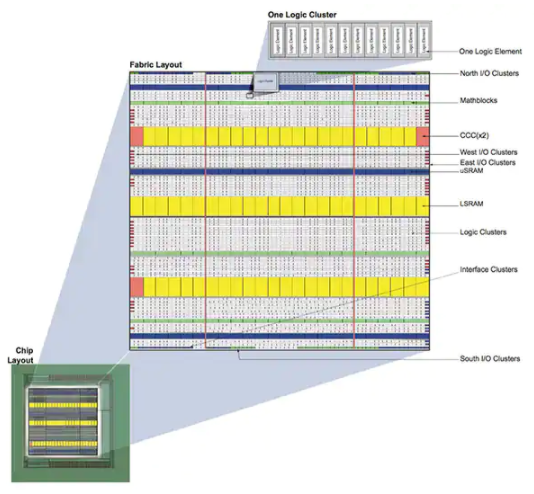

毫无疑问,精通构建基于微控制器或微处理器的系统的嵌入式开发人员在考虑使用 FPGA 时会被前面的学习曲线吓倒。对大多数人来说,显着的区别将是从基于软件的思维过程转向硬件“门”方法。FPGA 被认为是最接近设计定制 IC 的最接近的东西,它可以完全按照您的要求进行设计,FPGA 本质上是通用门和单元的空白画布,是使用硬件描述语言 (HDL) 编程或连接在一起的结构(图1)。学习数字逻辑的电子工程师很快就会对 FPGA 背后的基本概念感到宾至如归,而其他人可能会发现有关该主题的在线进修课程很有用。Simon Monk 对 FPGA 进行编程。

图 1:FPGA 器件的功能框图。

随着 FPGA 在各种应用中的使用势头越来越猛,有关它们的信息的可用性也越来越高。这主要是由领先的 FPGA 供应商推动的,他们投入巨资提供免费的开源软件工具,以帮助定义和加速设计流程。在 FPGA 架构中集成 MCU 以创建 FPGA 片上系统 (SoC) 设备进一步有助于管理 FPGA 并将其集成到最终应用中。极大地简化了学习和开发过程,有助于在更广泛的应用中使用 FPGA,并促进开放社区论坛的发展。在创客社区内采用 FPGA 也有助于激发对其功能的兴趣,并为 Mojo 和 Papilio 等许多众筹 FPGA 评估板项目做出了贡献。FPGA 制造商还努力通过创建在更广泛的开源社区中得到很好支持的开发套件和评估板来使设计更易于访问。所有这些举措共同创造了丰富的技术信息和支持资源,有助于鼓励设计人员考虑他们的第一个 FPGA 设计。

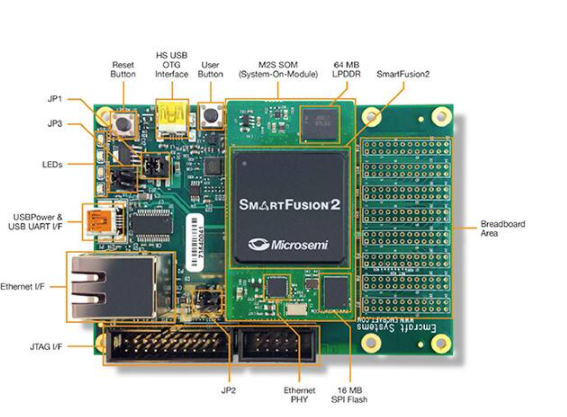

这种评估板的一个例子是Microsemi 的 SmartFusion2 入门套件,如图 2 所示。

图 2:SmartFusion2 入门套件。

该入门套件包含一个系统级模块 (SOM),其中包含带有相关存储器和时钟的 Microsemi SmartFusion2 FPGA SoC 器件,以及一个承载原型设计区域、电源转换器和电源管理 IC 的 SmartFusion2 基板,该入门套件提供了一个完整的平台开始您的第一个设计。

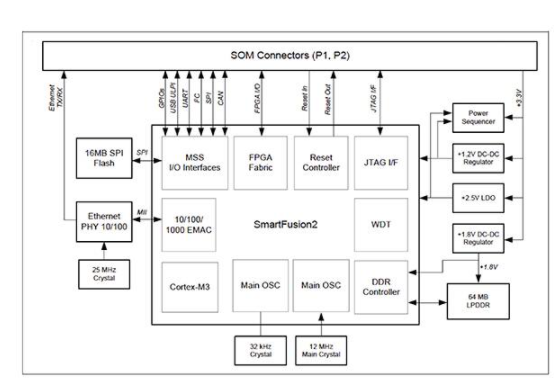

FPGA SoC 器件具有 32 位 ARM® Cortex®-M3 微控制器内核,在 FPGA 架构中实现为微控制器子系统 (MSS)。它支持 64 MB DDR 内存和 16 MB 闪存,并且能够运行高达 142 MHz。图 3 显示了 SmartFusion2 SOM 的功能框图。

图 3:SmartFusion2 系统级模块的功能框图。

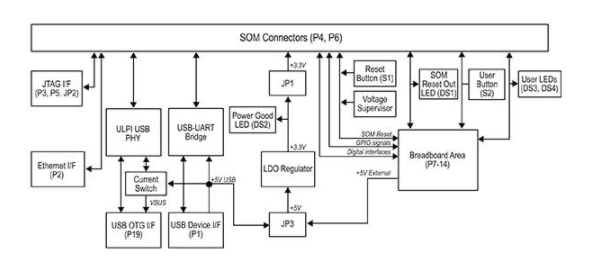

SOM 还包括一个 JTAG 接口、一个看门狗定时器、一个以太网接口以及大量 GPIO 和串行(I 2 C、CAN、SPI 和 UART)接口。基板连接和用户 I/O 功能的全部范围如图 4 所示。FPGA 架构的大小取决于模型,范围从 6060 到 56520 个逻辑元件。SoC 代码运行 uClinux 内核,通过提供对所有 Linux 工具(包括 SSH、FTP 和 Telnet 等网络实用程序)的访问,进一步帮助开发过程。

图 4:SmartFusion2 基板功能框图。

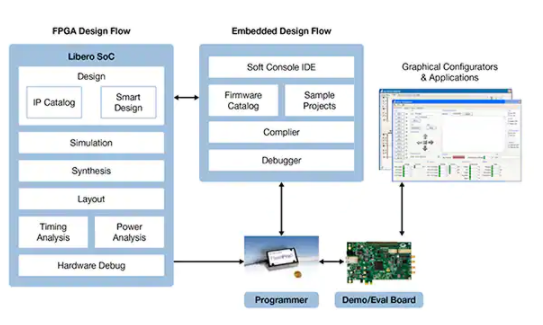

在对 FPGA SoC 进行编程时,Microsemi 的设计流程工具Libero可从 Microsemi 网站免费下载。套件中还包括作为 Libero 项目设置的完整 FPGA SoC 和电路板。Libero 将 FPGA 设计的设计流程与嵌入式应用程序开发集成在一起,如图 5 所示。

图 5:Libero 将传统的 FPGA 设计流程与微控制器固件开发集成在一起。

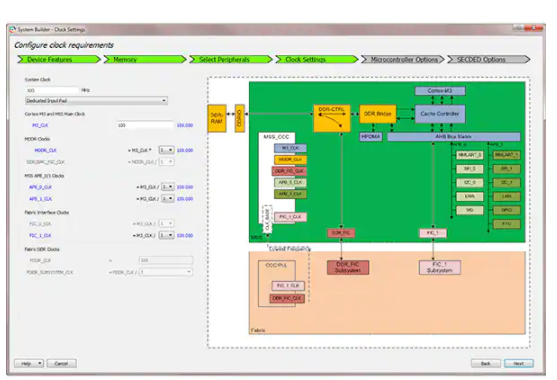

Libero 快速入门指南很好地介绍了使用 Libero 和整个设计流程。Libero 的一个关键部分是 System Builder 向导(图 6),它通过提出一系列问题来帮助开发人员进行架构设计过程,这些问题有助于塑造基本系统要求、配置选项,并在需要时向架构添加额外的外围设备。

图 6:Libero System Builder 向导 - MSS 中时钟功能的示例设置。

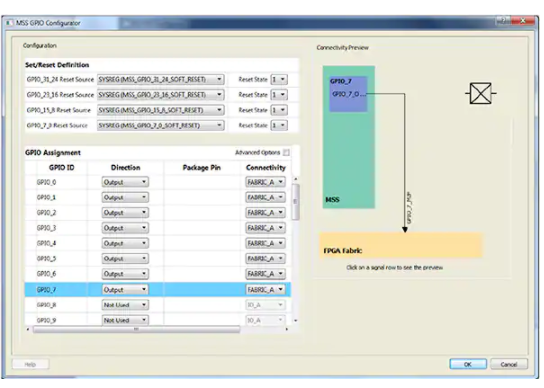

与传统的开发实践保持一致,“Hello World”第一程序的现代解释是通过闪烁的 LED 设计项目实现的。在本教程中完整记录,该文档指导工程师完成设计流程以实现此基本设计功能。图 7 是本教程的屏幕截图,突出显示了将输出信号分配给指定的 GPIO 引脚,该引脚在基板上连接了一个 LED。

图 7:闪烁 LED 示例中的 GPIO 引脚分配。

结论

FPGA 在原始计算能力、设计灵活性和每瓦性能方面可为开发人员提供很多帮助。以前被视为程序复杂、耗电大且价格昂贵的设备,随着越来越多的商业应用利用其广泛的功能,它们在最近已经成熟了很多。众所周知,在工程师创建复杂的神经网络设计之前,有一个合理的学习曲线。但是,由于本文中描述的开发工具的可用性,迈出第一步变得容易得多。

-

利用可定制微控制器优化算法设计2008-09-27 4014

-

基于8位微控制器体系架构的设计研究2011-04-15 2496

-

针对微控制器应用的FPGA的实现2012-08-20 2550

-

怎么通过FPGA实现微控制器?2019-03-22 3535

-

如何将微控制器与FPGA连接?2020-03-25 2307

-

请问如何实现微控制器与FPGA的接口设计?2021-05-06 1824

-

针对微控制器应用的FPGA实现2011-11-29 533

-

通过架构改进提高微控制器处理效率2012-01-12 1247

-

基于FPGA中实现微控制器2017-09-07 801

-

微控制器的FPGA接口的设计与实现方案介绍2019-06-10 4788

-

微控制器和FPGA的配对或是你设计成功的关键2019-01-20 1430

-

TI C2000的数字电源系统的微控制器架构介绍2019-04-26 5430

-

基于FPGA 架构的微控制器子系统实现2023-03-24 835

-

汽车微控制器介绍2023-10-17 2302

-

FPGA 与微控制器优缺点比较2024-12-02 2282

全部0条评论

快来发表一下你的评论吧 !