芯和电子系统设计仿真云平台应对各种仿真挑战

描述

前言

复杂的设计和竞争的压力促使着电子开发者寻找新的具有竞争力的解决办法。其中一个重要的方面是把云计算的能力用于 EDA (电子设计自动化)工具,从而显著地增加了生产率。经过十余年的发展,芯和电子系统设计仿真“云平台”已经成功地应用云计算技术,帮助不同的芯片、封装、系统用户应对各种场景的仿真挑战。

市场概况

由于近十年来的一系列革新,IC设计的规模、复杂性和种类不断增加。同时,激烈的竞争压力也促使企业将所有的资金投入到最大程度,并把所有优秀的工程师都投入到生产中去。IT与CAD团队在有限的场地和条件下,不论企业的规模和资源如何,都很难满足工程师团队对仿真的要求。

一个解决工程效率受限的办法是把更多的工程师和工具集中在最重要的项目上,但是这样做会加剧计算能力上的不足。如果更多的工程师在同一规模的基础设施上运行更多的工具,那么将会造成更多的计算资源争夺,最后会降低工程效率。即便是在确认了基础架构存在问题的情况下,也没有几家公司有足够的资源来升级和开发其硬件环境,以应对日益增长的计算资源需求。即便是拥有大量资源的企业,也无法在短时间内得到新的硬件来满足市场的需求。 为了解决仿真计算资源的不足,行业内推崇的新解决方案是利用具备云计算能力的仿真工具。

芯片、封装、系统大规模仿真挑战

1. On-chip电磁仿真

以光芯片为例,当前主流的光芯片接口速率为单通道56Gbps,业界最先进的可达到112Gbps,相信随着工艺的进步和终端用户对数据吞吐的进一步需求,速率会更高。从无源参数提取的角度,这是个宽频的应用,最高的频率已经达到毫米波。在如此复杂的电磁环境下,寄生参数的特性具有频变的特性,同时为了满足仿真精度必须要包含空间的电磁耦合。这些需求给电磁仿真器提出了更高的要求。

更重要的是光芯片集成度越来越高,都在往SOC的方向去实现。根据我们实际项目的经验,四通道光芯片版图的尺寸为1至2平方毫米,随着通道数增多,则版图尺寸会进一步的增大。除了必要的电感和互联外,版图还包括了大量的高密度电容结构,这些结构将仿真的规模提高了一个数量级。在端口方面,普通版图的电磁仿真通常需要50个左右的端口,而光芯片需要应对的端口数量翻了几倍,最高甚至可以达到500个,求解未知量达几百万。这使得设计者在有限的硬件资源下很难快速得到精确的仿真数据。

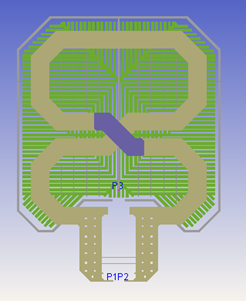

图1. 片上版图示例

2. 2.5D/3D 先进封装仿真

近年来,随着HPC、大数据、云计算、物联网、3D显示、网络交换等信息技术的发展,仿真对计算机性能的要求越来越高,比如高带宽,低延迟通信。

为了实现更高的带宽,DRAM的每个I/O引脚数据速率逐年都在增加。但由于DRAM晶体管技术的限制和高静态功耗,DRAM的每I/O引脚的数据速率不可能提高到10Gb/s以上。因此,需要一种新的解决方案来实现terabyte/s带宽的计算模块。

高密度片外存储器,如高带宽存储器(HBM)是最有前途的解决方案之一,它可以由4层DRAM组成,1024个硅通孔(TSV)I/O和底部的基本逻辑芯片组成。

另外,CPU的封装从早期的QPF、FCBGA到现在的先进封装,有了更多的变化。对于CPU芯片来说,随着工艺的发展,工程师大量利用硅载板或者TSV结构设计封装,如何能够准确高效的处理好多个信号之间的串扰问题,也是设计的重要一环。

以鲲鹏920为例,三颗裸芯组成的64核芯片,其中两颗为计算DIE,每颗含32个TSv110核,由4个核组成一个簇,8个簇挂在一个环状总线上,32MB的L3作为一个节点也挂在环上,同样的存控也作为一个节点挂在环上。三颗裸芯之间由 chip间总线实现互连。复杂的工艺以及众多的信号线需要一个强大计算能力的仿真工具,完成对信号和串扰的评估。

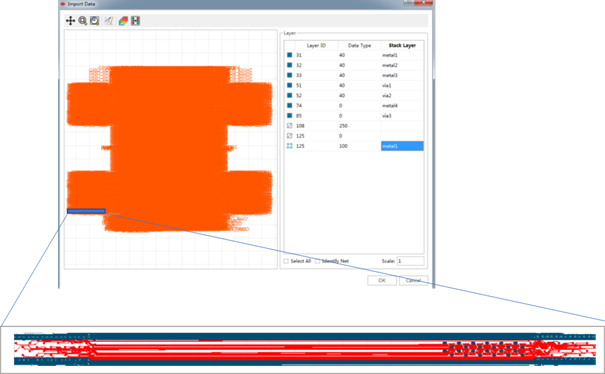

图2. 先进封装硅载板的“冰山一角”

3. Die-Interposer-Package联合仿真

随着摩尔定律逐渐接近物理极限,升级工艺技术所带来持续的产品PPA收益日渐受到挑战,从而驱使系统设计人员寻找异构集成技术。通过异构集成来实现3DIC和Chiplet的方案,为系统级功能集成和封装成本优化提供了额外机会,并开始在HPC、数据中心和高端路由器等领域广泛采用。但是,异构集成对设计人员提出了更高的技术挑战:大量高速SerDes和Memory互连线需要强大的全波三维电磁仿真引擎进行快速分析。传统RC提取工具无法满足精度要求,主流电磁仿真引擎工具又无法解决芯片纳米级别到封装厘米级别的跨尺度仿真问题以及异构集成超大规模问题。

如Chiplets包括多个芯片、硅通道、硅中介层、封装介质,芯片中的导体和硅通道之间的相互作用对电磁场求解器提出来更高的要求,它必须能够做超大规模的全波一体化分析。随着三维系统集成中I/O数目的增加,必须要考虑高密度集成在一起的TSV内部、TSV与有源电路之间以及TSV与TSV之间的串扰。高密度也使噪声耦合加剧。

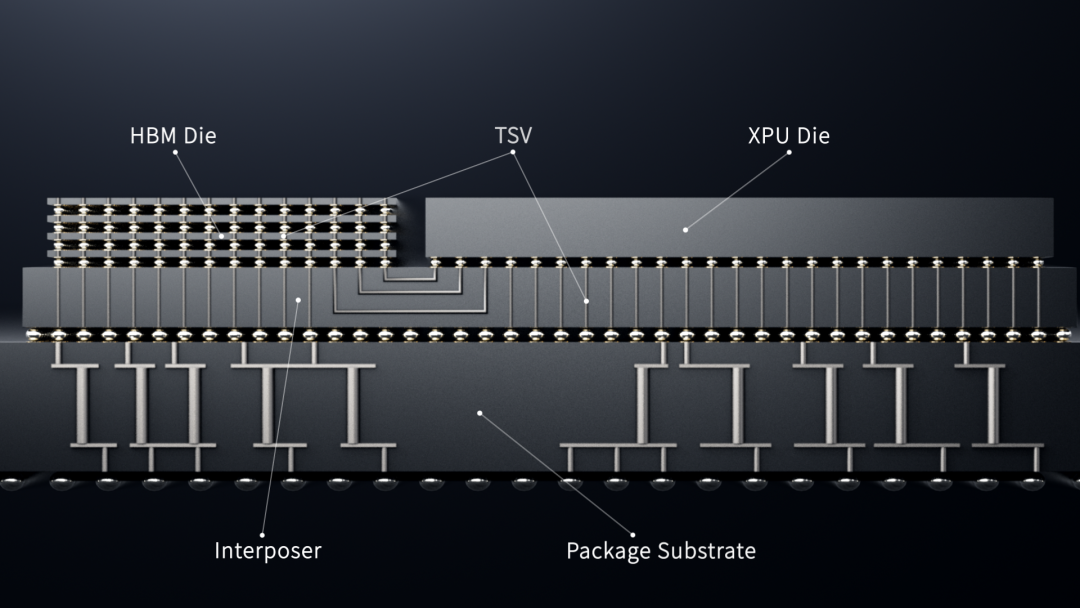

图3. 先进封装架构图

在超大规模一体化分析中,不可避免的问题是如何有效的分析不同尺度的结构,芯片-芯片或芯片-硅中介层的互联在10微米量级,芯片-封装的互联在100微米量级,而封装-母板之间在几百微米或毫米量级,这就对一体化的电磁场仿真提出来更多的计算能力要求。

芯片电子系统设计仿真“云平台”解决方案

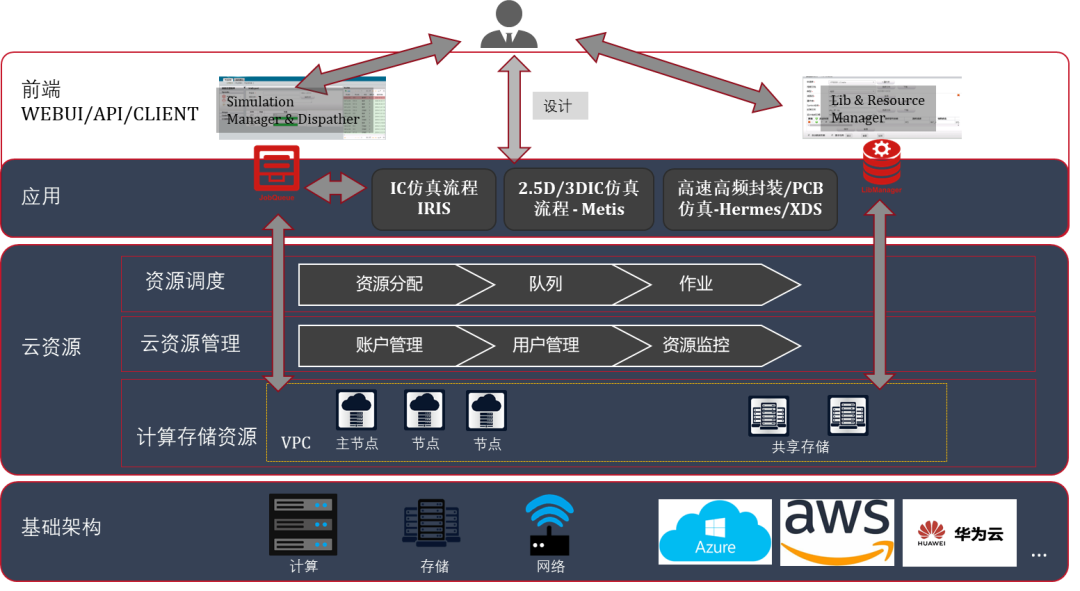

图4. Xpeedic EDA 云平台架构

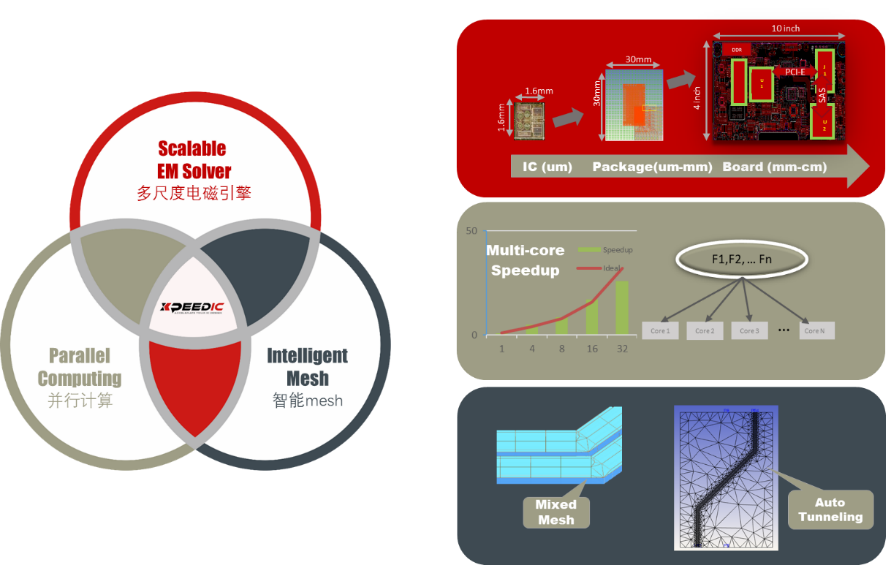

芯和电子系统设计仿真“云平台”解决方案集成核心差异化的电磁场仿真技术与软件、本地集群仿真技术、MPI仿真技术、云计算技术和分布式集群管理技术,使芯片、封装、系统设计大规模电磁仿真EDA的资源管理和资源统一调度使用成为了可能,通过使用优秀的管理系统和管理策略,达到资源统一分配和管理,不仅增加了各计算中的资源利用率,降低了计算中心的维护和部署成本,同时发挥芯和仿真软件的Intelligent Mesh智能mesh、Scalable EM Solver多尺度电磁引擎、Parallel Computing并行计算能力,为电子系统设计中的芯片,封装,PCB,系统进行大规模复杂电磁场仿真提供了可能。 芯和电子系统设计仿真“云平台”解决方案主要具有以下特点:

1.核心竞争力-差异化的电磁场仿真工具

图5. 核心技术

集成自主产权的多种尖端电磁场和电路仿真求解技术,提供从数字、模拟、射频领域,覆盖IC、封装到系统的仿真EDA解决方案:

芯片设计仿真产品线:为晶圆厂提供了精准的PDK设计解决方案, 为芯片设计公司提供了片上高频寄生参数提取与建模的解决方案;

先进封装设计仿真产品线:为传统型封装和先进封装提供了高速高频电磁场仿真的解决方案;

高速系统设计仿真产品线:为PCB板、组件、系统的互连结构提供了快速建模与无源参数抽取的仿真平台,解决了高速高频系统中的信号、电源完整性问题。

该平台提供了MOM和FEM两种电磁仿真求解器技术。首创革命性的电磁场仿真平台,突破了传统矩量法只能做电小尺寸如片上和封装的局限,解决了电小电大尺寸要不同技术的问题,用一个算法既能做芯片仿真,又能做PCB板级仿真,有效地提升电子产品的设计效率,缩短产品上市周期。

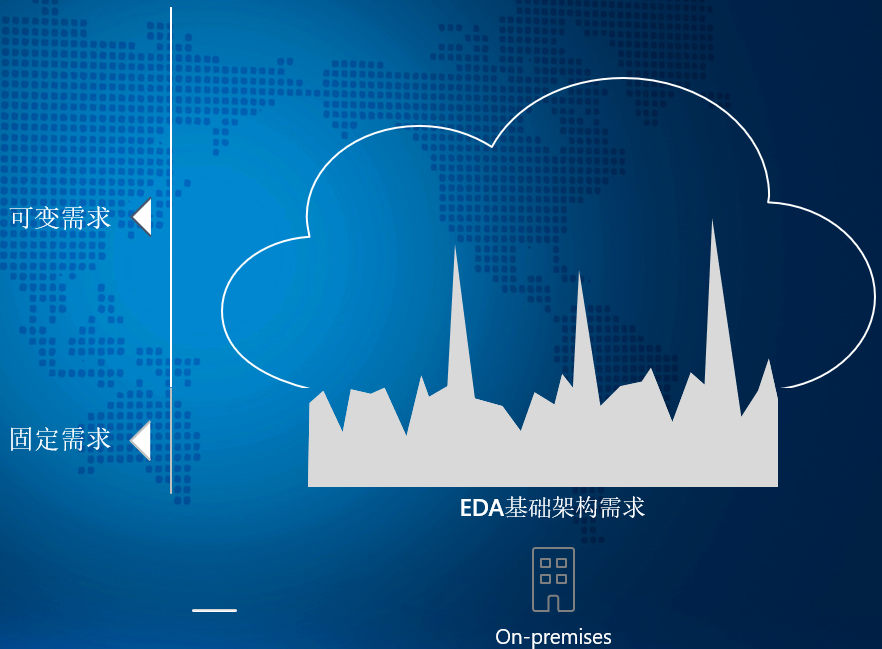

2.云计算

该平台集成了先进的多核多机分布式并行计算技术,能够最大程度地利用用户的硬件计算资源。同时该技术也很好地匹配了云计算平台,能利用云端的计算资源,帮助客户最大化地提升仿真效率。目前芯和已在亚马逊AWS和微软Azure云上建立了EDA仿真平台。

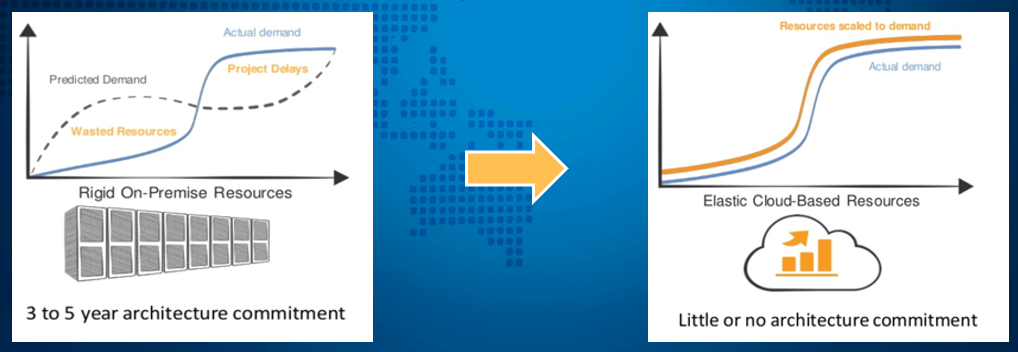

具备以下特点: 1,云的弹性为计算资源的可变需求提供了完美的适应;

图6. 弹性伸缩

2,基于云的 EDA 环境通过适应计算资源的按需使用模型来确保优化的业务敏捷性;

图7. 按需计算

3,更低的IT总支出

内部HPC:前期资本支出高,刚性

基于云的HPC:随用随付,灵活,需要资源的时候增加,不需要的时候减少

图8. IT维护灵活

总结

芯和电子系统设计仿真“云平台”解决方案集成了差异化的电磁场仿真技术与软件、本地集群仿真技术、MPI仿真技术、云计算技术和分布式集群管理技术,使芯片、封装、系统设计大规模电磁仿真EDA的资源管理和资源统一调度成为可能。“云平台”通过使用优秀的管理系统和管理策略,达到资源统一分配和管理,不仅增加了各计算中的资源利用率,降低了计算中心的维护和部署成本,同时发挥芯和仿真软件的智能mesh、多尺度电磁引擎、并行计算能力,加速电子系统设计中的大规模电磁场仿真。

审核编辑:刘清

-

FPGA仿真黑科技\"EasyGo Vs Addon \",助力大规模电力电子系统仿真2024-10-23 835

-

modelsim电子系统分析及仿真(第二版)配套光盘2014-06-18 12984

-

电子系统仿真与MATLAB2016-05-04 5310

-

ModelSim 电子系统分析及仿真2018-09-11 3664

-

汽车电子系统苛刻挑战谁来应对2019-05-13 1854

-

FPGA在车载电子系统的应用2019-07-25 3355

-

汽车电子系统面临的状况2020-06-24 3300

-

基于Multisim的电子系统设计、仿真与综合应用(第2版)2021-02-14 26872

-

电子系统设计所面临的挑战是什么2021-04-26 1912

-

电子系统模型分析与SYSTEMVIEW2011-06-15 1015

-

电子系统仿真与MATLAB_车晴2015-12-21 897

-

基于Matlab/Simulink的电力电子系统的建模与仿真2018-05-29 2616

-

芯和电子系统设计仿真“云平台”解决方案应对各种场景的仿真挑战2022-08-25 4300

-

基于MATLAB/Simulink的电力电子系统仿真技术2022-11-08 1253

-

元器件建模与仿真挑战2023-09-21 5960

全部0条评论

快来发表一下你的评论吧 !