可测性设计工具在可编程逻辑电路中的应用

电子说

描述

可测性设计工具针对集成电路生产测试需要,通过人工插入或工具自动综合生成测试逻辑电路,自动产生测试向量。可测性设计工具可以显著提升测试覆盖率,有效降低芯片在自动测试设备(Automatic Test Equipment,ATE)上测试的困难度及成本。

1.测试电路的自动生成

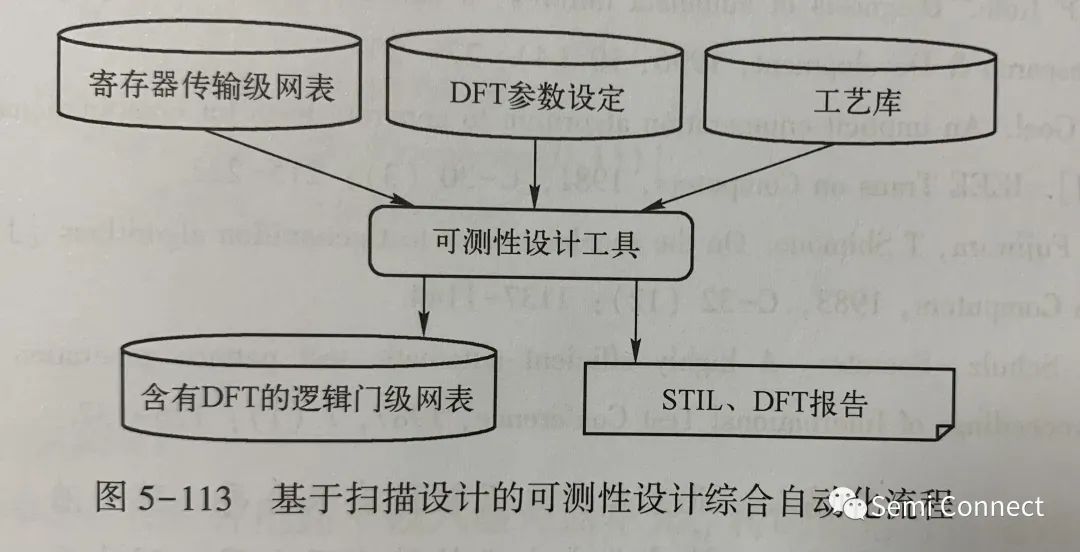

基于扫描设计(Scan-Based Design)方法是一种最常用的可测性设计方法。它把被测电路的寄存器转换成扫描寄存器,再将扫描寄存器连接成一条或多条的扫描链以传递测试信号。可测性设计的测试电路生成涉及一系列复杂的操作,通常需依靠自动化工具辅助完成。一个典型的基于扫描设计的可测性设计综合自动化流程如图5-113所示。

该流程包括下列几个主要步骤:

(1)将普通寄存器时序单元转换成扫描寄存器;

(2)检测被测电路是否符合一系列的DFT规则;

(3)对任何违反DFT规则的电路部分,进行自动修复或人工修复;

(4)根据DFT约束及目标设定,进行扫描链的链接并合成所需添加的逻辑。

测试电路的自动生成结果包括含DFT的逻辑门级电路网表、使用STIL(Standard Test Interface Language,标准测试接口语言)描述的DFT 工作情况以及DFT分析报告。

2.测量向量的自动生成及优化

基于DFT网表和STIL结果,自动测试向量生成工具可以自动产生芯片测试所需的测试向量信号。测试向量经过编码压缩、广播式压缩、逻辑变换压缩等方法优化后,在保证测试覆盖率的前提下可以减少测试数据数量、测试时间和必需的测试通道数。

D算法(又称多维通路敏化法)是第一个完备的ATPC算法,其基本思想是利用电路简化表和D向量传递,使故障沿着所有敏化通路传播至输出,通过兼容性检查得到最终的测试向量。针对大型组合电路中敏化通路选择的有效性,PODEM算法和FAN算法又对D算法进行了改进。后来的SOCRATES利用功能学习的方法提升了逻辑蕴含、通路敏化以及多路回退的效率。业界ATPG工具多采用基于类似SOCRATES的方法,并做了更进一步的改进。

除了上述的基于扫描设计DFT方法,业界还有几种不同的DFT解决方案。例如,LBIST(Logic Built -In Self-Test)将特殊的硬件或软件加入电路中,在不需要外在测试设备的条件下进行电路自测试。相对于LBIST,MBIST(Memory Built-In Self-Test)可用于存储器的自测试。

审核编辑:刘清

-

逻辑电路芯片-组合逻辑电路芯片-时序逻辑电路芯片2024-09-30 1155

-

什么是现场可编程逻辑阵列?它有哪些特点和应用?2024-05-23 2646

-

标准高速可编程阵列逻辑电路数据表2024-05-13 360

-

高性能冲击可编程阵列逻辑电路数据表2024-05-11 373

-

高性能Impact X可编程阵列逻辑电路TIBPAL16C数据表2024-05-07 388

-

什么叫可编程逻辑器件 可编程逻辑器件有哪些特征和优势?2023-09-14 4568

-

可创建小型组合与时序逻辑电路的PLU可编程逻辑单元2022-12-01 2675

-

实现可编程逻辑电路的三种主要技术2022-09-08 3208

-

如何使用可编程逻辑为按钮输入消抖2018-08-16 3442

-

如何使用可编程逻辑为按钮输入消抖:一个有效的消抖逻辑电路2017-09-06 10079

-

使用可编程逻辑为按钮输入消抖2017-04-18 3271

-

Xilinx可编程逻辑器件的高级应用与设计技巧绝版教程2012-02-27 17667

-

什么是可编程逻辑2009-05-29 3798

全部0条评论

快来发表一下你的评论吧 !