double tail comparator的debug过程(二)

描述

上一篇讲到了vref,这篇接着说。

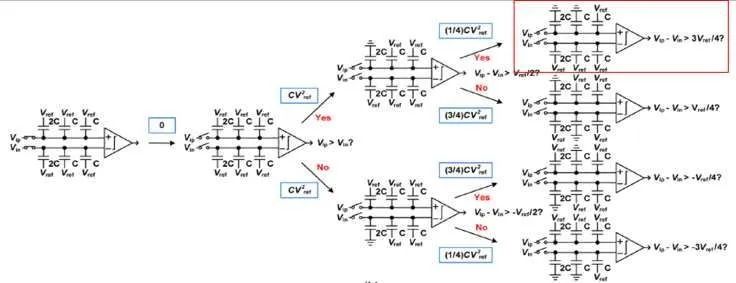

已知如果vip大于vin,那么一端连到vip的电容,另外一端连到vss的自然比较多,连到vref就少一些。对于vin,则是相反的,连到vref的比连到vss的多。于是,作者君画了下面这张图:

symbol画的比较大的电容,表示这个电容比较大。

跟上一篇的电路图相比,作者君多画了四个电容。

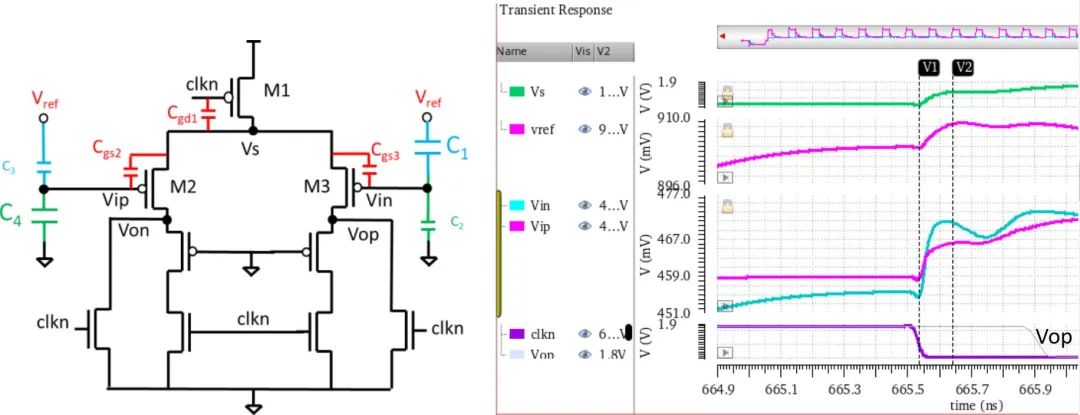

前面说到因为clkn导致的Cgs1把M2和M3的gate都往下拉了一点点,因此,通过较大的C1(vin和vref之间的电容)和较小的C3(vip和vref之间的电容),这个电容之间拉扯的动作影响到了vref。所以我们看到的右边第二行vref,也被拉下来了一点点。

vref自然是有个LDO来提供精准的0.9V的。现在vref被拉下来一点点,LDO(或者是buffer)必然会相应这个变化,于是,我们在v1和v2之间看到第二行的vref有个上升的动作。于是,通过C1和C3,vin和vip也跟着往上走。但是,为什么蓝色的vin上升得比较快呢?想到高频情况下,电容的等效阻抗1/cs跟电容的值成反比。于是vin连到vref的C1等效阻抗比较小,而vip连到vref的C3等效阻抗比较大。所以,可以解释vin的快速上升过程。

写到这里,大家自然可以想到,如果让尝试vref的LDO(或者是buffer)的负载电容大一些,是不是可以减小这个过冲的幅度呢?当然是可以的,作者君把负载电容从10pF增大到50pF,也可以跟前文讲的减小M1一样,得到正确的波形,而且不牺牲反应速度。(牺牲的自然是电容的面积了……)

或者不那么极端,稍微减小一点M1,然后同时增大负载电容,搭配起来使用,其实也不错。

讲到这里其实差不多可以完结撒花,不过作者君还想再说完。有兴趣的读者可以接着看下去。

说一个跟vref和capacitor array有关的东西:

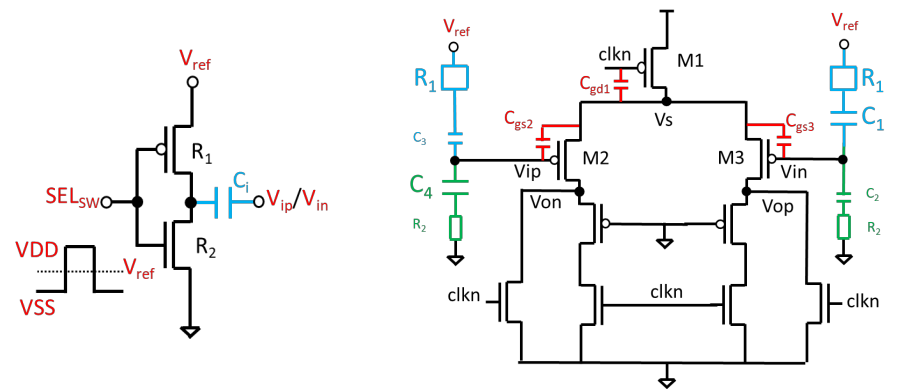

左图是每个电容的开关,右图是加上了开关的等效电阻

Capacitor array每个电容的开关如左图,输入在vdd和vss之间,所以对于上面的pmos来说,最大的vgs是vref-0也就是vref,下面的nmos的最大vgs是vdd-0也就是vdd。所以等效电阻,上面的pmos的R1大于下面的nmos的R2.于是作者君就在comparator的第一级画上了这两个R。

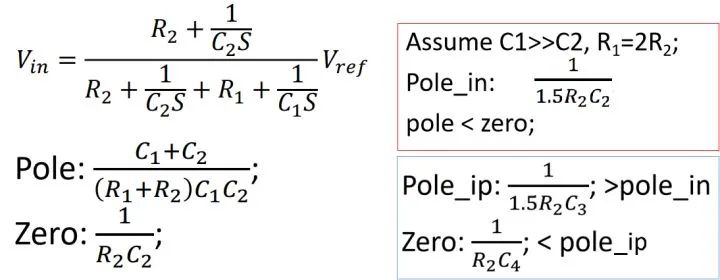

简单算一下从vref到vin或者vip的传输函数:

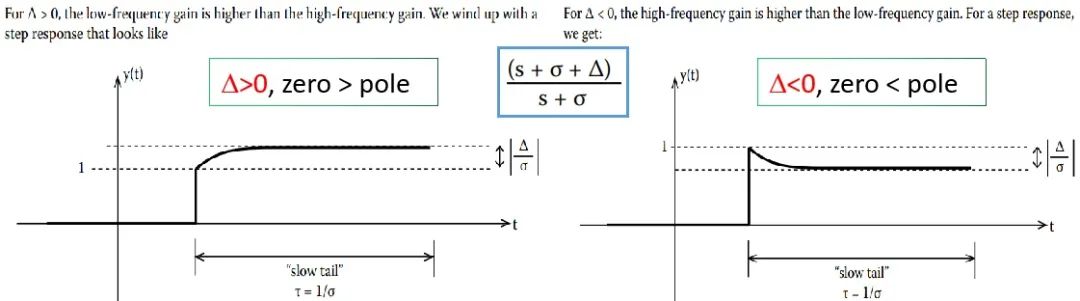

所以vin和vip两边,一个是pole小于zero,一个是pole大于zero。对于比较接近的doublet来说,用step response解释就是:

到这里也就解释了为什么过了图2的v2那条线之后,vin和vip的差距一度很大。

审核编辑:汤梓红

-

tail实时滚动显示log文件内容2019-07-09 2622

-

Implementing Double Data Rate2009-05-14 614

-

DEBUG程序的使用2008-09-28 7858

-

Dual Comparator Forms Temperat2008-11-24 1918

-

Comparator/DAC Combinations So2009-05-06 2038

-

LTC1540-Nanopower Comparator w2010-11-28 2194

-

基于Tail Fit算法的抖动分离2011-10-19 1040

-

Linux中tail与cat的区别2020-03-15 10305

-

结合搜索与Double DQN的非完备信息博弈算法2021-03-24 1213

-

AD45048:Rail-Tail在ADSL线驱动数据Sheet上运行.2021-04-16 621

-

配置VScode编译、调试STM32(二)Cortex-Debug插件2021-12-01 1794

-

HT8 MCU Comparator应用须知2022-06-09 770

-

如何在Intellij IDEA中使用好Debug2022-07-29 1948

-

double tail comparator的debug过程(一)2022-08-27 1793

-

单片机Debug与仿真区别2024-12-19 1812

全部0条评论

快来发表一下你的评论吧 !