物理设计工具的作用 利用仿真退火算法求解布局问题的流程

电子说

描述

物理设计工具的作用是采用自动布局布线技术或人工编辑的方法实现集成电路的版图设计。

自动布局布线通常分为布局规划(Floor Planning)、物理布局(Placement)、时钟树综合(Clock Tree Synthesis,CTS)、物理布线(Routing)等几个步骤。

布局规划在一定几何约束条件下,确定芯片面积及优化模块形状,决定标准单元、I/O Pad和宏单元的位置。常用的布局规划算法有布局尺寸变化算法、基于群生长摆放模块的方法、仿真退火迭代算法,以及将问题映射为等式集合进行解析求解的方法等。

物理布局又称为总体布局和详细布局,是指将标准单元摆放到版图核心区域的单元行上且满足设计规划的合理位置,使得芯片线长、时序、拥挤度、功耗等多个性能目标得到最优化。布局问题属于非确定性问题,很难找到一个多项式时间复杂度算法来得到最优解。在实际应用中通常寻求可行解来作为最优解的近似。常见的解决布局问题的算法可以分为图论算法(深度优先搜索、关键路径等)、确定性算法(线性规划、非线性规划、动态规划等)、随机算法(仿真退火等)3种。

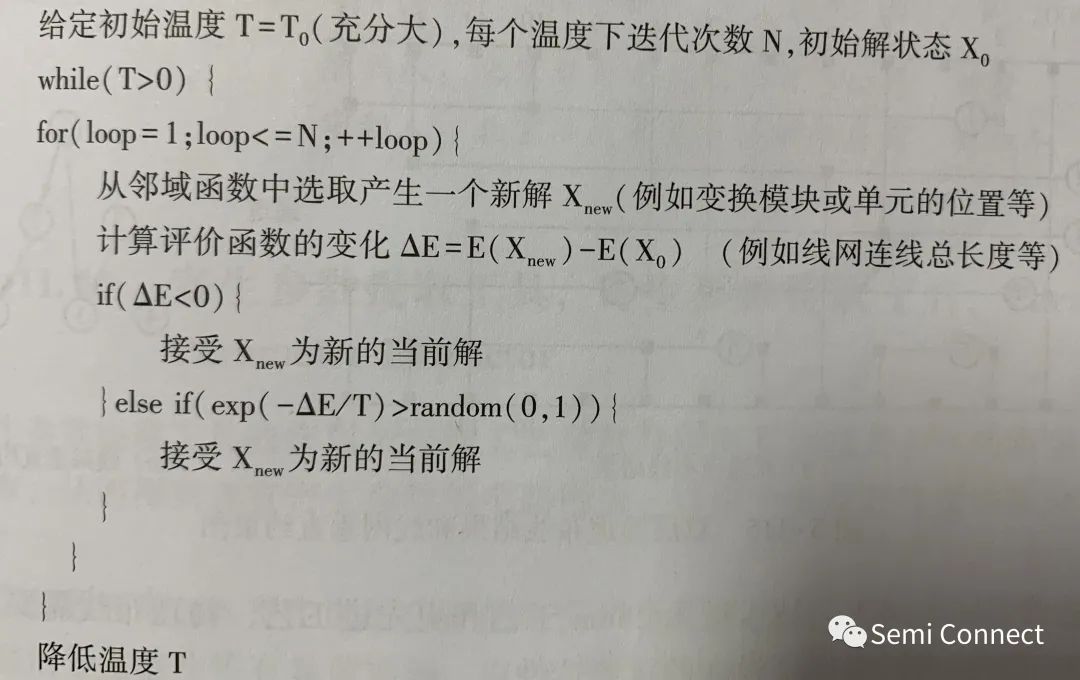

利用仿真退火算法求解布局问题的流程如下。

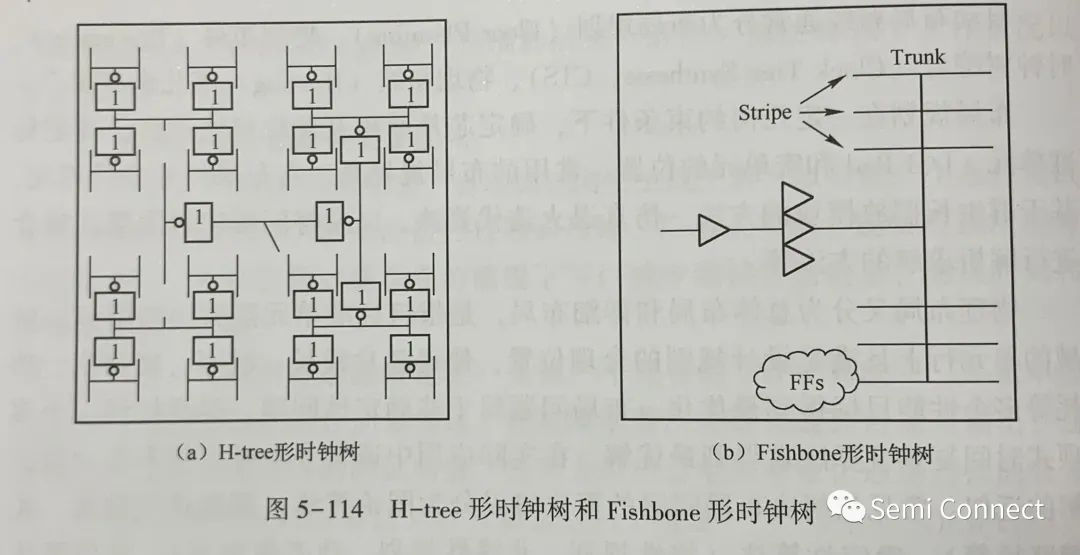

时钟树综合在时钟电路中插入缓冲器单元,将时钟信号传递到各个同步单元(触发器等),其优化目标在于尽量减少时钟路径延迟和时钟偏差。常见的时钟树综合算法有H- Tree 算法、Fishbone算法等,如图5-114所示。为了减少时钟偏差和受参数变化的影响,高性能的时钟系统设计还会采用网形(Mesh)结构,但同时也会占用更多的布线资源和面积。

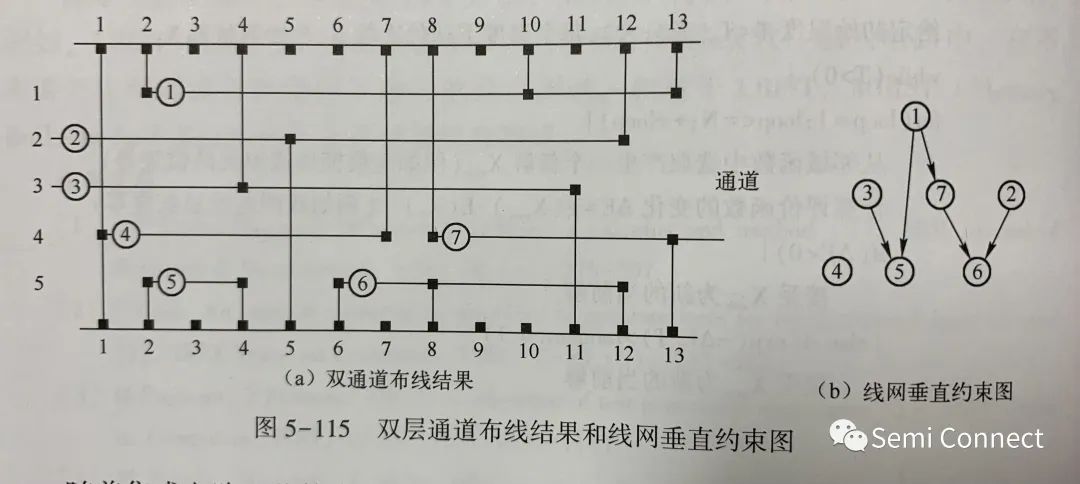

物理布线阶段分为总体布线和详细布线两个步骤:总体布线把网线合理地分配在合适的布线区域,尽量避免局部拥挤;详细布线实现线网通过布线层连线和通孔的具体连接,避免线网的短路、开路错误。根据布线区域和线网端点在区域中的分布情况有可以把详细布线分为通道布线、开关盒布线和区域布线。双层通道布线结果和线网垂直约束图如图5-115所示。

随着集成电路工艺技术进入28nm工艺和更先进工艺,物理布线需要支持多重曝光工艺技术,以保证设计的可制造性。

在集成电路的版图设计中,人工编辑主要依靠版图编辑工具。版图编辑工具提供一个以多边形为基础的二维几何图形创建与编辑环境,根据集成电路版图的特点及设计规则提供交互式的编辑与操作功能,最终以GDS或者OASIS等格式输出物理版图。版图编辑工具的基本功能如下。

(1)支持层次化编辑。

(2)与工艺绑定,并以一定的颜色、线型和填充方式区分不同的工艺层。

(3)支持矩形、多边形、路径等基本图形的创建、缩放、拉伸等。

(4)采用参数化单元(Parameterized Cell),减少重复输入。

随着集成电路设计方法学的发展,对版图编辑工具的要求也越来越高,主要体现在以下方面。

(1)与电路图的交互,由此产生了电路图驱动版图(Schematic-Driven Layout,SDL)和约束驱动版图(Constraint Driven Layout,CDL)两项技术。

(2)模拟和数字集成电路的融合,衍生出模拟电路的自动布局和自动布线技术。

(3)设计规模的急剧膨胀对工具效率提出更高要求,催生快速显示、多线程查询等技术。

(4)工艺技术的发展需要新的版图编辑技术,例如鳍式场效应晶体管(FinFET)的设计需要多格点对齐技术等。

审核编辑:汤梓红

-

VirtualLab Fusion应用:光导布局设计工具2025-02-21 810

-

VirtualLab Fusion应用:使用1D-1D EPE的光波导布局设计工具2025-02-24 686

-

HFSS 仿真算法及其应用场景详解:有限元算法、积分方程算法、PO算法2019-09-20 7428

-

怎么用模拟退火算法求全局最优解?2019-09-29 4049

-

基于模拟退火结合粒子群算法介绍2021-12-29 1518

-

基于遗传算法和模拟退火算法的TDOA定位技术2009-04-20 895

-

可支持任意流程的微机电系统设计工具技术2009-11-16 708

-

基于序列对和模拟退火算法的布局问题研究2010-02-22 1212

-

基于LabVIEW仿真实现TSP问题的模拟退火算法2011-09-09 1341

-

模拟退火算法及其在求解TSP中的应用2016-07-20 1108

-

基于退火算法的非合作对策求解2017-11-23 584

-

如何使用禁忌退火粒子群算法解决火力分配的问题2019-11-15 1279

-

结合模拟退火算法和单亲遗传的改进求解算法2021-06-29 877

-

【优化选址】基于模拟退火结合粒子群算法求解分布式电源定容选址问题matlab源码2022-01-07 1054

-

FL7701 设计工具流程2022-11-15 469

全部0条评论

快来发表一下你的评论吧 !