触发器的种类与触发方式

描述

你知道吗?计算机和计算器使用触发器来进行记忆。一定数量的触发器组合将产生一定数量的内存。触发器是使用逻辑门形成的,而逻辑门又由晶体管制成。

触发器是电子设备内存中的基本构建块,每个触发器可以存储一位数据。触发器有两个稳定状态,因此它们是双稳态多谐振荡器,两个稳定状态分别是高(逻辑 1)和低(逻辑 0)。

之所以使用术语触发器,是因为它们可以在控制信号的影响下在状态之间切换,即它们可以“翻转”到一个状态并“翻转”回另一个状态。其主要特点包括:

触发器是二进制存储设备,因为它们可以存储二进制数据(0或1)。

触发器是边沿敏感或边沿触发设备,即它们对转换敏感,而不是对时钟信号的持续时间或宽度敏感。

也被称为信号变化敏感器件,即时钟信号电平的变化会带来触发器输出的变化。

工作方式取决于时钟脉冲。

也用于控制数字电路的功能,因为可以根据状态改变数字电路的操作。

触发器的种类

一些最常见的触发器包括SR触发器、D触发器、JK触发器和T触发器,下面分别来介绍下。

1、SR触发器

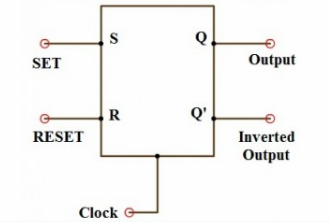

SR触发器是所有触发器中的基本触发器,所有其他触发器都是在SR触发器的基础上开发的。SR触发器如下图所示:

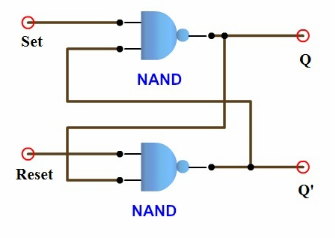

SR代表SET和RESET,这也可以称为RS触发器。不同的是RS是反相SR触发器。任何触发器都可以使用逻辑门构建。使用NAND和NOR门,因为它们是通用门。

下面是使用NAND门的SR触发器。

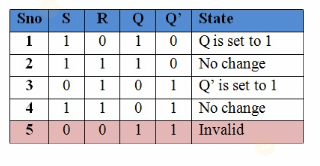

SR触发器的真值表:

工作过程:

从上面的真值表可以清楚地看出,SR触发器将在四个条件下置位或复位。

对于最后一个条件,它将处于无效状态。

当S=1且R=0时,SR触发器将被设置,如果S=1且R=1,则触发器会记住先前的状态。

当S=0且R=1时,触发器将被复位,如果S=1且R=1,则它会记住之前的状态。

但是当两个输入都为零时,SR触发器将处于不确定状态,其中Q和Q'将相同,这是不允许的。

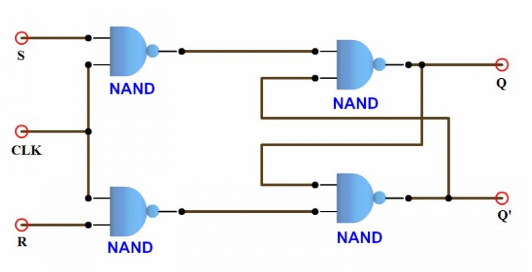

通过向现有触发器添加门额外的门来避免这种不确定状态。这称为时钟或门控SR触发器,这仅产生高时钟脉冲的输出。以下是使用NAND门的时钟SR触发器的电路:

2、D触发器

在SR触发器中发生了一个不确定的状态,这可以通过使用D触发器来避免。这里D代表“数据(Data)”。它由SR触发器构成,其中计时SR触发器的两个输入 (S&R) 连接到反相器。

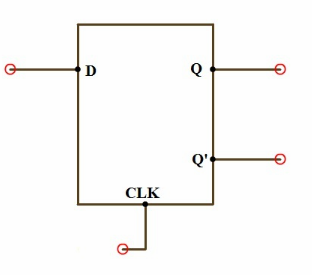

D触发器是使用最广泛的触发器之一,它有一个时钟信号(Clk)作为输入,数据(D)作为另一个输入。有两个输出,这些输出相互补充。D触发器的符号如下图所示。

真值表图如下:

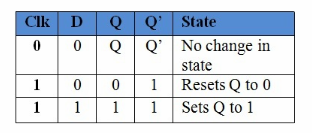

使用NAND门的D触发器如下图所示:

工作过程:

D触发器将根据时钟信号工作。

当时钟为低电平时,触发器的输出不会发生变化,即它会记住先前的状态。

当时钟信号为高电平并且在其数据引脚上接收到任何数据时,它会改变输出状态。

当数据为高时,Q复位为0,如果数据为低,Q被设置为0。

可以使用D触发器构建主从D触发器。

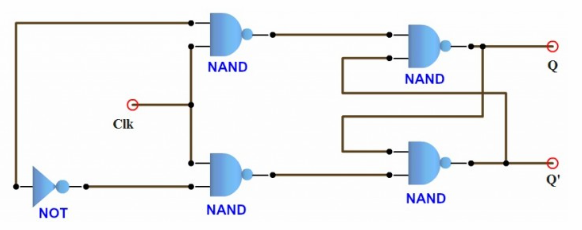

3、JK触发器

JK触发器以发明IC的电气工程师Jack Kilby的名字命名。

JK触发器是对SR触发器的修改。其中J输入类似于SR触发器的置位输入,而K输入类似于SR触发器的复位输入。SR触发器 (S=R=1) 中不允许的条件J=K=1被解释为切换命令。

在JK触发器中,共有:

两个数据输入J和K。

一个时钟信号输入 (CLK)。

两个输出Q和Q'。

JK触发器的符号如下所示:

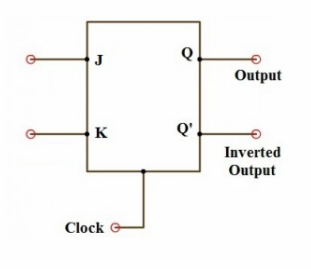

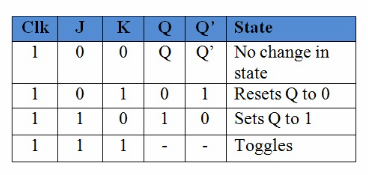

真值表图如下所示:

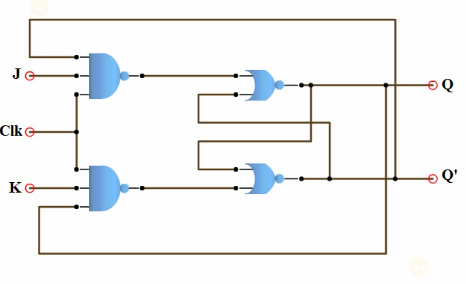

使用门的JK触发器的电路如下所示,它类似于修改后的NAND SR触发器:

工作过程:

当 J为低且K为低时,Q返回其先前的状态值,即它保持当前状态。

当J为低而K为高时,触发器将处于复位状态,即Q=0,Q'=1。

当J为高而K为低时,触发器将处于置位状态,即Q=1,Q'=0。

当J为高且K为高时,触发器将处于Toggle状态或翻转状态,这意味着输出将补充先前的状态值。

4、T触发器

T触发器也被称为“Toggle Flip – flop”,切换是在存在时钟输入信号的情况下将输出更改为先前状态的补码。

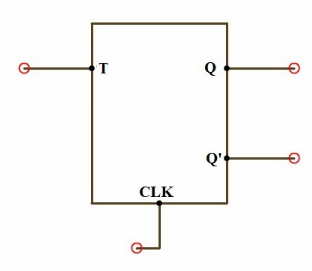

T触发器共有:

T输入。

一个时钟信号输入 (CLK)。

两个输出Q和Q'。

T型触发器的符号如下图所示:

其实可以通过使用任何其他触发器来构造一个T触发器。

SR触发器:通过将S 触发器的输出反馈连接到输入 (S & R)。

D触发器:将Q'连接到其D触发器的数据输入端作为反馈路径。

JK触发器:通过将JK触发器的J&K输入组合成单输入,可以设计出T触发器。

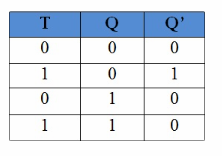

真值表如下图所示:

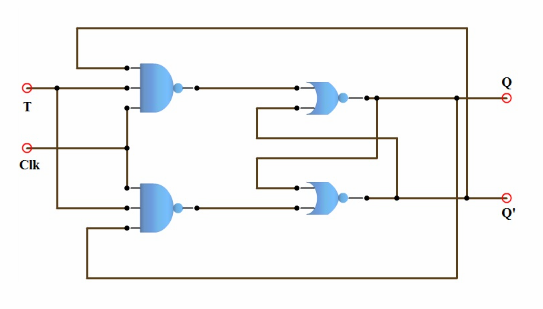

由NAND JK触发器制成的T触发器电路如下图所示。

工作过程:

当T输入为低电平时,T触发器的下一个状态与当前状态相同,即保持当前状态。

T=0并且当前状态=0然后下一个状态=0。

T=0并且当前状态=1然后下一个状态=1。

当T输入为高时,T触发器的下一个状态被切换,即它与时钟转换时当前状态的补码相同。

T=1并且当前状态=0然后下一个状态=1。

T=1并且当前状态=1然后下一个状态=0。

关于触发方式

触发器输出的变化可以通过输入信号的微小变化来完成,这种微小的变化可以在时钟脉冲的帮助下完成,而该时钟脉冲称为触发脉冲。

所以触发器也被称为“触发”,当触发脉冲施加到输入时,会导致输出发生变化。触发器是寄存器和计数器中的基本组件,它们以多位数字的形式存储数据。连接数个触发器构成时序电路,所有这些触发器都需要触发脉冲。施加到输入的触发脉冲的数量决定了计数器中的数量。

目前主有两种触发方式:电平触发和边沿触发。

电平触发

根据输入的有效电平改变输出状态的触发过程称为“电平触发”。电平触发有两种类型,它们是:

高电平触发。

低电平触发。

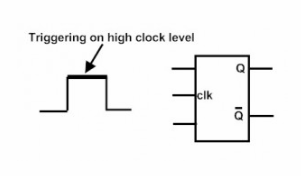

1、高电平触发

在高电平触发中,触发器的输出仅在其使能输入处于高电平状态即逻辑高或逻辑1时发生变化。高电平触发的符号表示如下所示:

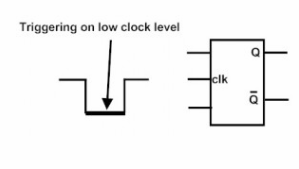

2、低电平触发

在低电平触发中,触发器的输出仅在其使能输入处于低状态即逻辑低或逻辑0时才发生变化。低电平触发的符号表示如下所示,低电平触发通常由时钟输入上的气泡标识。

边沿触发

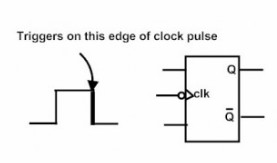

在边沿触发中,仅当输入出现在时钟脉冲的任一跳变时,输出才会改变,即从低到高(0 到 1)或从高到低(1 到 0)。

边沿触发也有两种类型,它们是:

正边沿触发。

负边沿触发。

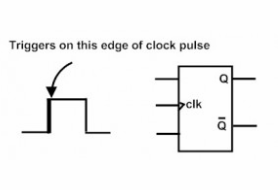

1、正边沿触发

在正边沿触发中,仅当输入处于时钟脉冲输入的正边沿时,输出才会改变,即从低到高(0 到 1)的转换。当需要触发器在低电平到高电平转换状态下响应时,使用正边沿触发方法。正边沿触发沿触发的符号表示如下所示。

2、负边沿触发

在负边沿触发中,只有当输入处于时钟脉冲输入的负边沿时,输出才会改变,即从高电平到低电平(1 到 0)的转换。当需要触发器在高电平到低电平转换状态下响应时,使用负边沿触发方法。负边沿触发的符号表示如下所示:

为什么说边沿触发优于电平触发?

最好使用边沿触发而不是电平触发。这是因为对于电平触发触发器的特定情况,电平触发可能会导致电路不稳定,其中在触发器输出发生变化的同时,时钟脉冲被提供给输入。从输出到输入的反馈会导致这种不稳定性。为了避免这种不稳定性,使用了边沿触发触发器。

触发器的应用

触发器的应用非常广泛,可以说在数字电路中很是常见,下面简单整理一些:

寄存器:由于触发器有两个稳定状态,所以将它们用于寄存器等存储元件中,用于数据存储。通常在计算机等电子设备中使用寄存器。

计数器:相互连接的触发器组用作计数器,对事件发生的增量或减量进行计数。

分频电路:触发器用作分频电路,将输入频率精确地分成一半。分频电路用于规范电子电路的频率。

数据传输:使用移位寄存器(一种特殊类型的寄存器)将数据从一个触发器传输到另一个触发器,它们以特定的顺序连接。

总结

简单来说,触发器就是同步时序电路的构建块。它有两个稳定状态,可以存储一位信息。触发器将具有时钟信号,它们的状态根据时钟脉冲而变化,这些设备将具有两种状态和一条反馈路径。

需要注意的是,触发器是边缘敏感的,当时钟信号从低到高或从高到低转换时,它们将改变它们的状态。在时钟信号从0到1或1到0的转换之后,即当时钟处于恒定的0或1时,即使输入发生变化,状态也保持不变。

-

t触发器变为d触发器的条件2024-08-22 4597

-

同步触发器和边沿触发器的区别2024-08-12 4006

-

t触发器与d触发器的区别和联系2024-08-11 7447

-

触发器的原理:RS触发器和T触发器2024-02-05 6234

-

触发器的三种触发方式原理图2024-01-26 16457

-

触发器的基本性质 触发器的触发方式分为哪三种2024-01-23 5732

-

rs触发器的触发方式有哪几种2024-01-15 4287

-

什么是触发器?触发器的作用是什么?触发器的触发方式2023-08-24 10638

-

电平触发器,脉冲触发器和边沿触发器的触发因素是什么2021-02-11 11131

-

触发器的常用触发方式2019-07-15 42985

-

什么是边沿触发器_边沿D触发器介绍2018-01-31 73429

-

同步触发器的触发方式和空翻问题2010-08-18 22969

-

施密特触发器,施密特触发器是什么意思2010-03-08 2383

-

触发器PPT2008-10-20 801

全部0条评论

快来发表一下你的评论吧 !