基于inFO的AiP天线的FOWLP技术分析

RF/无线

描述

高频率造成天线有源化趋势,手机侧的AiP天线应运而生

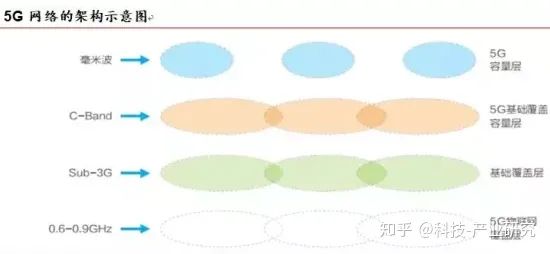

与2G/3G/4G移动网络相比,5G网络将在更高的频段C-Band(3.7-4.2GHz)和毫米波(24.25GHz-52.6GHz)上部署,而更高频率的信号就意味着更大的馈线损耗,根据硕贝德测算,传统4G手机射频前端的馈线损耗只有1dB不到,但是在毫米波频段线损在2-4dB。

因此,5G时代将天线与射频前端进一步集成就成为大势所趋,而这一集成趋势在宏基站侧就体现为基于Massive MIMO的AAU,在室分基站侧就体现为由DAS向数字化室分的演进,在手机侧就体现为AiP(Antenna in Package)天线的诞生。所谓AiP天线是基于封装材料与工艺,将天线与芯片集成在封装内,实现系统级无线功能的技术。AiP技术顺应了硅基半导体工艺集成度提高的趋势,兼顾了天线性能、成本及体积,代表着近年来天线技术的重大成就及5G毫米波频段终端天线的技术升级方向。

FOWLP有望成为AiP天线的主流技术工艺

尽管目前AiP的实现工艺主要有LTCC(低温共烧结陶瓷)、HDI(高密度互联)及FOWLP(晶圆级扇出式封装)三种,但是我们认为,基于更高的集成度、更好的散热性、更低的传输损耗等优势,结合目前的产业化进度,FOWLP有望成为AiP天线的主流技术工艺。

FOWLP是fan-out Wafer Level Package的缩写,其中WLP(晶圆级封装)是以BGA(Ball Grid Array)技术为基础,以wafer为加工对象,在wafer上同时对众多芯片进行封装测试,最后切割成单个器件,可直接贴装到基板或者PCB板上的封装方案。WLP由于不需要中介层(interposer)、填充物(underfill)与导线架,并且省略黏晶、打线等制程,因此能够大幅减少材料及人工成本,此外,WLP大多采用RDL(重布线层)与Bumping(凸块)技术作为I/O排线手段,因此具有较小的封装尺寸和较佳电性表现等优势,多应用于注重轻薄、节能的3C芯片中。

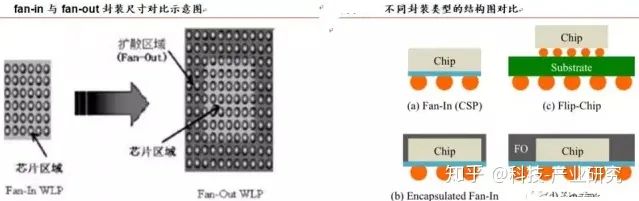

WLP可分为fan-in(标准型扇入式)及fan-out(扩散性扇出式)两种,其中fan-in是在wafer未进行切片前对wafer进行封装,之后再进行切片分割,完成后的封装大小和芯片尺寸接近。而fan-out则是基于wafer重构技术,将芯片重新布局到一块人工晶圆上,然后按照与标准的WLP工艺类似的步骤进行封装,封装面积大于芯片面积。传统的WLP封装多采用fan-in形态,应用于pin(引脚)数量较少的IC芯片,伴随着IC引脚数目的增加,对锡球间距的要求日趋严格,加上PCB排线对于IC封装后尺寸以及引脚位置的调整要求,因此衍生出fan-out。

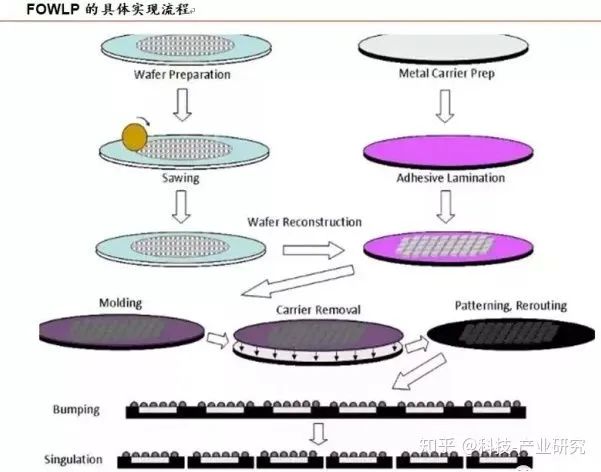

FOWLP的具体实现步骤如下图所示,第一步需要完成晶圆的制备及切割,即将晶圆放入划片胶带中,切割成各个单元,与此同时准备洁净处理后的金属载板;第二步将芯片从晶圆拾取并排布在金属载板上;第三步以模塑料(molding compound)密封载板完成制模;第四步从载板上移走已经成型的重建芯片;第五步在重分布层(RDL)上配置I/O连接;第六步在I/O连接口形成铜凸块;最后对已成型的塑封体进行切割。

由于FOWLP是从裸晶端点拉出所需电路到RDL层进而形成封装,因此在最终的产品形态中不存在封装载板,可以减少成本并降低芯片厚度,此外,由于RDL层有助于缩短互联电路的长度,可有效降低高频信号的传输损耗。

苹果A10处理器是FOWLP工艺大范围推广的催化剂

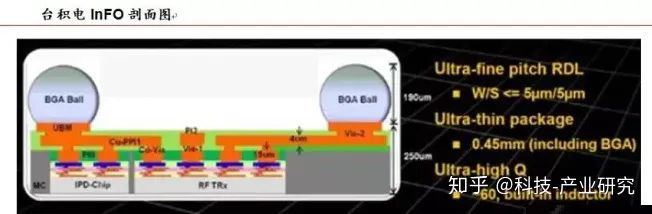

2009-2010年间Intel Mobile率先推动FOWLP在手机基带芯片的单芯片封装过程中得到应用。2014年台积电宣布其inFOWLP(integrated fan-out)进入量产准备,可实现封装厚度250um,RDL间距10um,从具体应用而言,台积电8mm x 8mm平台可用于射频和无线芯片的封装,15mm x 15mm可用于应用处理器和基带芯片封装,而更大尺寸如25mm x 25mm可用于图形处理器和网络等应用的芯片封装。

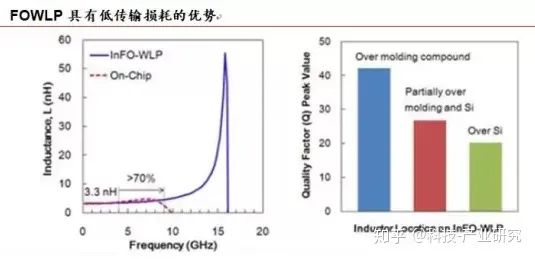

在台积电inFOWLP工艺中,铜互连形成在铝PAD上,应用于扇出型区域以制造出高性能的无源器件如电感和电容。以3.3nH的电感为例,根据麦姆斯咨询数据,65nm的CMOS采用on-chip封装其品质因子Q为12,而InFO封装则可达到峰值42。电感与模塑料越接近,损耗因子越小,Q值越高,由此也印证了如前所述的FOWLP的低传输损耗的优势。

2016年苹果首次在iPhone中采用了基于FOWLP工艺的处理器A10,根据Techinsights数据,由台积电代工的A10处理器基于16nm finFET制程工艺,采用inFO(integrated fan-out)封装工艺,使用了5-5µm、10-10µm和10-10µm三层RDL。在苹果和台积电的合力推动下,设备商Veeco、封装测试供应商Amkor、日月光、星科金朋、晶圆代工厂Global Foundries等均在2016年大力加码FOWLP相关技术、产品布局。

根据Yole数据,在苹果A10、A11处理器的带动下,2015-2017年全球FOWLP市场规模CAGR接近90%,于2018年达到约14亿美金规模,面对渐行渐近的5G时代,在高通、三星、华为海思等玩家陆续进入的过程中,FOWLP全球总产值有望在2022年超过23亿美金,2019-2022年间的CAGR接近20%。

硕贝德联合中芯长电已成功发布了基于inFO的AiP天线产品

19年3月19日中芯长电在CSTIC发布了世界首个超宽频双极化的5G毫米波AiP天线,该产品采用了基于FOWLP封装SmartAiP工艺技术,该工艺能够帮助客户实现24GHz-43GHz超宽频信号收发、达到12.5dB的超高天线增益、以及适合智能手机终端对超薄厚度要求等优势,并且有进一步实现射频前端模组集成封装的能力。

根据中芯长电讯,该工艺方案与领先的天线方案提供商硕贝德合作,现已获得中国和美国专利授权,可通过超高的垂直铜柱互连提供更强的三维集成功能,加上中芯长电成熟的多层双面RDL技术,结合晶圆级精准的多层天线结构、芯片倒装及表面被动组件,使得SmartAiP实现了5G天线与射频前端芯片模块化和微型化的高度集成加工。

编辑:黄飞

-

封装天线技术的发展动向与新进展2019-07-16 5086

-

封装天线技术发展历程回顾分析2019-07-17 3449

-

【微信精选】成本低、功耗低,Aip封装技术如何让毫米波雷达替代超声波成为可能?2019-10-13 2794

-

AIP封装EMI问题2020-05-15 2358

-

AIP1616产品技术参数2020-12-15 2703

-

什么是AIP? IAP的原理是什么?2021-12-15 1526

-

智能天线技术原理及应用分析2012-09-20 1967

-

你知道吗?台积电技术优势之一在于FoWLP封装2018-04-23 2553

-

基于封装天线(AiP)的过孔分析讲解2018-05-03 10250

-

采用封装天线(Antenna-in-Package,AiP)技术的雷达芯片2019-05-05 25435

-

天线为收发射频讯号的被动元件 逐渐由传统FPC变成AiP2019-05-06 2268

-

高频率造成天线有源化趋势,手机侧的AiP天线应运而生2020-09-02 3602

-

AiP技术扩展了毫米波雷达的应用2020-10-15 4672

-

面向 TSMC InFO 技术的高级自动布线功能2023-11-27 1519

-

从InFO-MS到InFO_SoW的先进封装技术2025-08-25 963

全部0条评论

快来发表一下你的评论吧 !