可编程逻辑电路—版图验证工具的作用

可编程逻辑

描述

版图验证工具的作用是检查版图是否满足设计规则、电气规则、版图与电路图是否一致等,对于降低设计失败的风险具有重要作用。

版图验证工具不仅要支持扁平化验证,而且要支持层次化验证。扁平化验证是版图验证工具的基础;层次化验证充分利用版图层次,可以有效避免重复报错和提高处理版图的速度。对于大规模版图,通常还采用并行技术以加速版图验证效率。

版图验证工具主要包括设计规则检查(Design Rule Check,DRC)、版图电路图一致性检查(Layout Versus Schematic,LVS)、电气规则检查(Electronic Rule Check,ERC)、版图比对检查(Layout Versus Layout,LVL)等。

1.设计规则检查(DRC)

版图设计必须遵循制造工艺的设计规则要求,因此设计检查主要包括连线宽度、连线间距、图形包含关系、金属密度、天线效应检查等。如果版图设计中违反了这些规则将导致制造失败,例如线条宽度过小可能导致断路。

DRC涉及的关键技术有层次处理和扫描线算法等。

层次处理技术是对版图原始层次进行调整,根据需要对版图图形进行投影或提升以提高DRC工具的性能。

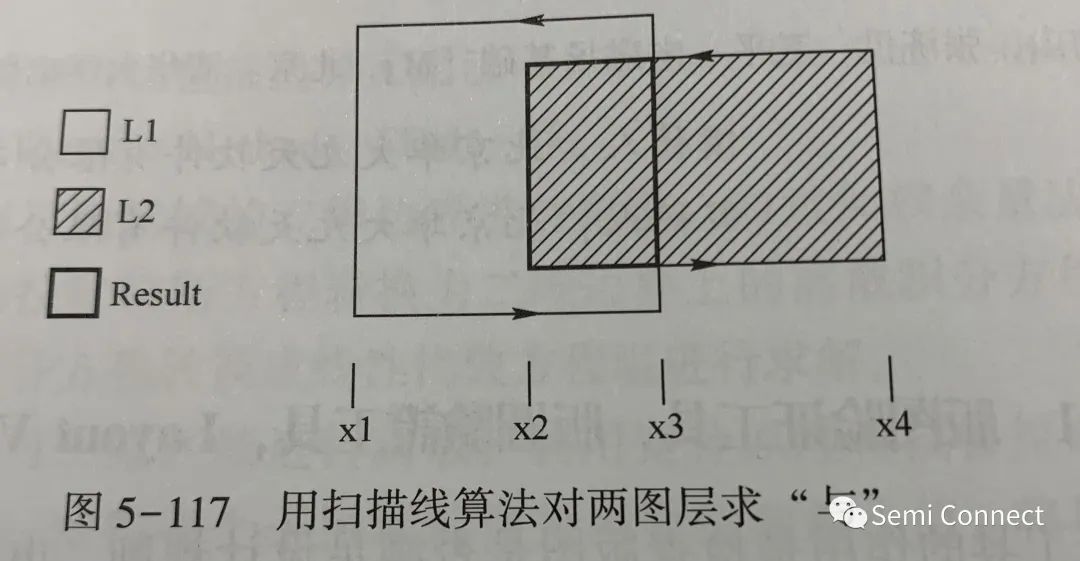

扫描线算法包括基于梯形的扫描线算法和基于边的扫描线算法。DRC技术通常采用基于边的扫描线算法。

边,即一条线段,用它的两个端点的坐标表示。基于边的扫描线算法的本质是将平面的二维几何问题转化成两个一维问题,包含以下几个步骤:

(1)确定当前扫描线的位置;

(2)加入当前扫描线上的新进边,与原有的边构成当前扫描线边集合;

(3)对当前扫描线边集合进行排序;

(4)遍历当前扫描线边集合,根据不同的命令进行相应的逻辑处理;

(5)删除当前扫描线上的离开边,并重新回到步骤(1)。

在图5-117中,L1和L2图层为输入图层,x1、x2、x3、x4为扫描线需要计算的位置,Result图层为结果图层。

2.版图电路图一致性检查(LVS)

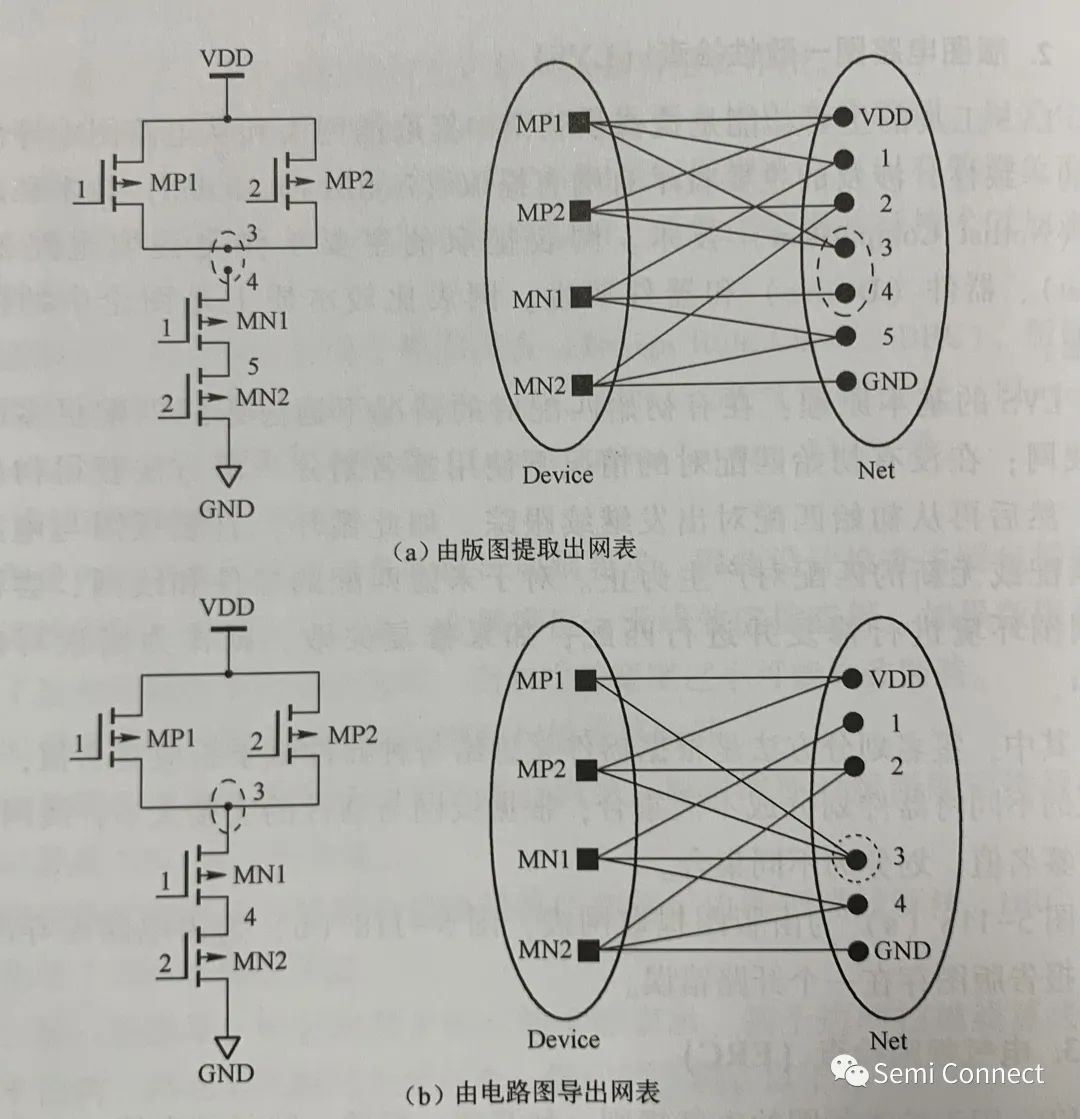

LVS工具的主要功能是检查从版图中提取的网表和从电路图中导出的网表的一致性,涉及的主要技术有网表提取(Netlist Extraction)技术和网表比较(Netlist Comparison)技术。网表提取的主要工作是提取电路的线网(Net)、器件(Device)和器件属性。网表比较本质上是图论中的图同构问题。

LVS的基本原理:在有初始匹配对的情况下通过跟踪匹配更多的器件或线网;在没有初始匹配对的情况下使用签名划分等方法获得初始匹配对,然后再从初识匹配对出发继续跟踪。如此循环,直至版图与电路图全部匹配或无新的匹配对产生为止。对于未能匹配的器件和线网,尝试根据其周围环境进行修复并进行匹配;如果修复失败,则作为错误写出至报告中。

其中,签名划分方法是根据器件给每种器件赋予相应签名值,根据签名值的不同将器件划分成不同集合;根据线网与器件的连接关系,线网也会被赋予签名值,划分为不同集合。

图5-118(a)为版图提取网表,图5-118(b)为由电路图导出网表,LVS报告版图存在一个开路错误。

3.电气规则检查(ERC)

ERC用于检查版图的电气规则,如开路、短路、路径检查等。ERC基于版图进行建成区,不需要电路图,可以快速检查并直观定位设计中存在的常见问题。通常ERC功能包含于LVS工具中。

4.版图比对检查(LVL)

LVL工具主要应用在两个方面:1)版图改版时设计者需要借助LVL工具查看修改前后的差异;2)制版时版图数据通常被扁平化,LVL工具用于比对版图扁平化前后的差异。

LVL检查涉及的关键技术有层次处理、扫描线算法、数据压缩、并行计算等。另外,由于涉及的规则比较少,可以针对不同类型的版图采用一些特殊的加速技巧。

工艺发展到40nm和更先进的工艺后,因线距变小,层厚度也变小,线与周围的环境以及线间耦合的影响变大,光学效应的影响也凸显出来。传统的版图验证工具所采用的二维检查技术已经不能满足检查需求,需要利用三维和光学分析技术以处理各种效应的影响,开发新的检查功能,例如模式匹配(Pattern Match)、双重/多重曝光(Double/Multi- pattern)、智能哑元填充(Smart Fill)等。

编辑:黄飞

-

逻辑电路芯片-组合逻辑电路芯片-时序逻辑电路芯片2024-09-30 1155

-

什么是现场可编程逻辑阵列?它有哪些特点和应用?2024-05-23 2645

-

标准高速可编程阵列逻辑电路数据表2024-05-13 360

-

高性能冲击可编程阵列逻辑电路数据表2024-05-11 373

-

高性能Impact X可编程阵列逻辑电路TIBPAL16C数据表2024-05-07 388

-

可编程逻辑阵列PLA内部逻辑结构示意2024-02-02 5259

-

可创建小型组合与时序逻辑电路的PLU可编程逻辑单元2022-12-01 2675

-

实现可编程逻辑电路的三种主要技术2022-09-08 3208

-

可编程阵列逻辑的构造及运用2020-06-19 3359

-

如何使用可编程逻辑为按钮输入消抖2018-08-16 3442

-

如何使用可编程逻辑为按钮输入消抖:一个有效的消抖逻辑电路2017-09-06 10079

-

使用可编程逻辑为按钮输入消抖2017-04-18 3271

-

什么是可编程逻辑2009-05-29 3798

全部0条评论

快来发表一下你的评论吧 !