CDC跨时钟域分单bit和多bit传输介绍

描述

多bit跨时钟域

(大疆2020数字芯片)下列关于多bit数据跨时钟域的处理思路,错误的有()

A. 发送方给出数据,接收方用本地时钟同步两拍再使用;

B. 发送方把数据写到异步fifo,接收方从异步fifo里读出;

C. 对于连续变化的信号,发送方转为格雷码发送,接收方收到后再转为二进制;

D. 发送方给出数据,发送方给出握手请求,接收方收到后回复,发送方撤销数据。

答案:A

解析:多bit跨时钟域不能简单使用打两拍,打拍后可能数据错乱;

CDC(Clock Domain Conversion)跨时钟域分单bit和多bit传输,其中:

1. 单bit(慢时钟域到快时钟域):用快时钟打两拍,直接采一拍大概率也是没问题的,两拍的主要目的是消除亚稳态;

其中:

(1)为了更长的平均无故障时间 MTBF( Mean Time Between Failures),需要配合一个 ASYNC_REG 的约束,把用作简单同步器的多个寄存器放入同一个 SLICE,以降低走线延时的不一致和不确定性。

(* ASYNC_REG = "TRUE" *) reg rst_reg_0;

(* ASYNC_REG = "TRUE" *) reg rst_reg_1;

(2)或者:直接在约束文件里进行约束

set_property ASYNC_REG TRUE [get_cells [list rst_reg_0 rst_reg_1]]

2. 单bit(快时钟域到慢时钟域):握手(脉冲展宽)、异步FIFO、异步双口RAM;快时钟域的信号脉宽较窄,慢时钟域不一定能采到,可以通过握手机制让窄脉冲展宽,慢时钟域采集到信号后再“告诉”快时钟域已经采集到信号,确保能采集到;

3. 多bit跨时钟域:异步FIFO、异步双口RAM、握手、格雷码;

(1)使用异步FIFO的IP

实际上是用 FPGA 内部的 BRAM 来搭建,所有的控制逻辑都在 BRAM 内部,是推荐的 FIFO 实现方式。

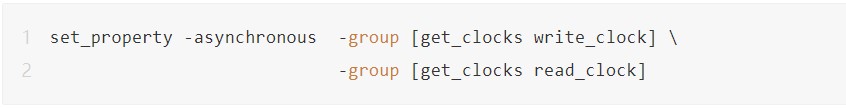

时序约束简单,进行时序例外约束,只需要 set_clock_groups 将读写时钟约束为异步时钟组即可,简单高效。

set_property -asynchronous -group [get_clocks write_clock] \ -group [get_clocks read_clock]

(2)自己写外部控制逻辑的FIFO

格雷码做异步 FIFO 的跨时钟域处理,计数器和读写控制逻辑在 BRAM 或者 RAM 的外部,除了代码的合理设计以外,还需要进行额外的时序例外约束,不能简单使用 set_clock_groups 约束异步时钟组,还需要考虑外部的读写逻辑的约束。

Xilinx建议这里设置set_max_delay来约束跨时钟域路径,约束的原则是:最大路径延时等于或者略小于目的时钟的一个周期。

写逻辑从cell1到cell2的约束中,cell2的驱动时钟周期为5,如下所示,读逻辑约束进行相应约束。

多bit中,强烈推荐使用异步FIFO的IP来实现,我在实际工程中使用多次,简单方便。

set_property ASYNC_REG TRUE [get_cells [list rst_reg_0 rst_reg_1]]

审核编辑:刘清

-

从处理单bit跨时钟域信号同步问题来入手2023-06-27 2762

-

CDC跨时钟域处理及相应的时序约束2023-06-21 3394

-

FPGA跨时钟域处理方法(二)2023-05-25 1873

-

单bit信号的跨时钟域传输可以使用两级同步但后果呢?2023-05-10 1696

-

单位宽信号如何跨时钟域2023-04-13 2315

-

Verilog电路设计之单bit跨时钟域同步和异步FIFO2023-01-01 2002

-

关于跨时钟域信号的处理方法2022-10-09 8555

-

介绍3种方法跨时钟域处理方法2021-09-18 23590

-

如何处理好FPGA设计中跨时钟域间的数据2021-07-29 1720

-

CDC单bit脉冲跨时钟域的处理介绍2021-03-22 4477

-

三种跨时钟域处理的方法2021-01-08 2344

-

如何处理好FPGA设计中跨时钟域问题?2020-09-22 2398

-

cdc路径方案帮您解决跨时钟域难题2017-11-30 8840

全部0条评论

快来发表一下你的评论吧 !